当模块突加载时,输入功率来不及变化仍然是原来的功率,因而输入功率小于输出功率,从而使得PFC母线电压下跌。根据能量守恒可知,

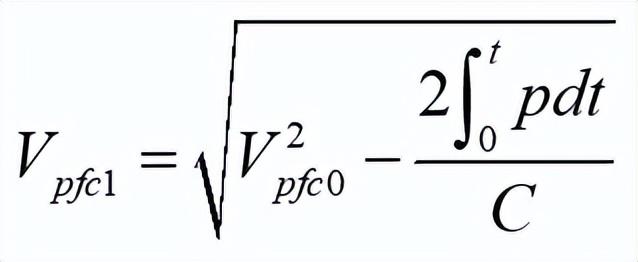

式(1)

式中,Vpfc1和Vpfc0分别为PFC母线电压在突加载下跌过程的终值和初始值,p等于突加载下跌过程中输出功率减输入功率(在此过程中p是不断变化的),t为突加载下跌的时间(也即从动态开始到Ipfc达到输入功率等于输出功率时的值),C为母线电容。

从式(1)可以看出,Vpfc下跌值在Vpfc0一定时,取决于电容C、p和下跌时间t,要想减小Vpfc的下跌值可以增大电容C,或者减小功率p,或者减小下跌时间t。但是,在主电路确定以后电容C是一定的;功率p主要取决于突加载增加的功率,这又取决于实际的应用情况,在设计时需要考虑最恶劣的情况(即从空载到满载),这在确定模块的功率后一般也是一定的;下跌时间t主要取决于环路控制,是可以通过控制策略来减小的。所以,在突加载情况下,对于改善PFC动态来说,动态控制策略实际上就是想办法加快环路响应,减小下跌时间t。

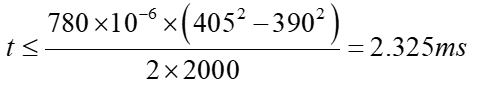

举个例子,设Vpfc0=405V,电容C=780us,突然从空载加到满载2000W,那么假如电压下跌15V到390V的话,时间t应该:

式(2)

PFC控制环路采用的是电压外环和电流内环组成的双闭环结构,如图1所示,下跌时间t可以看成有以下4部分组成:

t = t1 + t2 + t3 + t4 (3)

其中:

t1——从突加载到DSP第一次电压环计算的时间,可能从0到DSP电压环计算周期时间不等,如果电压环是16拍计算一次,那么最大就是177.8us(90kHz计算频率),如果每拍计算,最大就是11.11us。

t2——Vpfc的采样和滤波时间,电压环中有一个30Hz的电压滤波器,此滤波器的延时是t2的主要组成部分,由于采样频率高于计算频率,所以采样时间基本可以不考虑。

t3——表征电压环PI参数的时间,当Kp和Ki越大时,t3就越小。比如说,突加载后期望的电流环给定为Ipfcref,那么t3就是Vpfc下跌产生的电压偏差Err通过电压环PI参数累积,使得电流环给定达到Ipfcref的时间。

t4——电流环响应时间。

当然,上述时间的定义只是为了更清楚的分析和设计PFC控制策略,也可以从其他角度来看,实际上也可以将t1 + t2 + t3统称为电压环的响应时间。

从构成下跌时间t的几部分来看,t1取决于电压环的计算频率和动态的发生时刻,是不确定的,要减小t1需要提高电压环的计算频率,受限于DSP的时间资源提高计算频率比较困难,而且t1也较小(16拍最大为177.8us,每拍最大为11.11us),可减少的时间有限,所以设计PFC动态控制策略时可以忽略;t4电流环响应时间,一般电流环带宽为2~3kHz,大概估算应该小于200us,想进一步提高带宽也比较困难,而且t4本身也较小,再怎么提高带宽时间减少也很小,所以一般也不太考虑;剩下的t2和t3是下跌时间的主要部分,其中t2的30Hz滤波的延时就有十几ms,所以PFC动态控制策略主要就是基于减小t2和t3来设计的。

PFC动态控制新算法在源跳变或负载跳变时快速的将期望值赋给电流环给定来改善PFC动态特性,实际上也是通过减小t2和t3来加快电压环改善动态特性。

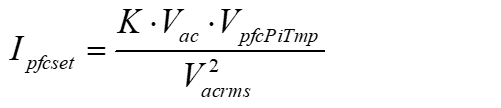

PFC电流环给定为:

式(4)

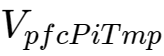

式中,

是电压环PI调节器输出。

源跳变控制实现

采用原来的动态控制方案时,在输入交流电压跳变时,

不能及时的更新,使得Ipfcset不能及时更新,从而造成输入功率和输出功率不平衡,使得Vpfc产生上冲或下跌。只有在Vpfc已上冲或下跌了18V后才进入动态处理程序,所以Vpfc会有较大的上冲或下跌。

新控制算法实时计算Vac有效值,快速的更新Ipfcset到期望值,从而减小Vpfc的波动。

负载跳变控制实现

采用原来的动态控制方案时,当发生负载跳变时,由于电压环很慢,不能及时更新

,导致功率不平衡,从而造成Vpfc的上冲或下跌。

采用新算法后,根据PFC输出功率迅速更新

到稳定值,减少功率不平衡的时间,从而减小Vpfc的上冲或下跌。

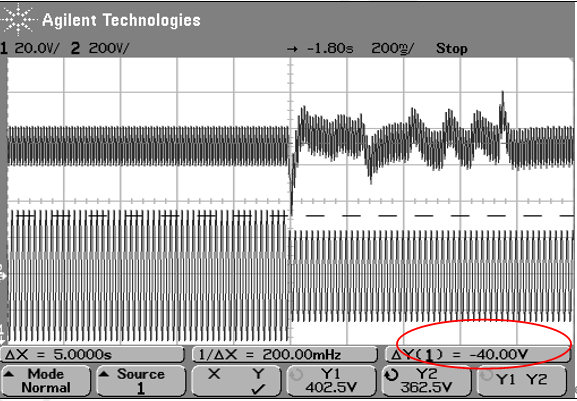

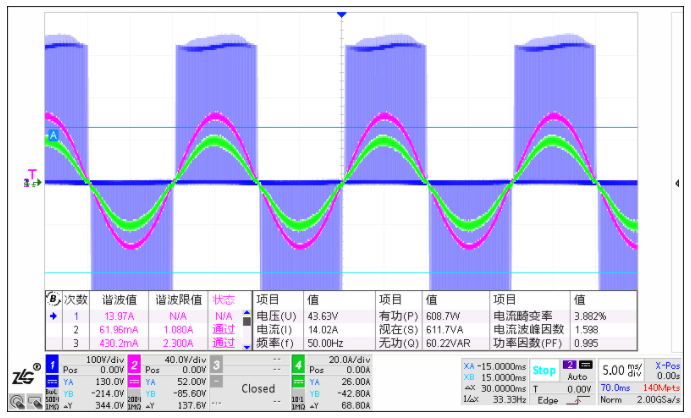

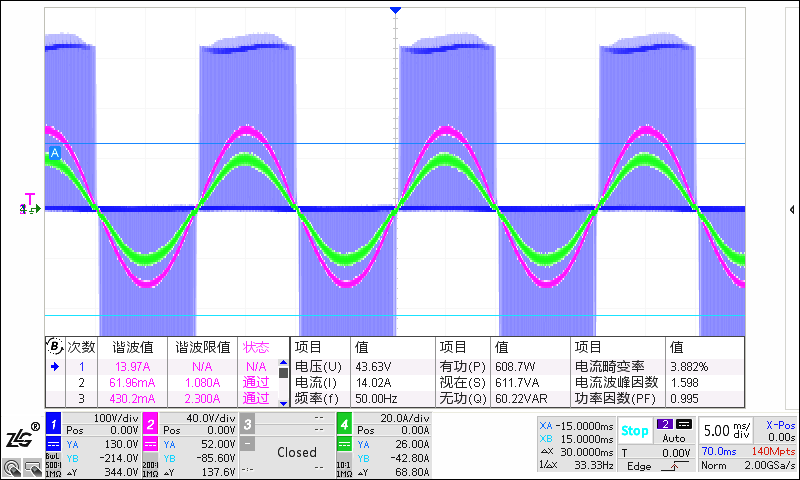

旧策略,输入电压180---260V跳变,60Hz,满载(37.5A),Vpfc和Vac

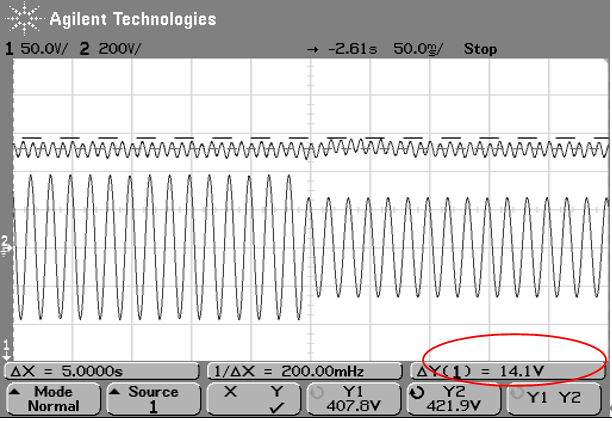

新策略,输入电压180---260V跳变,60Hz,满载(37.5A),Vpfc和Vac

-

dsp

+关注

关注

554文章

8066浏览量

351816 -

滤波器

+关注

关注

161文章

7919浏览量

179506 -

PFC

+关注

关注

47文章

994浏览量

106675 -

输入功率

+关注

关注

0文章

11浏览量

7827 -

母线

+关注

关注

0文章

175浏览量

16737

发布评论请先 登录

相关推荐

数字控制提高了无桥接PFC性能

在数字控制电源中高效调节动态电压的案例

数字控制真的会取代模拟控制,而成为PFC中的主流控制方式吗?

用数字控制提高无桥PFC性能

基于TMS320LF2407的全数字PFC控制技术

单相Boost功率因数校正器的PFC数字控制策略

使用C2000 MCU的数字控制无桥式功率因数校正(BL PFC)

数字控制PFC动态策略

数字控制PFC动态策略

评论