DS75的2线制时序规格不同于I2C。本申请说明详细说明了差异。SDA不是由DS75内部持有的。总线主控器的责任是保持SDA直到SCL的下降沿完成。

介绍

本应用说明详细说明了DS75通信时序与I2C规范之间的差异。在I2C下,SCL和SDA线被允许同时转换,因为SDA被从设备内部延迟至少300ns。DS75相对于SCL不延迟SDA信号,因此总线主控器必须将SDA保持在适当的逻辑状态,直到SCL完全转换到逻辑低,以防止START或STOP操作的错误生成。。

适当的时机

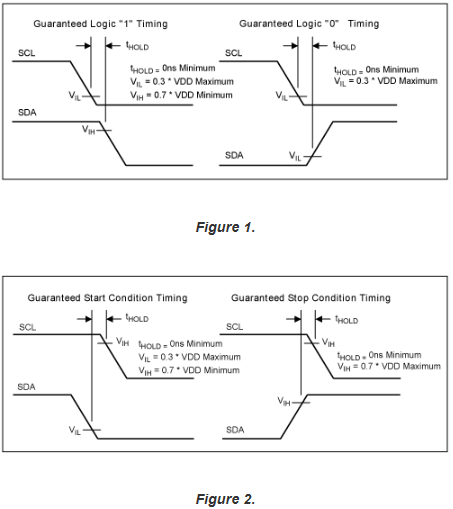

DS75的SDA线路相对于SCL没有内部延迟。由于这个原因,SDA逻辑电平必须保持在DS75外部,直到SCL在写入数据时转换到逻辑低;否则可以替代地识别开始或停止条件。在2线总线上写入逻辑“1”时,在SDA转换到低于保证逻辑高阈值VIH(0.7 x VDD最小值)之前,SCL必须达到保证逻辑低阈值VIL(0.3 x VDD最大值)。当写入逻辑“0”时,SCL必须在SDA转换到VIL之上之前达到VIL。生成START条件时,SDA必须在SCL转换到VIH以下之前达到VIL。生成STOP条件时,SDA必须在SCL转换到VIH以下之前达到VIH。VIL和VIH水平都在每个设备上进行了生产测试。这保证了在包括器件制造公差在内的整个电压和温度范围内使用该定时的正确操作。

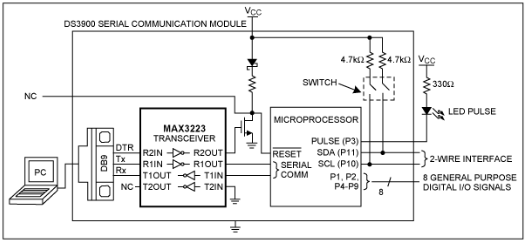

图1.

图2.

总结

DS75时序和I2C规格之间存在差异。相对于SCL,DS75不会在内部延迟SDA。因此,系统主机需要在SCL的下降沿期间保持SDA,以防止逻辑“1”被解释为START条件,以及逻辑“0”被解释为由STOP条件。

-

总线

+关注

关注

10文章

3065浏览量

91945 -

I2C

+关注

关注

28文章

1564浏览量

131887 -

Start

+关注

关注

0文章

73浏览量

13983

发布评论请先 登录

使用ADC3424EVM的2-wire模数转换,ADC3424需要配置吗?

DS75 pdf datasheet

DS1629 pdf datasheet (2-Wire D

MAX9621,pdf datasheet (2-wire Hall-effect sensors to low voltage microprocessors)

关于DS1624 2线通信SDA保持时间的说明

关于DS75 2线通信SDA保持时间的说明

Writing Parallel-Port 2-Wire S

如何使用I²C接口的DS2482 1-Wire主控

用于2-Wire总线应用的上升时间加速器电路

使用LabVIEW的2-Wire通信

如何使用PC并口与2-Wire设备通信

DS75 2-Wire通信SDA保持时间澄清

DS75 2-Wire通信SDA保持时间澄清

评论