Input-to-Reg 约束

设置 Input-to-Reg 时序路径的约束时,不仅需要创建时钟模型,还需要设置输入延时 (input delay)。 设置 input delay 时,需要假设输入 port 信号是与时钟相关联的,且 port 信号是在时钟上升沿到来之后延迟了一小段时间到达的 port 端。 这一小段延迟时间称为 input delay。

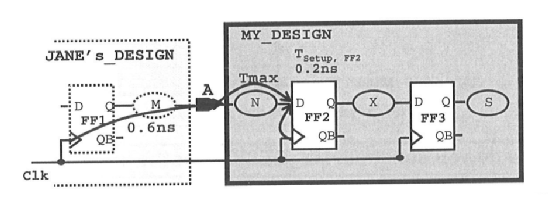

假设上图中 port A 信号是在时钟到来之后的 0.6ns 达到,时钟周期为 2ns,clock uncertainty 为 0.3ns,建立时间为 0.2ns,则约束语句为:

create_clock -period 2 [get_ports Clk]

set_clock_uncertainty -setup 0.3 [get_clocks Clk]

set_input_delay -max 0.6 -clock Clk [get_ports A]

则 port A 到寄存器 FF2 的 D 端的 N 路径延时为:

Tmax = 2-0.3-0.6-0.2 = 0.9ns

只要 port A 到寄存器 FF2 的 D 端的延时小于 0.9ns,时序就能满足要求。

当所有输入端口延迟相同时,可利用以下语句进行时序约束:

set_input_delay -max 0.6 -clock Clk \\

[remove_from_collection [all_inputs] [get_ports Clk]]

当仅有一两个信号的输入延迟不同时,可以使用分别设置的方法,也可以使用覆盖设置的方法:

# 首先设置所有 input delay 为 0.6ns

set_input_delay -max 0.6 -clock Clk [all_inputs]

# port A 的输入延时设为 0.7ns,则上一句 A 的输入延时属性会被覆盖

set_input_delay -max 0.7 -clock Clk [get_ports A]

# 去除掉 clock 端的输入延时设置

remove_input_delay [get_ports Clk]

Reg-to-Output 约束

设置 Reg-to-Output 时序路径的约束时,也需要设置输出延时 (output delay)。

设置 output delay 时,也需要假设输出 port 信号是与时钟相关联的,且 port 端信号在延迟了一小段时间后可以到达可能存在的 ”下一级寄存器的 D 端“,并被时钟捕获。 这一小段延迟时间称为 output delay。

假设上图中 port B 信号输出后到达下一级的 output delay (Tt + Tsetup) 为 0.8ns,时钟周期为 2ns,clock uncertainty 为 0.3ns,则约束语句描述为:

create_clock -period 2 [get_ports Clk]

set_clock_uncertainty -setup 0.3 [get_clocks Clk]

set_output_delay -max 0.8 -clock Clk [get_ports B]

寄存器 FF3 的 clock 端到 port B 的最大延时为:

Tmax = 2-0.3-0.8 = 0.9ns

只要寄存器 FF3 的 clock 端到 port B 的延时小于 0.9ns,时序就能满足要求。

当所有输出端口延迟相同时,也可以同时对所有输出端进行 output delay 的设置。 当仅有一两个信号的输出延时不同时,可以使用分别设置的方法,也可以使用覆盖设置的方法。

Input-to-Output 约束

当输入端和输出端之间只存在组合逻辑时,就需要在 DC 中创建虚拟时钟来约束时序。 虚拟时钟没有连接到设计中的任何端口,只为方便分析 input delay 与 output delay。

例如某个设计示意图如下所示,估算虚拟时钟的频率为 2ns, uncertainty 为 0.3ns,则 Input-to-Output 的约束语句描述如下:

# 创建虚拟时钟时无需指定 clock 源,且不可省略 -name 选项

create_clock -name VCLK -period 2

set_clock_uncertainty -setup 0.3 [get_clocks VCLK]

set_input_delay -max 0.4 -clock VCLK [get_ports A]

set_output_delay -max 0.3 -clock VCLK [get_ports B]

此时 port A 与 port B 之间的组合逻辑最大延时要求为:

Tcomb = 2-0.3-0.4-0.3 = 1ns

Latency/Uncertainty 对 Input/Output Delay 的影响

上一个寄存器的时钟端到下一个寄存器的数据端的路径,可以称为数据路径 (data path)。 而时钟周期的传输可以称为时钟路径 (clock path)。

clock 建模时,如果设置了 Uncertainty/Latency,则会对 data path 和 clock path 产生影响,从而对 Input/Output Delay 的相关时序可能也会产生影响。

某一设计示意图及时序约束语句描述如下,图中也简单计算了数据到来时刻、数据捕获时刻、时钟到来时刻等信息。

首先分析 Input-to-Reg path:

考虑 clock latency,时钟延时为 source latency 与 network latency 的总和:

clock latency = 0.3+0.12 = 0.42 ns

FF2 时钟端的 clock launch 包含了 clock latency 和 uncertainty,到达时刻为:

clk launch = 2+0.42-2 = 2.22ns

数据到达 port 端口的时间为 clock latency 与 input delay 的总和:

input arrival = 0.42+0.6 = 1.02ns

所以,内部路径 N 的最大延时为:

Npath_Tmax = clk launch - input arrival = 2.22-1.02 = 1.2ns

不考虑 clock latency,则内部路径 N 的最大延时为:

Npath_Tmax = 2 - 0.2 - 0.6 = 1.2ns

可见,clock latency 对 Input-to-Reg 路径时序没有影响,clock uncertainty 有影响。

分析 Reg-to-Output 路径:

考虑 clock latency,则 clock launch 时间不变,仍然为 2.22ns。

clock latency 与内部路径 S 的延时时间和为:

clock latency + Spath_Tmax

= clock launch - output_delay

=2.22 - 0.8 = 1.42ns

内部路径 S 的最大延时为:

Spath_Tmax = 1.42 -0.42 = 1ns

不考虑 clock latency,则内部路径 S 的最大延时为:

Spath_Tmax = 2 - 0.2 - 0.8 = 1ns

可见,clock latency 对 Reg-to-Output 路径时序没有影响,clock uncertainty 有影响。

小结

clock latency 同时作用于 data_path 与 clock path,所以对 Input-to-Reg 与 Reg-to-Output path 的时序分析不会产生影响。

clock Uncertainty 只作用于clock path,所以对 Input-to-Reg 与 Reg-to-Output path 的时序分析会产生影响。

时序预算 (Timing Budget)

因为应用场景的差异,更多时候 input/output delay 的具体值是无法精确得到的,这就需要对相关的延时值进行估计,并应用到约束设置中,即为时间预算 (timing budget)。

Timing Budget 的方式主要有两种:按时钟百分比估算和按寄存器输出估算。

按时钟百分比估算

一般建议使用时钟周期的 40% 时长来约束 port 端到寄存器 D 的延时 (上图中 MY_BLOCK 的 N path) ,即 input delay 可以设置为时钟周期的 60% 时长。 output delay 同理。

假如上一级 Q 端到输出端的延时 (上图中 X_BLOCK 的 S path) 也取 40%,那么 Input-to-Reg path 将有 20% 的裕量,裕量中包括 FF1 的 CQ 延时 (FF1 时钟端到输出端) 和 FF2 的建立时间。 所以,实际设置 60% 的 input delay 是有些偏大的。

假设上述设计中,时钟周期为 10ns,则 timing bugdet 方案可以描述如下:

create_clock -period 10 [get_ports CLK]

set_input_delay -max 6 -clock CLK \\

[remove_from_collection [all_inputs] [get_ports CLK]]

set_output_delay -max 6 -clock CLK [all_outputs]

按寄存器输出估算

假设所有的输出 port 都是由寄存器驱动的 (见上图中的 X_BLOCK 和 Y_BLOCK 设计),那么 input delay 可以由上一级寄存器的延时特性估算,output delay 可以由下一级寄存器的延时特性估算。

例如通过查找 library 得到触发器的 CQ 延时 (时钟端到输出端) 最大为 1.5ns,最小为 0.2ns,那么 input/output delay 的约束语句可以描述如下:

set C2Q_MAX 1.5

set C2Q_MIN 0.2

set PERIOD 10

create_clock -period $PERIOD [get_ports CLK]

set_input_delay -max $C2Q_MAX -clock CLK \\

[remove_from_collection [all_inputs] [get_ports CLK]]

set_output_delay -max [expr 10-$C2Q_MIN] -clock CLK [all_outputs]

-

寄存器

+关注

关注

31文章

5336浏览量

120230 -

时钟

+关注

关注

10文章

1733浏览量

131446 -

约束

+关注

关注

0文章

82浏览量

12728 -

时序约束

+关注

关注

1文章

115浏览量

13416 -

时序路径

+关注

关注

0文章

12浏览量

1397

发布评论请先 登录

相关推荐

VIVADO时序约束及STA基础

FPGA时序约束的基础知识

FPGA主时钟约束详解 Vivado添加时序约束方法

时序约束的相关知识(二)

时序约束的相关知识(二)

评论