CSP封装及演进

芯片封装是半导体产业中的一个重要环节,它是芯片与外界信号互连的通道,同时对裸芯片起到固定、密封、散热、保护等多种功能。

CSP封装(Chip Scale Package)指芯片级封装,其封装尺寸和芯片核心尺寸基本相同,一般芯片面积与封装面积的比例约在1:1.2以内。CSP封装广泛应用于手机等消费电子的AP处理器,以及存储器芯片、射频模组等。

这些芯片或模组逐步向多功能低功耗演进,同时尺寸向轻、薄、短、小方向发展,要求封装IO密度和高速高频性能提升的同时,依然保持轻薄的特性。导致CSP封装结构,芯片组装方式从WB打线,向FC倒装芯片或混装方式演进;单芯片封装也逐步向多芯片,甚至堆叠方式演进。按照组装方式,业界常把CSP封装分成WBCSP和FCCSP两大类。

CSP封装分类

CSP基板的技术趋势

CSP基板做为CSP封装的重要载体,承载着信号互连、机械支撑、以及底部散热的功能。

对应前文所述的CSP封装主流应用领域,CSP基板有两个主流演进方向。其中存储器和应用处理器,为支持更多的IO接口同时缩小封装尺寸,FCCSP基板需要持续减薄同时增加线路密度,这样需求更薄的基板和更精细的线路制程。射频模组,为获取更好的信号和集成性能,基板层数持续提升,同时高频材料的应用越来越广泛。

CSP基板演进方向

CSP基板关键工艺挑战

概括起来,CSP基板有四大关键工艺挑战:超薄、精细线路、多层数,同时需要自动化生产来保障其质量稳定性。除此之外,微孔、高频高速高稳定的板材、多种表面处理、阻焊,也是CSP基板的关键技术。

CSP基板关键技术

· 精细线路工艺

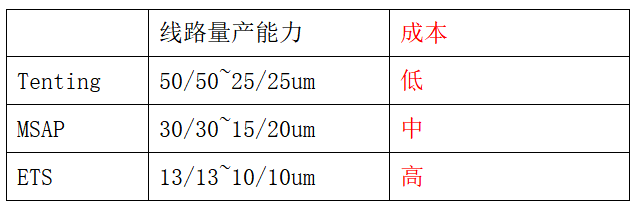

CSP基板精细线路的实现路径,主要包括Tenting-减成法、MSAP-改良半加成法、ETS-埋线路三种制程。这三种制程的可实现的线路精细度不同,同时由于复杂度不同带来的成本不同。其中,ETS属于Coreless无芯基板制程,但制作的线路最精细。

兴森同时具备这三种工艺能力,以匹配不同客户从L/S 50/50~10/10μm各类产品需求。引进高解析度全自动LDI曝光机、垂直非接触式MSAP显影线等先进设备,ETS最小线宽/线距可做到10/10um。

· 超薄板

超薄板是存储芯片、可穿戴设备的重要需求。兴森科技具备最薄芯板0.035mm、无芯基板总厚70-90μm的加工能力。这需要工厂全线设备在设计上都具备对应能力。对于无芯基板,如图4,制造过程中会使用一种叫Detach Core的支撑层材料。分离这层材料时,兴森采用了自动分离机,分离速度快,精度高,可极大降低传统手动分离导致的基板破损,折痕,翘曲等问题。

· 多层

CSP基板2-4层就能满足大多数要求,但是射频模块等产品高频信号、高集成,对基板层数也有更高要求,这在芯板很薄的前提下,挑战很大。兴森拥有成熟的层间对位和涨缩控制系统,高度自动化的叠合-压合流程设备,可实现最高10层的CSP封装基板量产。

· 多种表面处理

应对不同的应用场景,有不同的表面处理要求,为此,兴森配备了完整的五种表面处理线体。

· 自动化

上述薄板精细线路和多层都是CSP封装基板的关键技术挑战,唯有高度自动化的产线,才能实现稳定高效的连续生产,保障产品高品质和快速交付。

审核编辑:刘清

-

处理器

+关注

关注

68文章

19125浏览量

228881 -

集成电路

+关注

关注

5379文章

11336浏览量

360528 -

存储器

+关注

关注

38文章

7443浏览量

163541 -

CSP

+关注

关注

0文章

124浏览量

28027 -

芯片封装

+关注

关注

11文章

475浏览量

30540

原文标题:硬干货!深度剖析全球先进的集成电路CSP封装基板

文章出处:【微信号:China_FASTPRINT,微信公众号:兴森科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

深度剖析全球先进的集成电路CSP封装基板

深度剖析全球先进的集成电路CSP封装基板

评论