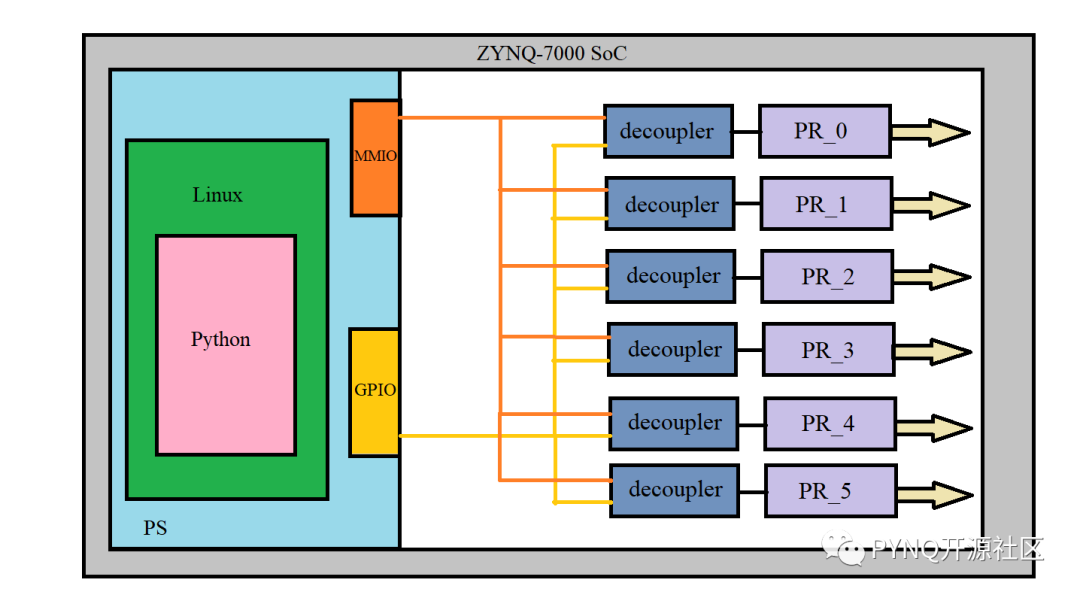

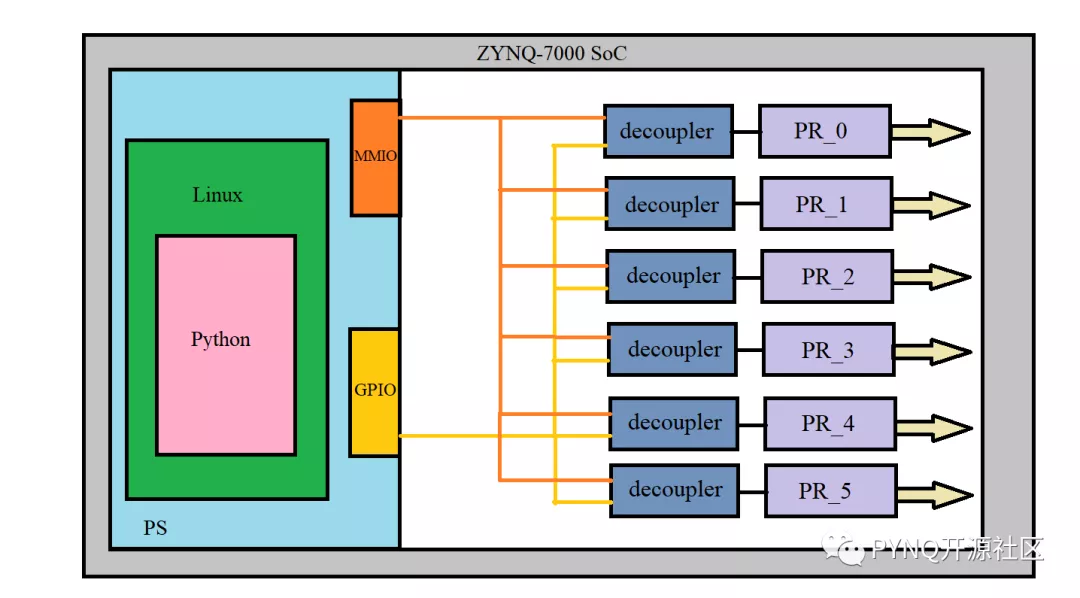

PYNQ-PRIO是一个介绍如何利用FPGA部分可重配置特性和PYNQ框架提供的方便的API,对FPGA分时复用,提高FPGA灵活性的项目。可重配置是指在一个FPGA工程中,划分了静态逻辑部分和动态逻辑部分,静态逻辑部分是指在运行过程中逻辑不变的部分,动态逻辑部分是指在运行过程中可以根据需要下载特定比特流文件实现不同逻辑的部分,在工作时,修改某一动态逻辑部分不会对静态逻辑部分和其他动态逻辑部分造成影响,实现了FPGA的功能上的分时复用。

上图为工程项目示意图。通过软硬件划分,在PS端中负责Linux和通信,PL端例化了6个PR(Partitial Reconfiguration)块。每个块中有GPIO、uart和IIC等几种不同的RM(Reconfiguration Module),它们通过各自的partitial bitstream下载。动态逻辑部分和静态逻辑部分使用分离器保证它们互不影响,并在动态逻辑部分下载完成后对下载好的部分进行复位。

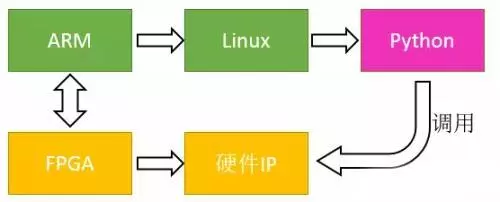

此项目中在PYNQ框架下有两种驱动这些IP的方式:一是直接使用PYNQ提供的API操作overlay里面的IP,二是将这些IP通过DTS(Device Tress Source)注册到linux sysfs中,然后调用linux提供的驱动。

快速开始

运行下面这条命令即可快速安装:

sudo -H pip3 install git+https://github.com/Siudya/PYNQ-PRIO.git

项目演示

1 、 使用pynq API的方法:

打开~/prio/uart.ipynb,前面一段代码是UART的驱动程序和必要的功能代码,不是本文重点请读者自己研读。

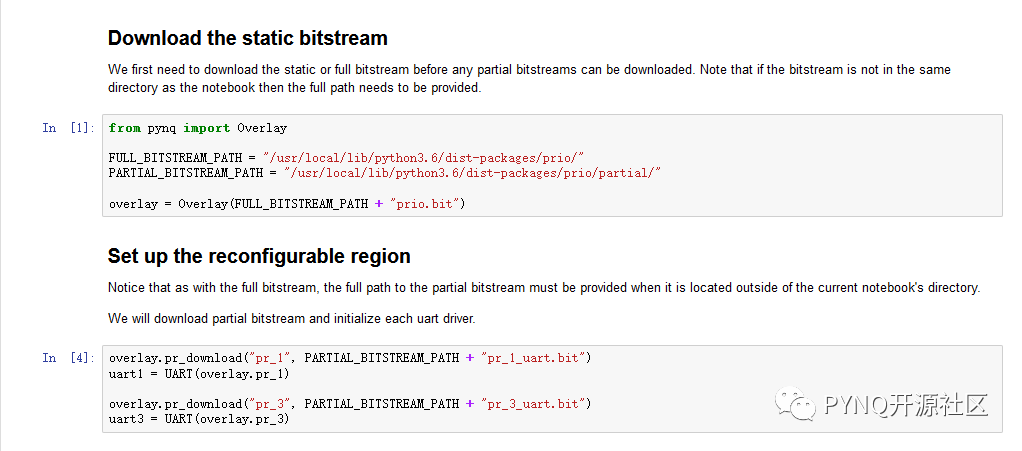

接下来就是下载bit文件。首先下载静态逻辑bit文件,静态bit文件中的PR部分是默认的RM。然后下载PR的bit文件。注意,下载一个PR的bit文件后要立刻例化一个驱动实例,这是因为每个PR的bit文件所对应的hwh文件中其他PR部分都使用默认RM,但是下载一个PR的bit文件并不会影响其他PR和静态逻辑。

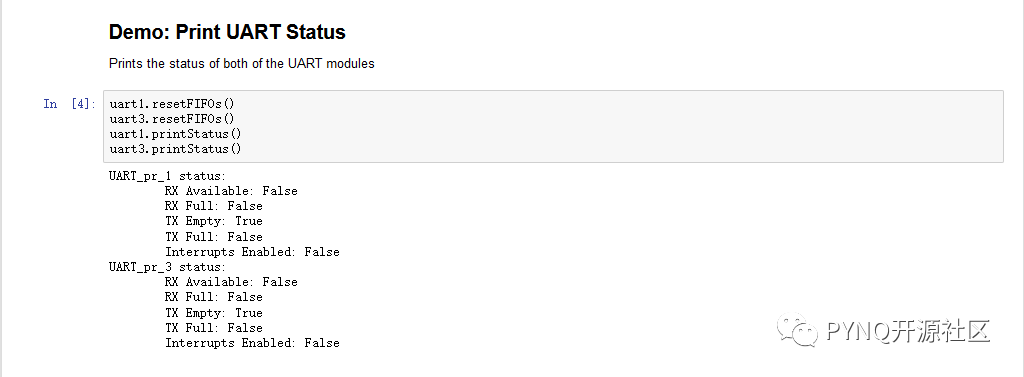

然后可以测试一下两个UART的状态,在这里我们并没有开启中断。

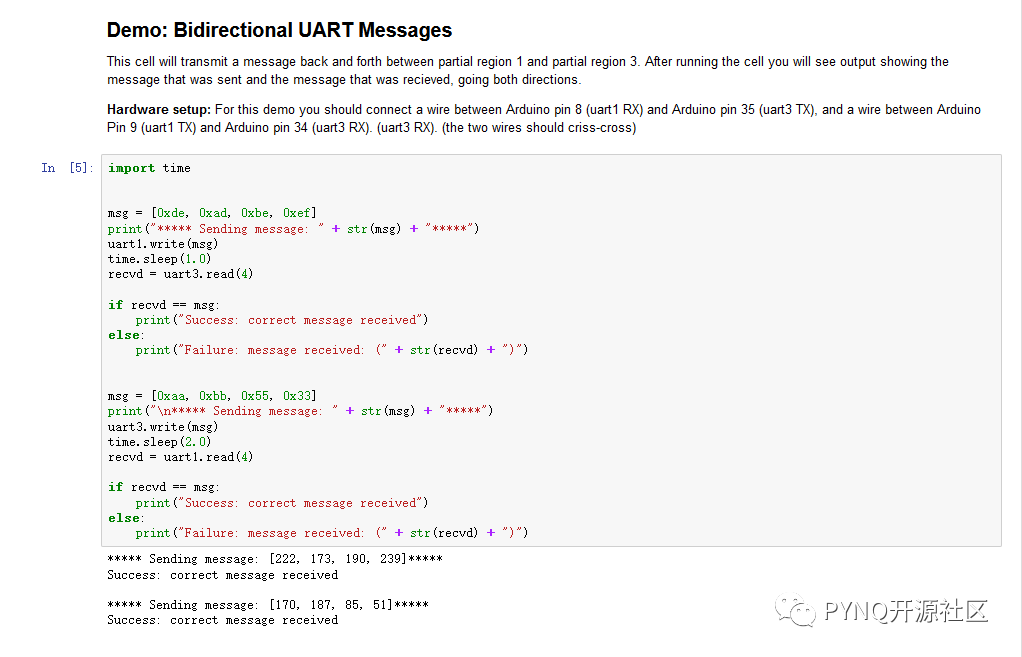

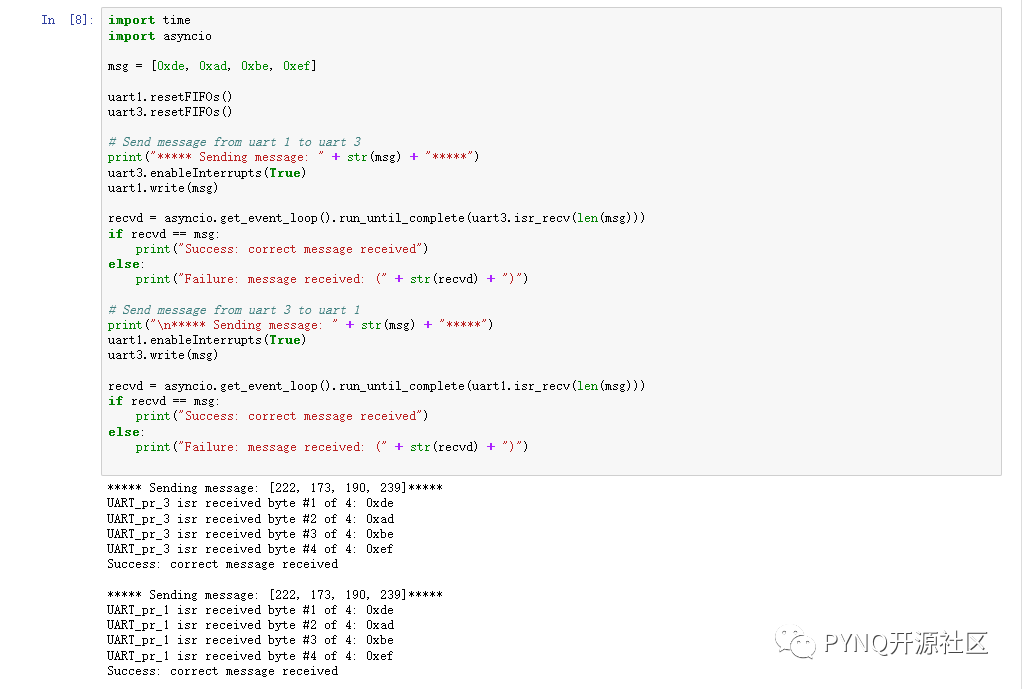

下一步我们测试两个串口的收发。用杜邦线将uart1的TX(Arduino的Pin 9)和uart3的RX(Arduino的Pin 34),uart1的RX(Arduino的Pin 8)和uart3的TX(Arduino的Pin 35)连接起来,运行这段代码,可以看到信息被正确地收发了。

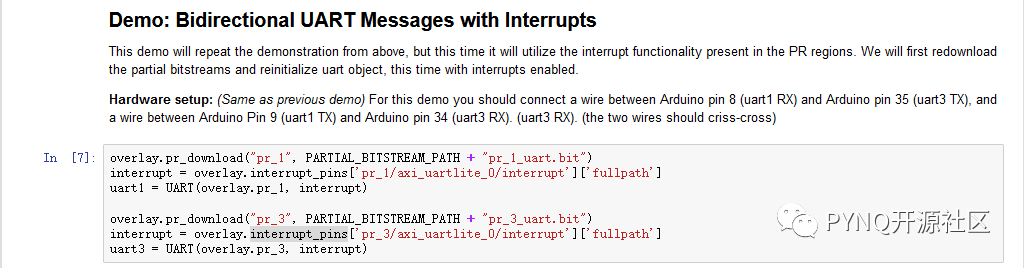

接下来我们试试含中断的收发。首先仍然是例化实例,不过在这里我们要从overlay.interrupts_pins中读取每个uart的中断引脚,然后初始化uart实例。

利用asyncio库和中断,我们可以实现异步收发。

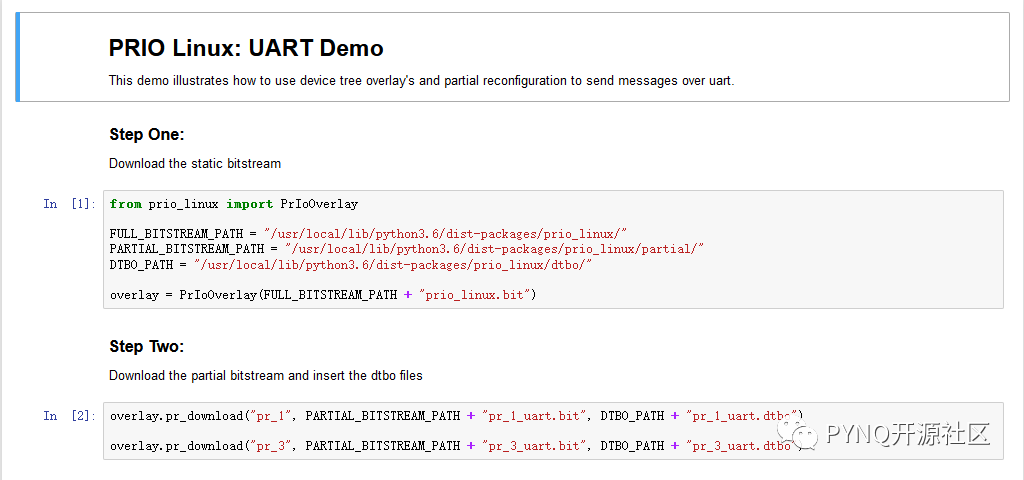

2 、使用linux sysfs API的方法:

打开~/prio_linux/uart_linux.pynb

首先和上面使用pynq的API的方法一样,首先下载静态逻辑的bit文件,再下载PR的bit文件。但是不同的是同时注册了对应的dtbo到linux系统中。dtbo由dtso编译而来,dtso是描述设备树的文件,关于它的编写参阅以下链接:

https://www.raspberrypi.org/documentation/configuration/device-tree.md

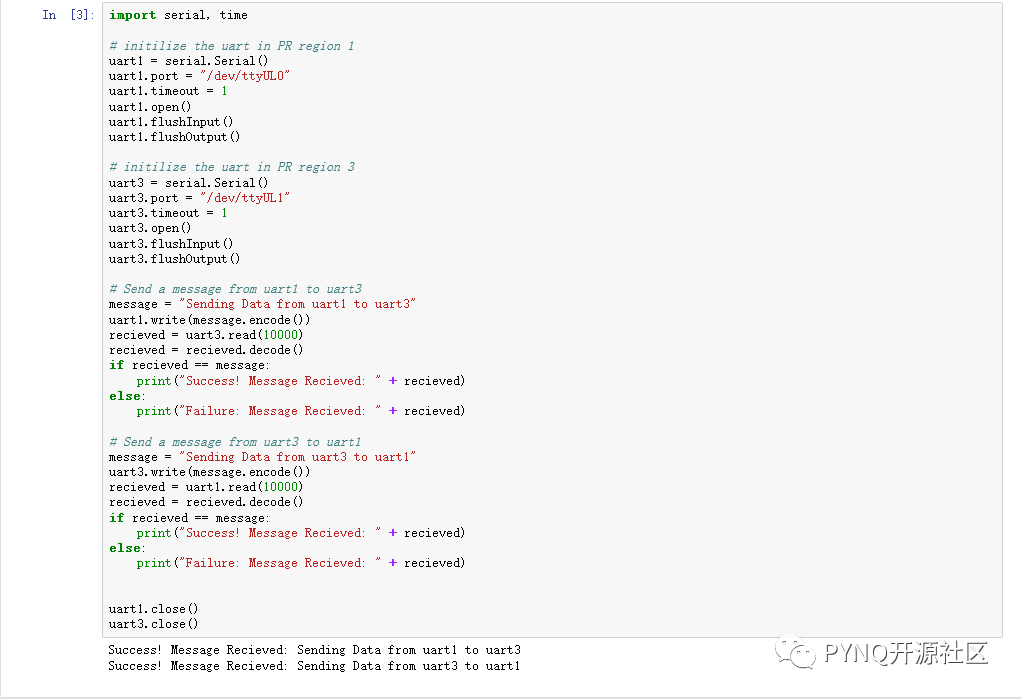

注册完成后可以直接在/dev下看到这两个uart模块。然后可以使用linux自带的serial库调用它们。

这个项目中我们利用了FPGA的部分可重构的特性,实现了运行中的部分逻辑的动态转换。另外我们可以看到利用PYNQ提供的API,可以轻松注册设备到Linux系统,方便了其他程序对我们自定义IP的使用。

审核编辑 :李倩

-

FPGA

+关注

关注

1625文章

21620浏览量

601172 -

API

+关注

关注

2文章

1471浏览量

61742 -

PYNQ

+关注

关注

3文章

61浏览量

2882

原文标题:PYNQ经典项目分享| 可重配置IO

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

赛灵思发布ISE12.2强化部分可重配置FPGA技术

如何利用FPGA部分可重配置特性实现PYNQ-PRIO经典案例

PYNQ项目——Pynq开发板启动实验

总线可重配置的多处理器架构

可重配置系统中的联合负载控制及其终端选择算法

可重配置PLL使用手册

软件无线电平台可重配置接口的实现

FPGA的全局动态可重配置技术

基于SRAM的可重配置电路

赛灵思可重配置加速堆栈方案,旨在快速开发和部署加速平台

基于SRAM的可重配置电路PLD

PYNQ经典项目分享:可重配置IO

PYNQ经典项目分享:可重配置IO

评论