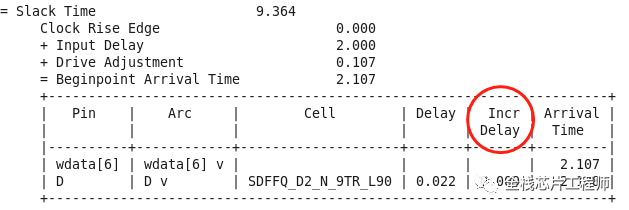

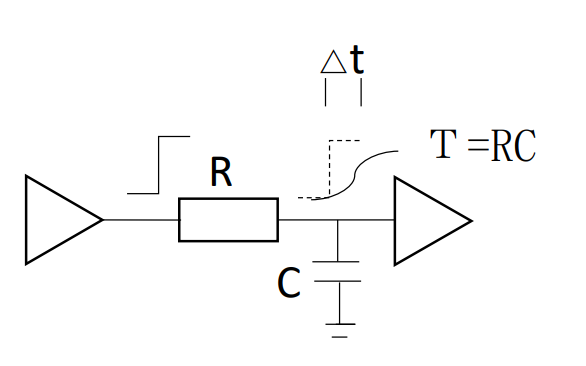

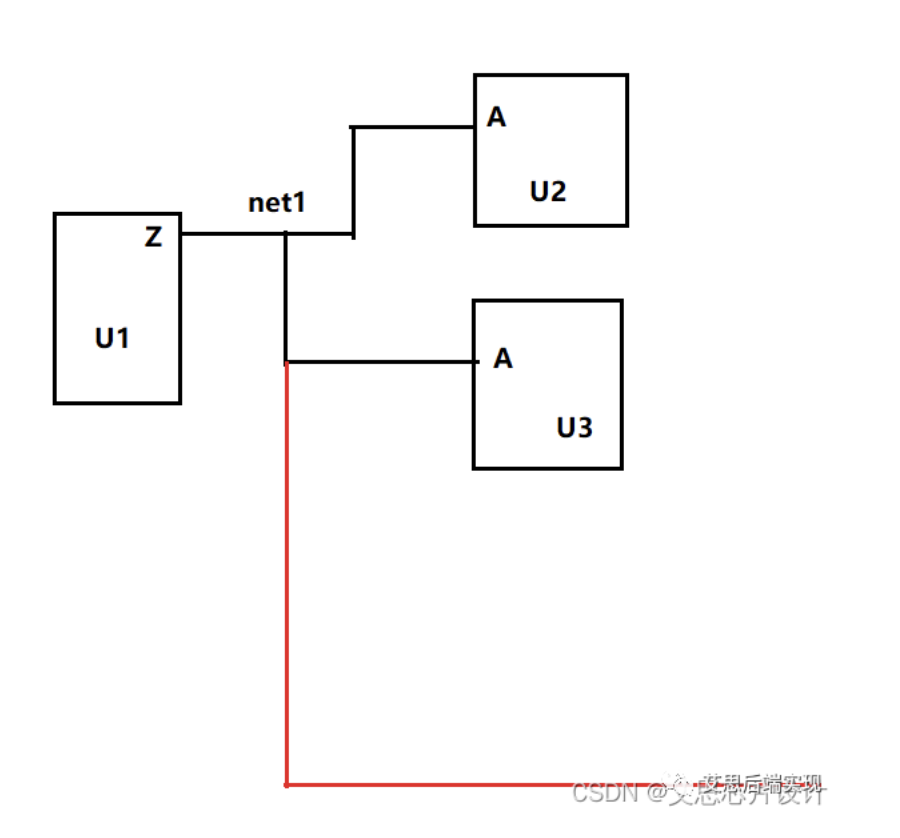

innovus的incredible delay是什么?如下图:

首先,Incr Delay不是incredible delay,而是increment delay增量延时的缩写。Incr Delay是由于SI信号完整性(比如cross talk、电磁等)造成的增量延时,也称为噪声延迟(incr delay)。

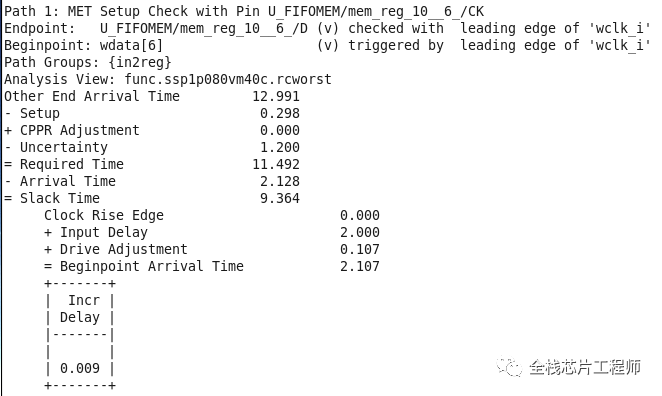

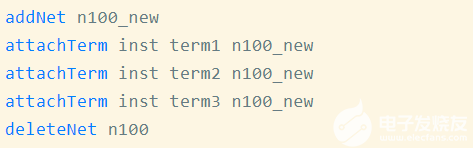

我们可以通过report_timing -format incr_delay报出来Incr Delay:

比如: report_timing -format incr_delay -from U_FIFOMEM/mem_reg_10__6_/D

但是这样报告只会打印出一个孤零零的incr delay数据:

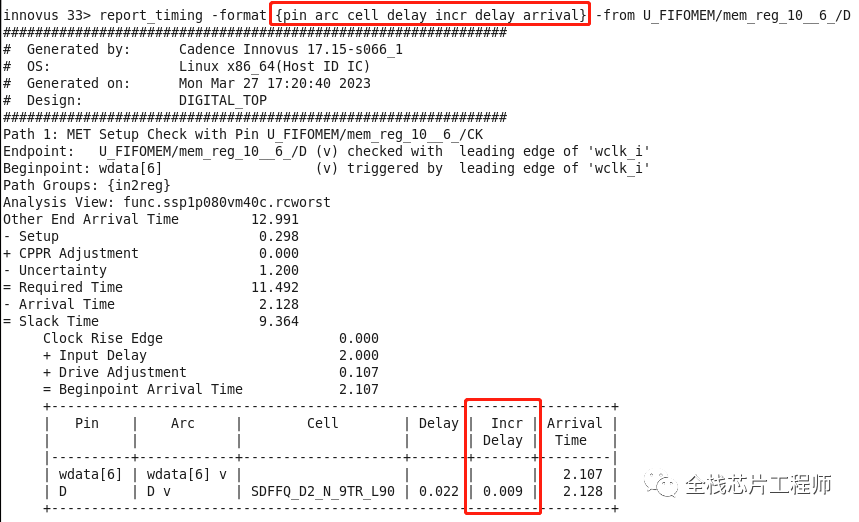

我们需要给-format再加上{pin arc cell delay incr_delay arrival}等信息:

report_timing-format{pinarccelldelayincr_delayarrival}-fromU_FIFOMEM/mem_reg_10__6_/D

报告的timing信息如下,请思考个问题,为什么0.009ns的Incr Delay没有加到Arrivel Time?

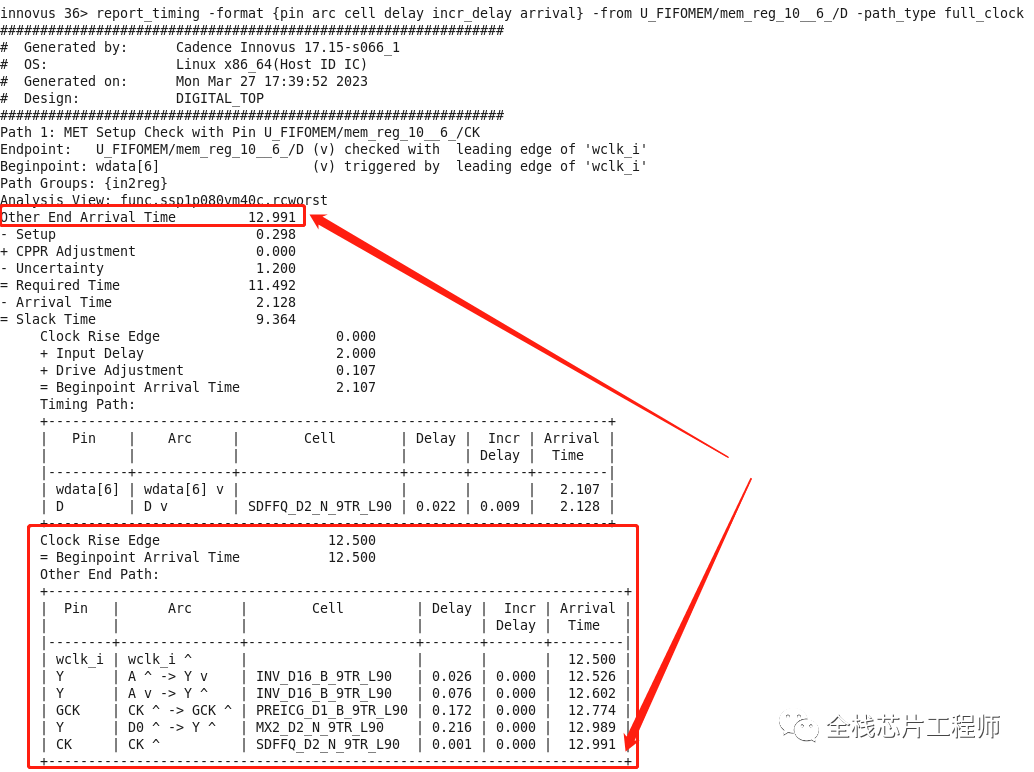

通常timing报告只有launchclock path +launch data path的具体path信息,为了展开看到capture clock path信息,我们可以给report_timing添加-path_type full_clock

report_timing -format {pin arc cell delay incr_delay arrival} -from U_FIFOMEM/mem_reg_10__6_/D -path_type full_clock

审核编辑:刘清

-

信号完整性

+关注

关注

68文章

1403浏览量

95454 -

PIN

+关注

关注

1文章

303浏览量

24279

原文标题:C家timing report之Incr Delay

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Cadence Innovus助力Realtek成功开发DTV SoC解决方案

How Delay Lines Work

延迟线比较-Delay Lines Comparison

芯片延迟Delay测试的学习课件PDF文件免费下载

stm32 delay文件总结

STM32上进行Delay延时的方法

【innovus】大小写重名的终极解决方法

innovus中悬垂线的理解和处理

innovus中的DanglingWire(悬垂线)的理解和处理

MCU项目innovus中get_db使用

innovus中的DanglingWire的理解和处理

innovus的incredible delay是什么?

innovus的incredible delay是什么?

评论