3.3.1 SIMT堆栈

SIMT堆栈用于在Warp前处理SIMT架构的分支分化的执行。一般采用后支配堆栈重收敛机制来减少分支分化对计算效率的负面影响。

SIMT 堆栈的条目代表不同的分化级别,每个条目存储新分支的目标 PC、后继的直接主要再收敛 PC 和分布到该分支的线程的活动掩码。在每个新的分化分支,一个新条目被推到栈顶;而当 Warp 到达其再收敛点时,栈顶条目则被弹出。每个 Warp 的 SIMT 堆栈在该 Warp 的每个指令发出后更新。

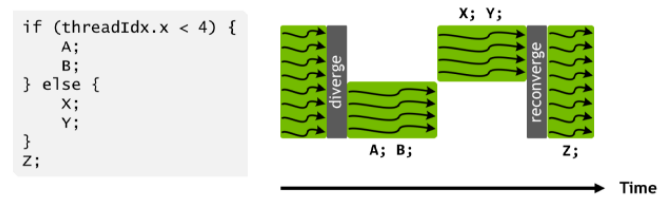

线程束分化

从功能角度来看,虽然SIMT架构下每个线程独立执行,但在实际的计算过程中会遇到一些分支的处理,即有些线程执行一个分支,而另外的线程则执行其他分支。如果在同一个Warp内不同的线程执行不同的分支,就会造成线程束分化,导致后继SIMD计算的效率降低。因此应尽量避免线程束的分化。

图 3-6 线程束分化与重聚合

SIMT堆栈功能

SIMT堆栈模块可有效改善线程束分化引起的GPGPU执行单元利用率下降的问题。

SIMT堆栈重点解决:

控制流嵌套问题(Nested Control Flow)

在控制流嵌套中,一个分支严重地依赖另一个分支,这极大影响了线程的独立性。

如何跳过计算过程(Skip Computation)

由于线程束分支的存在,导致同一个Warp内的有些线程并不必要执行某些计算指令。

- SIMT掩码

SIMT堆栈中使用了SIMT掩码(SIMT Mask)来处理线程束分化问题,以下例来说明掩码如何控制整个Warp的执行。

- SIMT 掩码引起的死锁问题

SIMT 掩码可以解决Warp内分支执行问题,通过串行执行完毕分支之后,线程在Reconverge Point(重合点)又重新聚合在一起以便最大提高其并行能力。

但对于一个程序来说,如果出现分支就表明每个分支的指令和处理是不一致的,容易使一些共享数据失去一致性。如果在同一个Warp内如果存在分支,则线程之间可能不能够交互或者进行数据交换,在一些实际算法中可能使用锁定(Lock)机制来进行数据交换。但掩码恰恰可能因为调度失衡,造成锁定一直不能被解除,造成死锁问题。

- GPGPU解决死锁的方法

图 3-8 V100 Warp调度对比图[2]

解决死锁的方法如下:

NVIDIA为V100 中Warp内的每个线程都分配了一个PC指针和堆栈,将PC指针的颗粒度细化到每一个线程中去,保障数据交换避免死锁。(图3-5)

为避免细粒度的PC指针和堆栈与GPU的SIMT执行模型产生冲突,硬件仍以Warp为单位来进行线程调度。

使用了Schedule Optimizer(调度优化器)硬件模块来决定哪些线程可以在一个Warp内进行调度,将相同的指令重新进行组织排布到一个Warp内,并执行SIMD模型,以保证利用效率最大化[2]。

3.3.2 线程束调度与记分牌

进行线程束(Warp)调度的目的是充分利用内存等待时间,选择合适的线程束来发射,提升执行单元计算效率。

在理想的计算情况下,GPU内每个Warp内的线程访问内存延迟都相等,那么可以通过在Warp内不断切换线程来隐藏内存访问的延迟。

GPU将不同类型的指令分配给不同的单元执行,LD/ST硬件单元用于读取内存,而执行计算指令可能使用INT32或者FP32硬件单元,且不同硬件单元的执行周期数一般不同。这样,在同一个Warp内,执行的内存读取指令可以采用异步执行的方式,即在读取内存等待期间,下一刻切换线程其他指令做并行执行,使得GPU可以一边进行读取内存指令,一边执行计算指令动作,通过循环调用(Round Robin)隐藏内存延迟问题,提升计算效率。

在理想状态下,可以通过这种循环调用方式完全隐藏掉内存延迟。但在实际计算流程中,内存延迟还取决于内核访问的内存位置,以及每个线程对内存的访问数量。

内存延迟问题影响着Warp调度,需要通过合理的Warp调度来隐藏掉内存延迟问题。

- 指令顺序调整的原因

在同一个Warp的单个线程中,调整发送到ALU将要执行的指令顺序,可以隐藏掉一部分内存延迟问题。例如读取指令和加法指令使用的是不同的硬件单元,在第一个时钟周期执行内存读取指令之后,下一个时钟周期不必等待读取内存指令,而是可以直接执行加法指令,从而实现一边计算一边读取,来提高整个运行效率。

但在实际情况中,后一个指令有可能是依赖于前一个指令的读取结果。要解决该问题就需要GPU提前对指令之间的依赖关系进行预测,解析出指令之间的独立性和依赖关系。

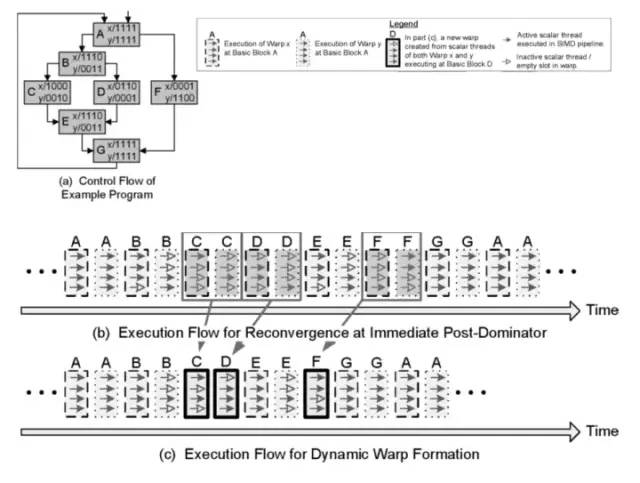

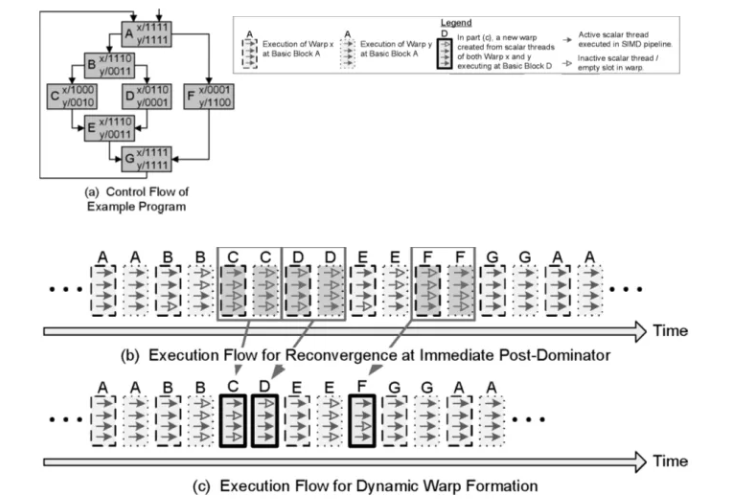

图 3-11动态线程束示例(来源:WILSON W. L. FUNG等)

- 记分牌与指令顺序调整的方法

GPU在这里参考了CPU设计,为了解析指令之间的独立性,采用顺序记分牌(In-Order Scoreboard)。

对于单线程束情况,

- 每个寄存器在记分牌中都对应一个标志位,用于表示该寄存器是否已被写入数据,如果置1则表示该寄存器已经被写入。

- 此时如果另外一个指令想要读或者写该寄存器,则会处于一直等待状态,一直到该寄存器的标志位被清零(表明之前写寄存器操作完成)。这样就可以阻止Read-After-Write和Write-After-Write的问题。

- 当顺序记分牌和顺序指令(In-Order Instruction)结合时,能避免Write-After-Read的问题。

图 3-11数据冲突与流水线结构相关

对于多线程束情况,将上述方法应用到GPU时,还需要解决两个问题:

- 由于有大量寄存器GPU,在每组寄存器中增加一个标志位将需要占用更多额外的寄存器。

- 在GPU中,一般会有很多个线程同时执行同一指令,一旦其执行的指令被打断,会有很多线程同时访问Scoreboard造成读取阻塞。

对于多线程束情况,可通过动态记分牌解决上面的两个问题:

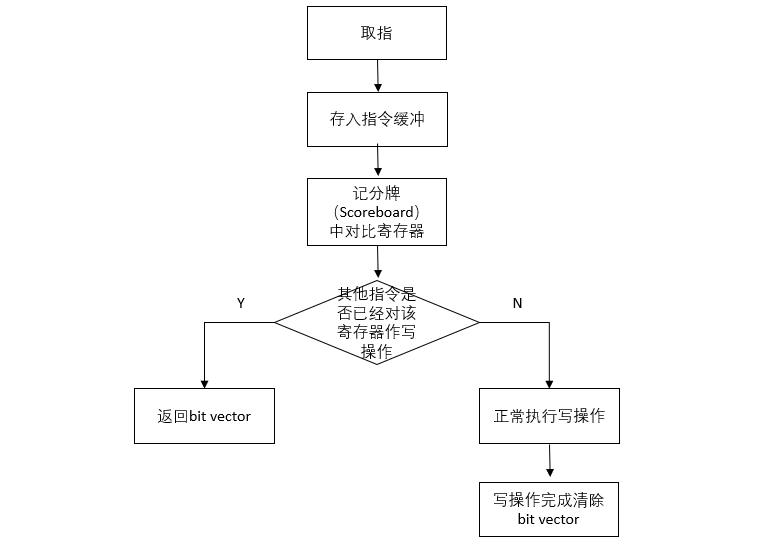

图 3-9 记分牌Entry流程

- 为每个Warp创建几个入口(Entry),每个入口与一个即将被写但操作尚未完成的寄存器相对应。记分牌在指令进入指令缓冲区(Instruction buffer,I-Buffer)和写操作完成结果存入Register File时能被访问(图3-6)

- 当一个指令从内存中读取出来放入到I-Buffer时,将该指令中的源寄存器和目的寄存器与Entry做比较,看是否有其他指令集已经对该寄存器在做写操作,如果有则返回一个bit Vector,与该寄存器一起写入到I-Buffer中。如果该指令集的写操作完成了,将会刷新I-Buffer中的该指令集寄存器的bit Vector,将bit Vector清除掉。

- 如果一个指令做写操作,并需要将该寄存器放入Entry中,但是此Entry已经满了,那么该指令将会一直等待,或者被丢弃过一定时钟周期后被重新获取再次查看Entry是否满[3]。

-

cpu

+关注

关注

68文章

10947浏览量

213899 -

gpu

+关注

关注

28文章

4830浏览量

129778 -

多处理器

+关注

关注

0文章

22浏览量

9005

发布评论请先 登录

相关推荐

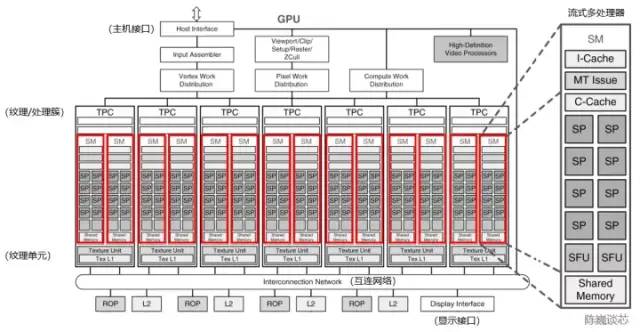

GPGPU的流式多处理器微架构原理解析

总线可重配置的多处理器架构

多处理器分组实时调度算法

基于NiosII的SOPC多处理器系统设计方法

面向异构多处理器设备的自适应命令解释系统

什么是同步多处理器

GPGPU流式多处理器架构及原理

GPGPU流式多处理器架构剖析(上)

GPGPU流式多处理器架构剖析(下)

GPGPU流式多处理器架构剖析(下)

评论