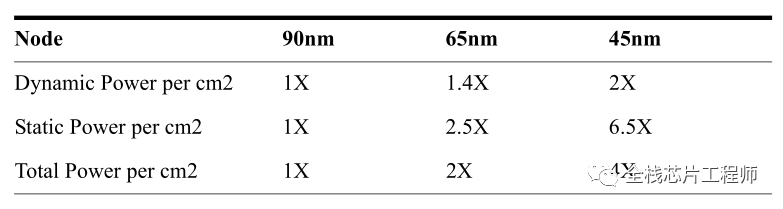

低功耗设计的重要性,从下图可窥一斑,随着工艺节点的推进演化,45nm工艺的动态功耗、静态功耗相比90nm工艺分别增加到了2倍、6.5倍。随着工艺节点演进到14nm、7nm等先进节点,Leakage Power的占比越来越高,Power gating的低功耗设计则十分关键。

功耗与IR分析密不可分,本文先讲芯片功耗类型,再讲Voltus IR分析。

降低功耗优势:

避免移动电子设备频繁充电; 避免芯片过热,延长芯片寿命; 避免高成本封装(陶封),若芯片功耗低,使用塑封即可; 避免芯片封装散热装置(水冷、加铜片)的成本;

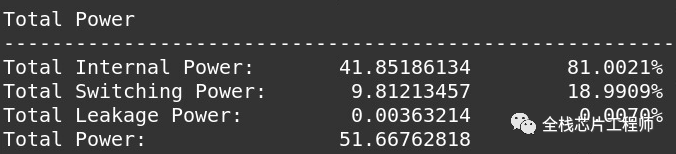

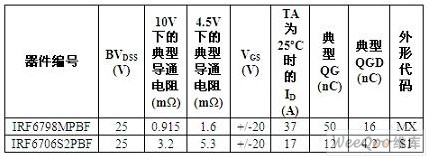

通常功耗分析完成后,工作目录下将得到power.rpt、power.db和*.ptiavg文件,其中*.ptiavg、power.db文件将用于IR分析,而power.rpt则会列出详细功耗组成部分,包括以下三个部分:短路功耗(Internal Power),翻转功耗(Switching power),漏电流功耗(Leakage Power)。

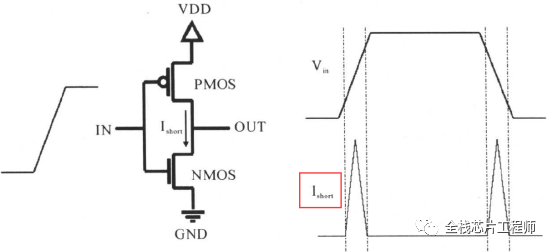

短路功耗(Internal Power)

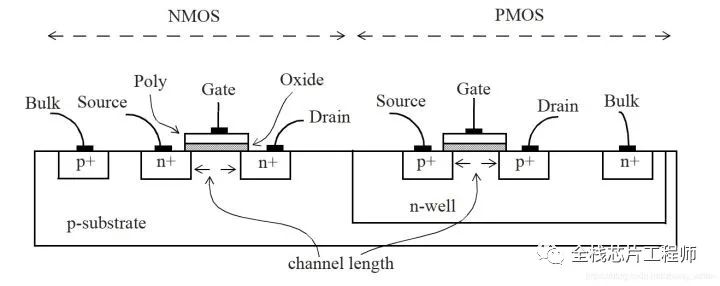

内部功耗又称短路功耗,在输入信号翻转时,信号的翻转不可能瞬时完成,因此PMOS和NMOS不可能总是一个截止另外一个导通,总有那么一小段时间是PMOS和NMOS同时导通,那么从电源VDD到地VSS之间就有了通路,就形成了短路电流。

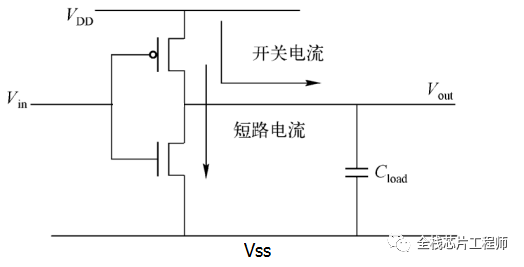

翻转功耗(Switching power)

顾名思义,Switching power 就是对输出电容进行充放电产生的功耗,其大小由电压、翻转率、负载电容决定。

漏电流功耗(Leakage Power)

即静态功耗,随着工艺节点演进到14nm、10nm、7nm等先进节点,Leakage Power的占比越来越高,Power gating的低功耗设计则十分关键。

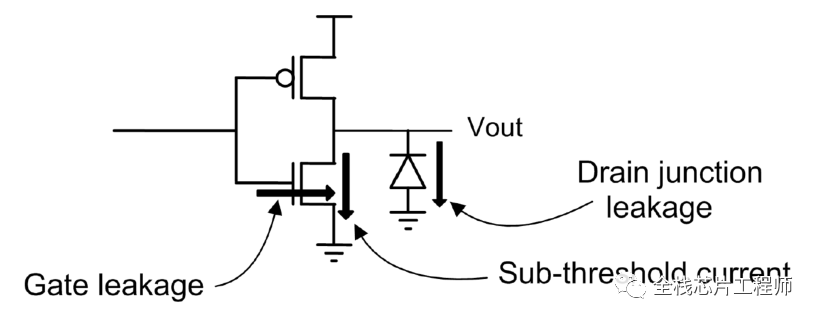

Leakage Power由以下几个部分组成:

1. 亚阈值漏电流(Sub-threshold Leakage, ISUB)

晶体管逻辑关断时,但沟道并没完全截止,导致channel中仍存在少量导通电流。那么,可提高阈值电压Vt,从而完全截止电流,但Vt越高,器件翻转速度就降低,PPA中,Power变好了,Performance就变差了。

2. 栅极漏电流(Gate Leakage, Igate)

由于栅极氧化物隧穿和热载流子注入,存在着通过氧化物流到衬底的电流。在65nm及以下节点工艺,栅极漏电流逐步增大到了亚阈值漏电流大小,因此,high-k高介电材料必须用以阻断栅极漏电流。

3. 栅极感应漏电流(Gate Induced Drain Leakage, IGIDL)

Gate引入的结泄漏电流与其他泄漏电流相比通常都很小。

4. 反向偏置结泄漏(Reverse Bias Junction Leakage ,IREV)

由少数载流子漂移、耗尽区产生电子/空穴对引起,通常也很小。

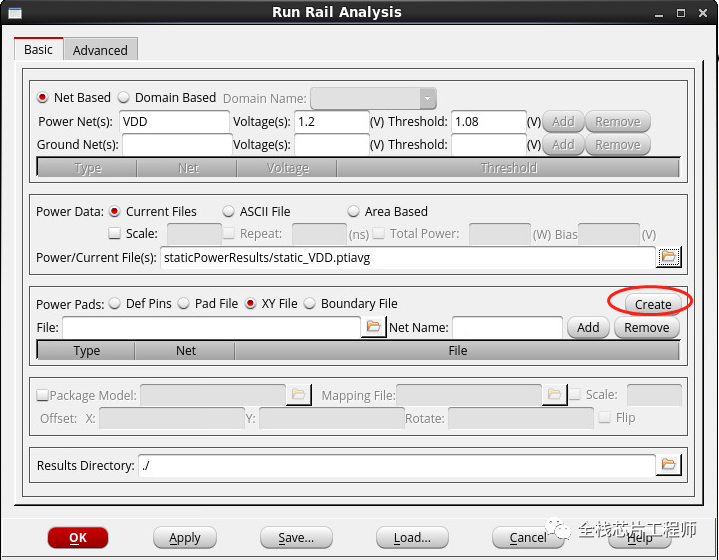

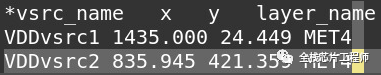

功耗分析完成后,工作目录下将得到power.rpt、power.db和*.ptiavg文件,其中*.ptiavg、power.db文件将用于IR分析,此外还需要指定voltage source location来提供电源源点的位置。

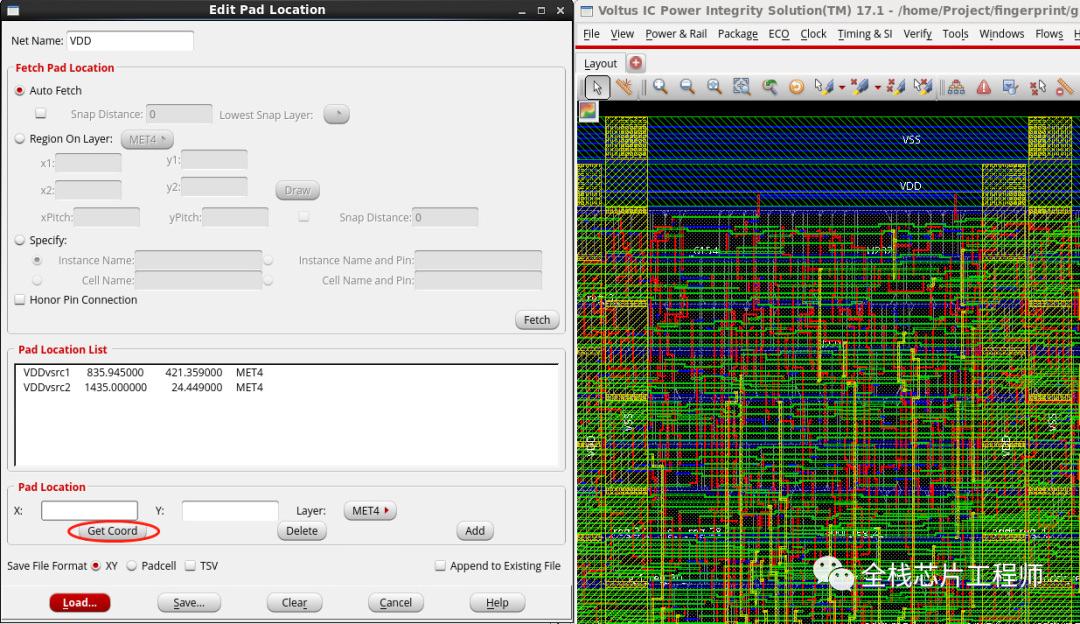

创建 Power Pads - XY File:

生成的 Power Pads - XY File如下:

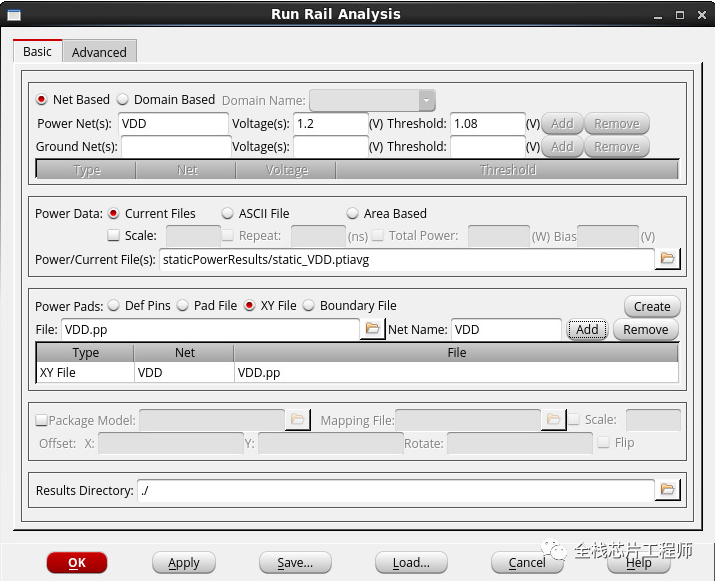

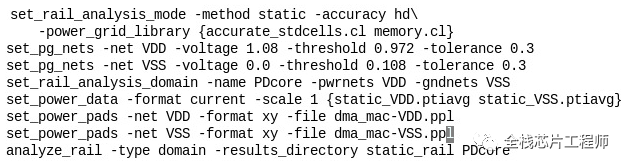

脚本流程参考如下:

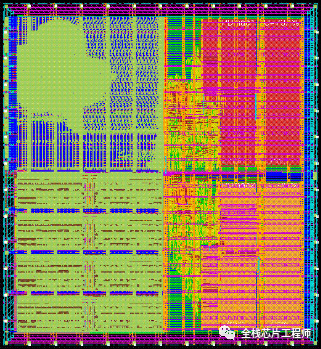

运行IR分析后,可得到相应报告及Rail analysis Plot:

审核编辑:刘清

-

NMOS

+关注

关注

3文章

404浏览量

36957 -

低功耗设计

+关注

关注

0文章

127浏览量

16795 -

漏电流

+关注

关注

1文章

280浏览量

17987 -

VDD

+关注

关注

1文章

319浏览量

37442 -

PMOS管

+关注

关注

0文章

84浏览量

7540

原文标题:芯片功耗的构成/IR分析

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IR推出IR3588 ChiL数字控制IC及IR3552、IR3546

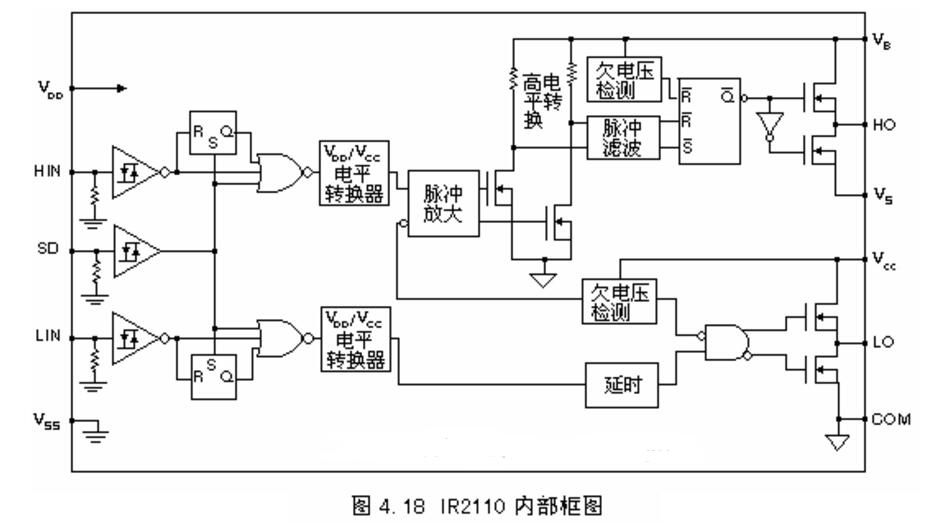

IR2110功率驱动集成芯片应用

新型电子镇流器控制芯片IR2156

IR推出二款DirectFET MOSFET芯片组

MOSFET半桥驱动芯片IR2111

IR2130集成芯片在逆变器中的设计应用

ir2110驱动工作原理_IR2110的特点和内部功能图及应用电路图

芯片功耗的IR分析

芯片功耗的IR分析

评论