除了SPI这种串行接口比较受存储器设计厂商的欢迎,还有比如由samsung和toshiba设计的Toggle NAND Interface,也被称为 Asynchronous DDR NAND Interface ( DDR:double data rate ,之所以设计成Asynchronous是因为最开始传统的存储器用的就是异步设计方法),虽然数据的传输速率得到了大大提升(使用DDR设计方法),但是确保数据准确性的设计却较为复杂。

另外一种比较受欢迎的接口就是由Cypress设计的 ONFI(Open NAND Flash Interface) NAND Interface, 据说现在的4.1版本已经能够达到1200MBps的传输速率了。而且使用的是NV-DDR3的1.2V电压标准,使得功耗也得到了改进。以上两种接口不是本篇文章讨论的重点,就暂且介绍到这里,感兴趣的朋友们可以在网上自行搜索更详细的资料了解学习,我们还是回到SPI接口上来。

下面我们就来讲讲为什么芯片常选用SPI作为与存储器互联的接口,也就是说SPI相较于其他接口有什么优势。

最主要的一个原因也是目前业界使用的大部分存储器( Serial NAND FLASH )使用的都是SPI接口,比如WINBOND家的,MICRON家的和GIGADEVICE家的,好像有种被绑架的感觉。。。

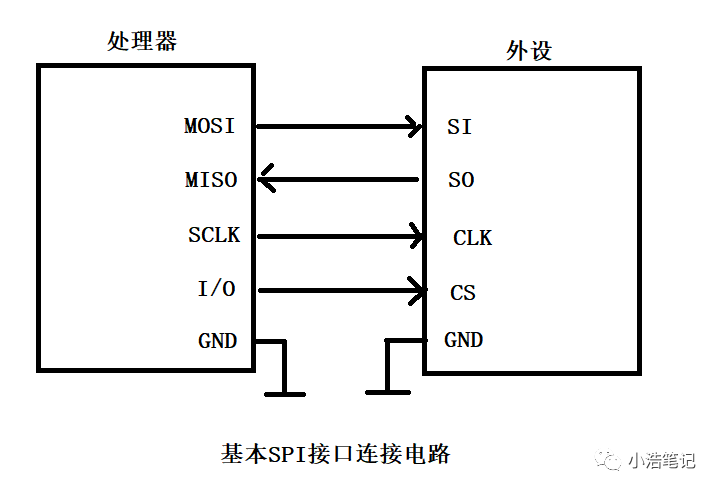

一般在SPI接口的数据端还会设计一个FIFO(数据宽度一般为8bit)来控制数据能够稳定被接收到,因此,SPI由一个缓冲区组成,该缓冲区通过 DMA (直接存储器访问)或CPU可寻址缓冲区与系统接口。时钟逻辑从内部系统时钟获得时钟,并可针对所需的速度进行编程。引脚控制逻辑提供输出驱动和延迟设置。可以有各种控制和状态寄存器为器件提供可编程性。

除此之外在物理实现的过程中会在接口产生一个延迟(正常情况不会超过两个时钟周期)。所以如果在full-duplex mode下,当slave已经将所需的数据都发送出去(发送的数据多少需要提前由master发出的指令决定),但是master还是会多产生几个时钟周期的SCLK和CS信号,这个时候就会采集到几个没有意义的数据线上的信号(signal low)。这个时候就需要系统软件识别出多余的信号然后将它们从有效数据中剔除出去。

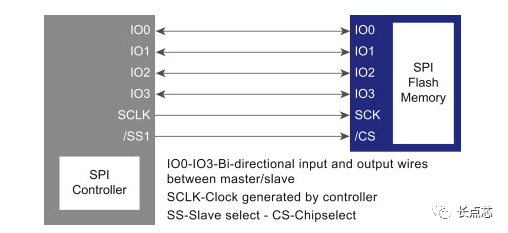

目前除了最开始介绍的传统四线数据线的SPI接口,为了进一步增大接口的数据传输速率,已经发展成了具有多个数据传输pin口的接口,比如说dual,quad SPI。

多个数据传输pin口

结语

SPI作为一个芯片常见的片外接口,适用于许多目前业界流行的Serial存储器设备,这些Serial NAND Flash一般作为储存芯片boot code的存储设备。有许多的优势所在,而相比于并行接口,改进后的串行接口目前也有较高的数据吞吐率以及成本较低的优势,无论是在工艺上还是功耗上。

-

存储器

+关注

关注

38文章

7452浏览量

163606 -

SPI

+关注

关注

17文章

1701浏览量

91326 -

串行接口

+关注

关注

3文章

326浏览量

42572

发布评论请先 登录

相关推荐

SPI接口的基本原理

用SPI接口扩展外部Flash存储器

Cyclone IV 器件中的外部存储器接口

基于DSP的存储器接口宽度调节设计

AXI内部存储器接口的功能

利用C8051F020的SPI接口扩展大容量数据存储器

信号完整性的价值:存储器接口设计

SPI接口在存储器接口上的应用

SPI接口在存储器接口上的应用

评论