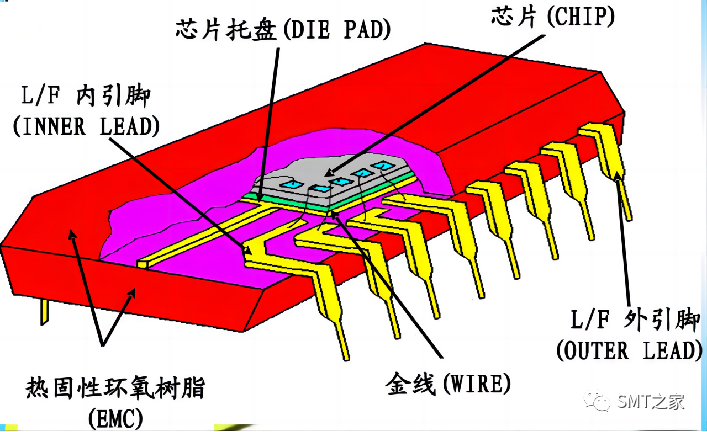

芯片封装的目的(The purpose of chip packaging):

芯片上的IC管芯被切割以进行管芯间连接,通过引线键合连接外部引脚,然后进行成型,以保护电子封装器件免受环境污染(水分、温度、污染物等);保护芯片免受机械冲击;提供结构支撑;提供电绝缘支撑保护。它可以更轻松地连接到PCB板上。

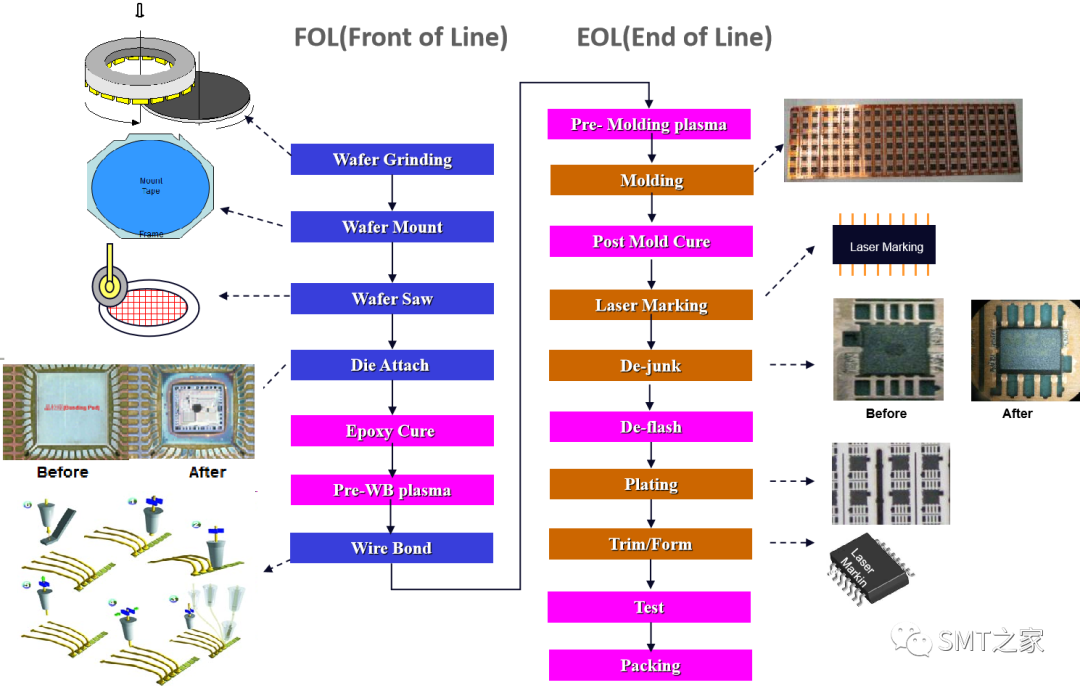

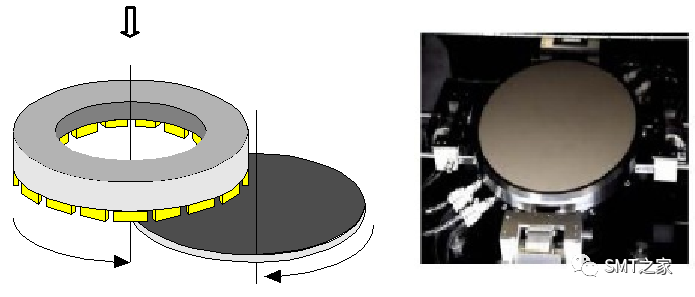

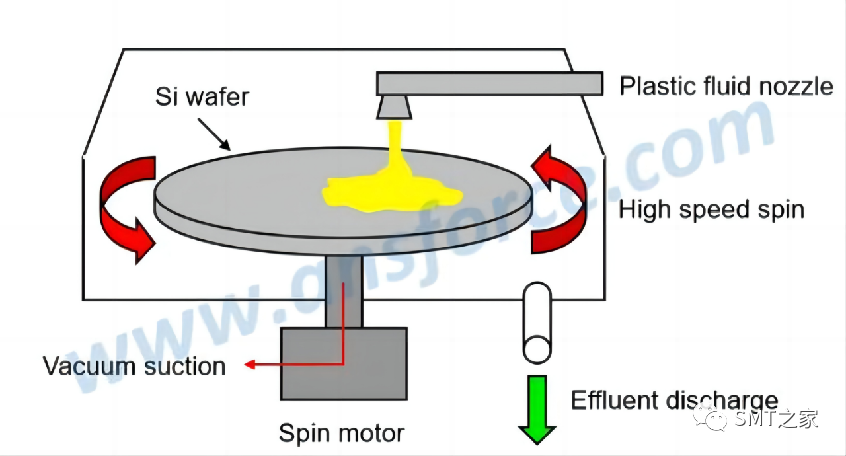

目的Purpose:

Make the wafer to suitable thickness for the package

将芯片制作成适合封装的厚度

|

Machine |

Disco(DFG8540) |

|

Material |

UVTape |

|

Control |

DIWaferResistivity |

|

VacuumPressure |

|

|

Check |

WaferRoughness |

|

WaferWarpage |

|

|

WaferThickness |

|

|

VisualInspection |

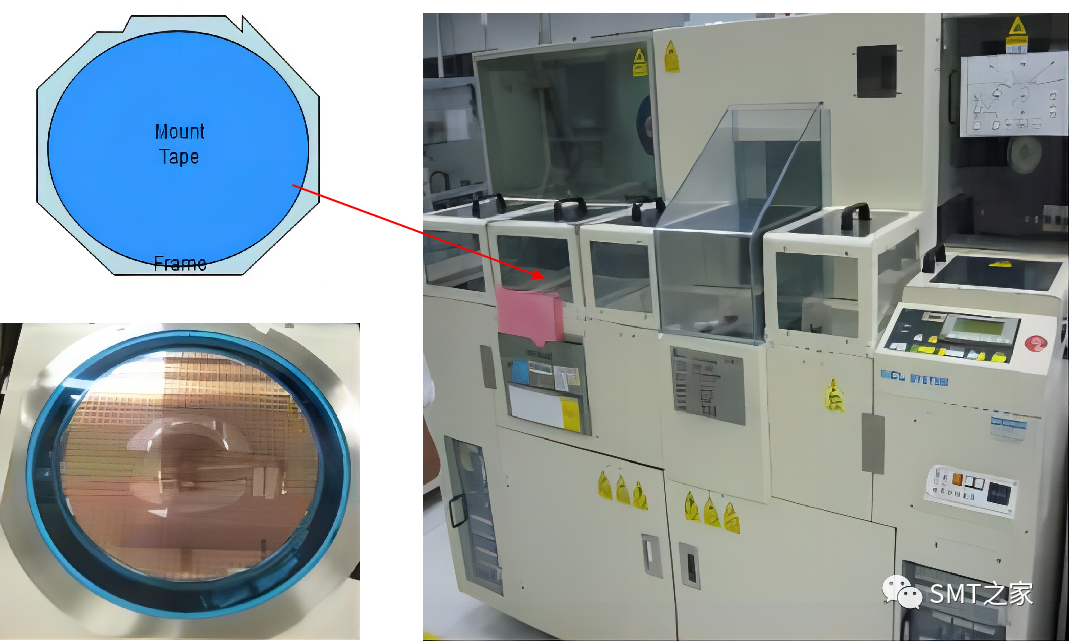

放入晶圆 Wafer Mount:

目的Purpose:

Combine the wafer with Dicing tape onto the frame for die sawing

将晶圆片与切割带装在框架上进行模切

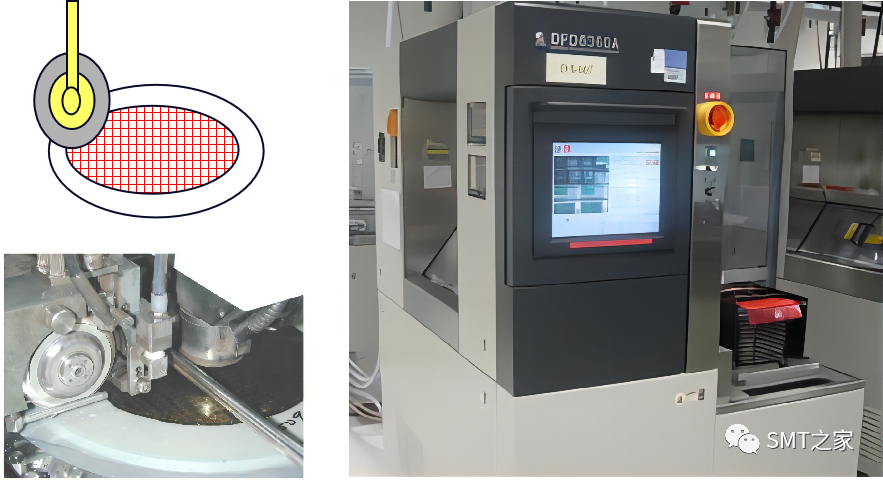

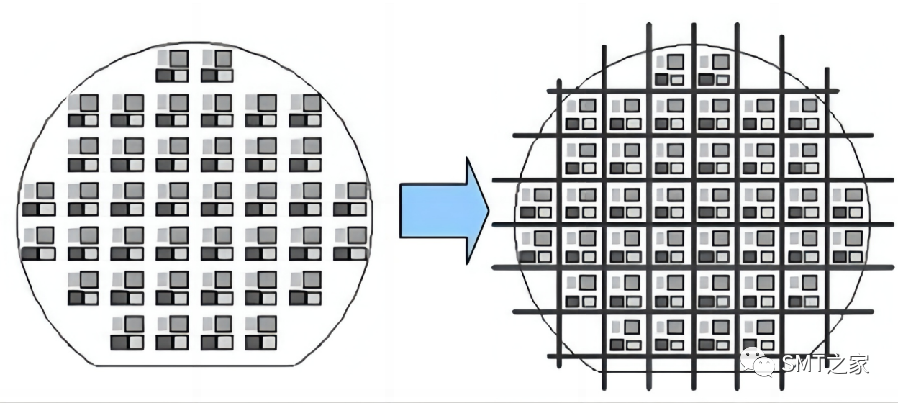

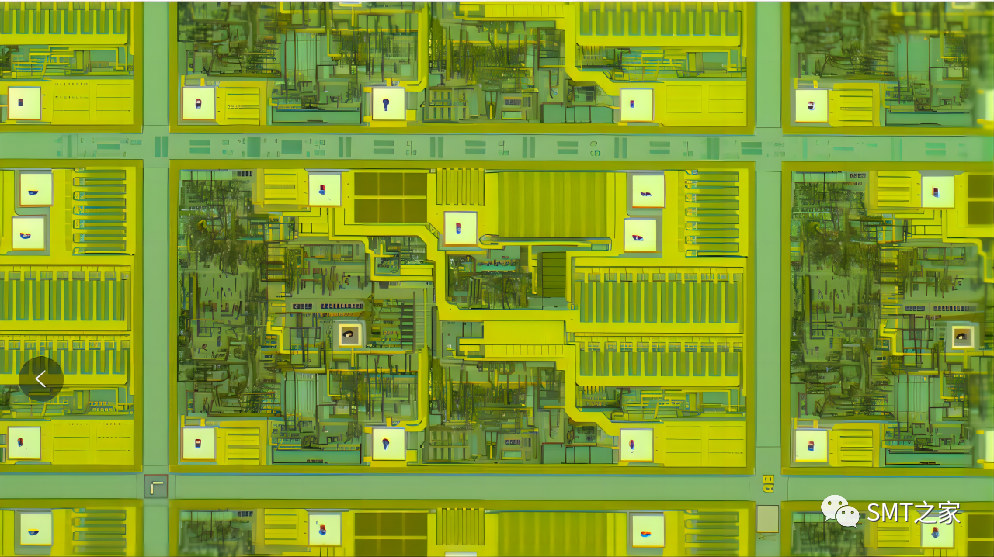

锯晶圆 Wafer Saw:

目的Purpose:

Make the wafer to unit can pick up by die bonder

使晶圆片单元能被粘片机拾取(吸取)

|

Machine |

Disco(DFD4360/DAD3350) |

|

Material |

SawBlade |

|

Control |

DIWaterResistivity(+CO2) |

|

Sawing/CleaningParameter |

|

|

Check |

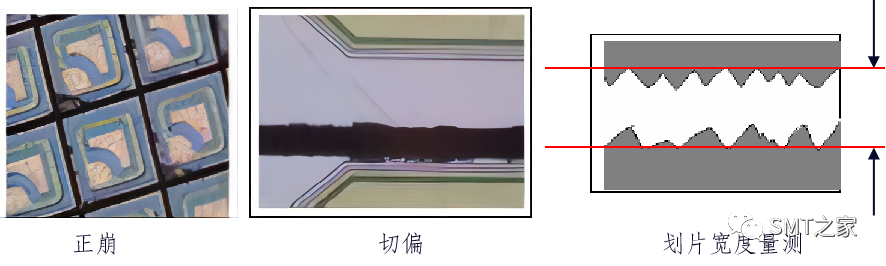

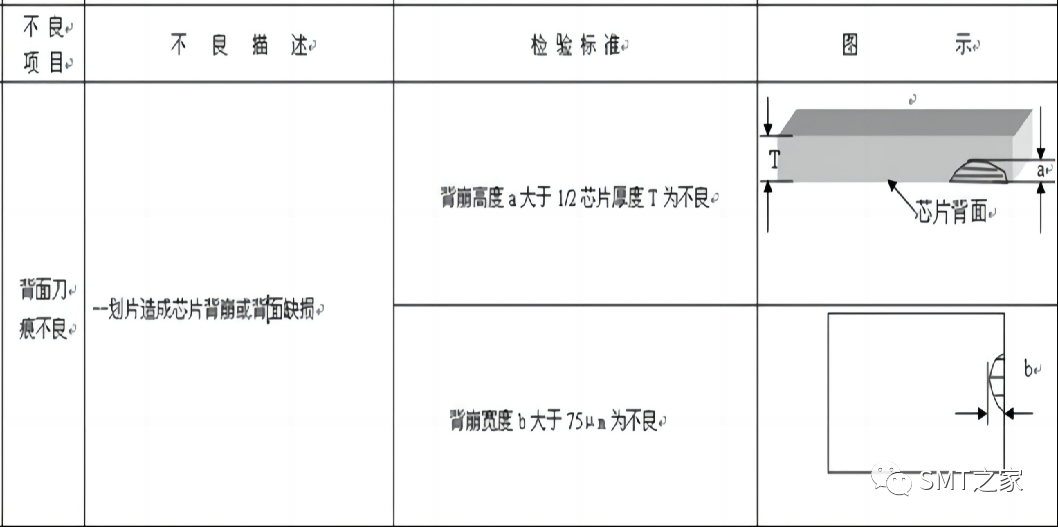

KerfChippingWidth |

|

VisualInspection |

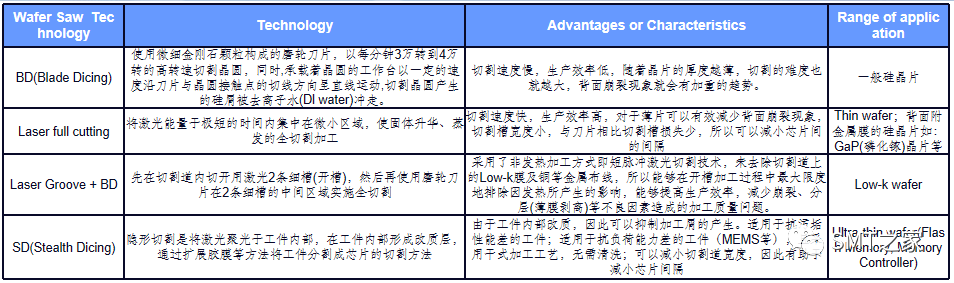

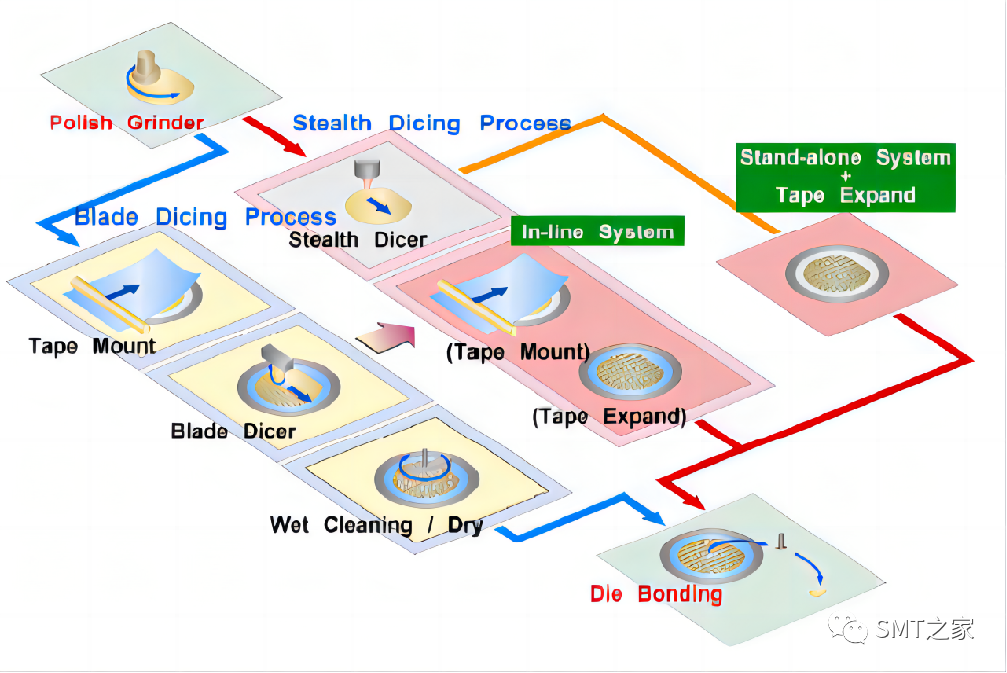

BD和SD的流程区别 Process difference between BD and SD:

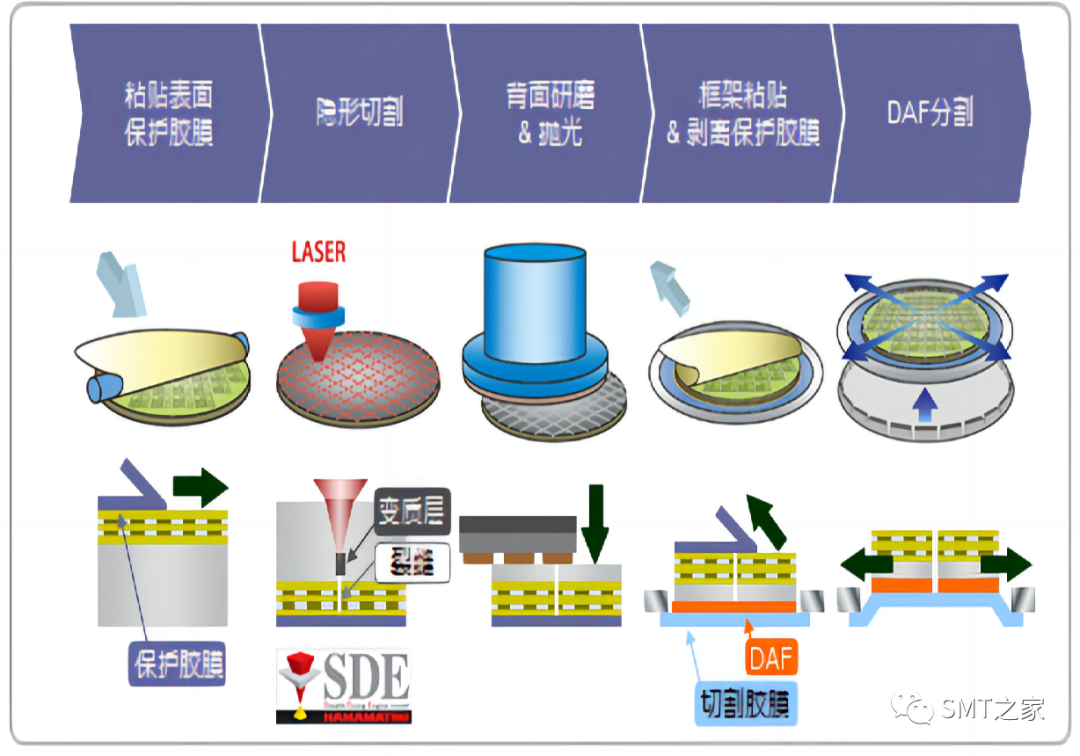

SDBG:

质量控制 Quality Control

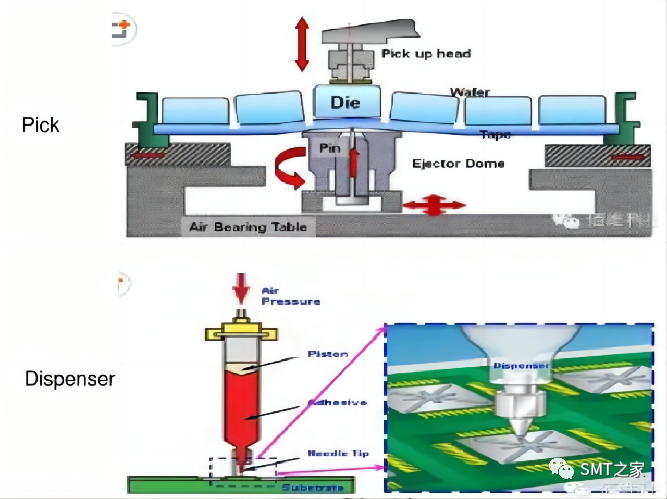

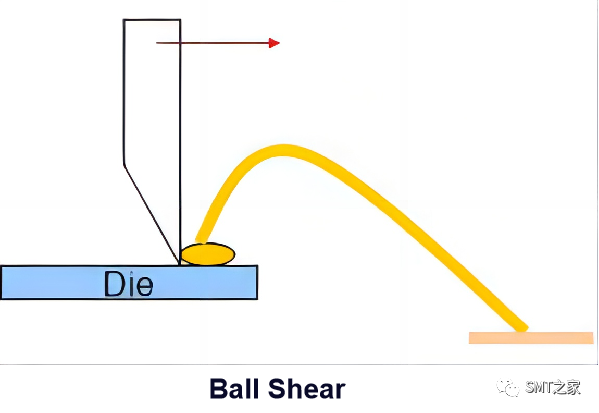

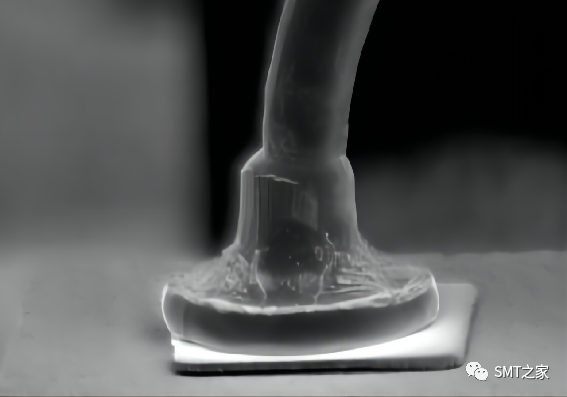

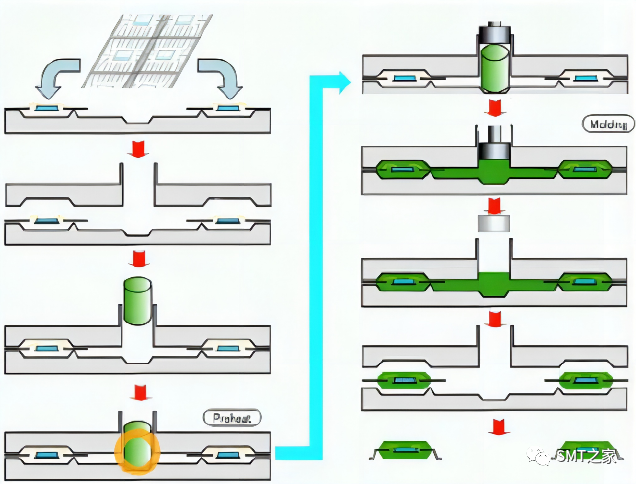

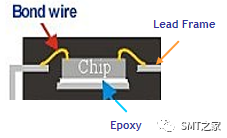

上芯Die Attach:

目的Purpose:

Pick up the die and attach it on the lead frame by epoxy

吸取芯片,用环氧树脂将其附在引线框上

|

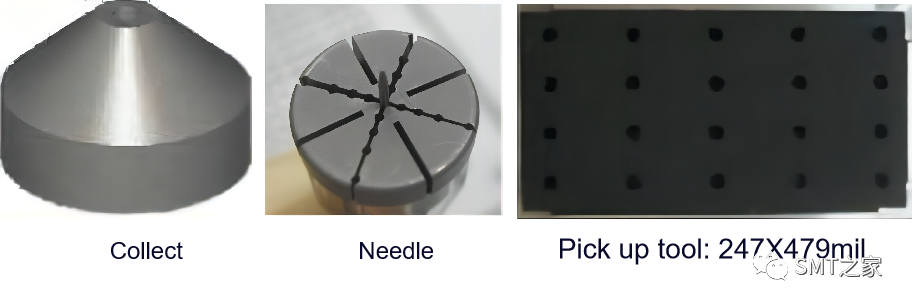

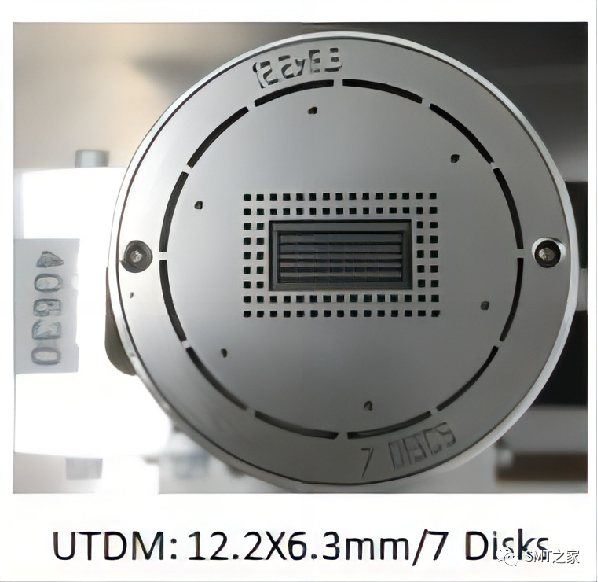

Machine |

ESEC/ASM |

|

Material |

Epoxy/Leadframe |

|

Control |

BondingParameter |

|

Collect/NeedleHeight |

|

|

Check |

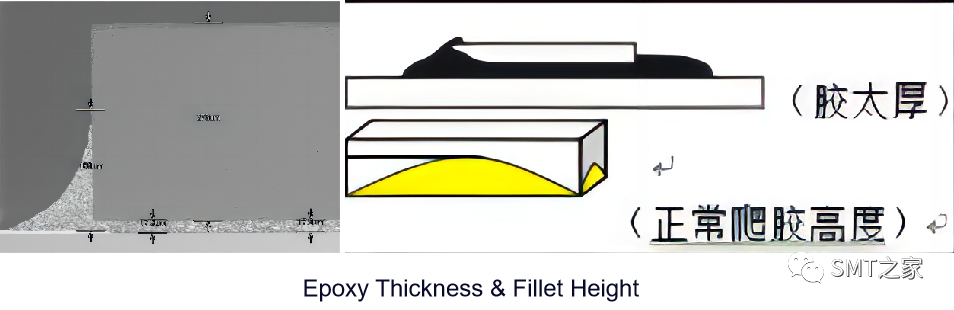

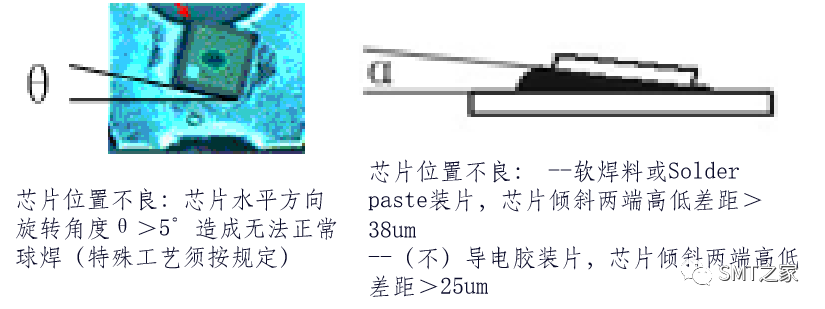

EpoxyThickness/DieTilt |

|

BondingPosition/DieShear |

|

|

VisualInspection |

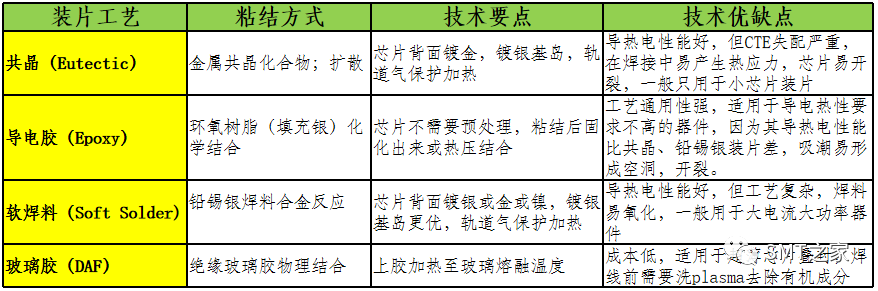

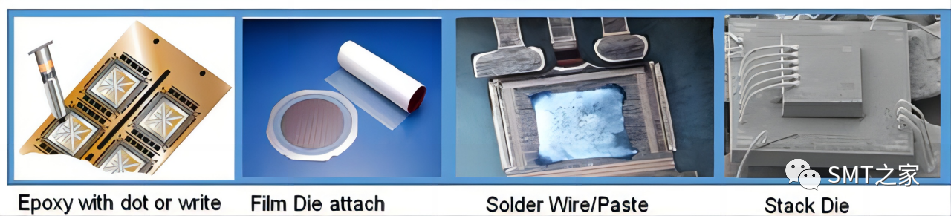

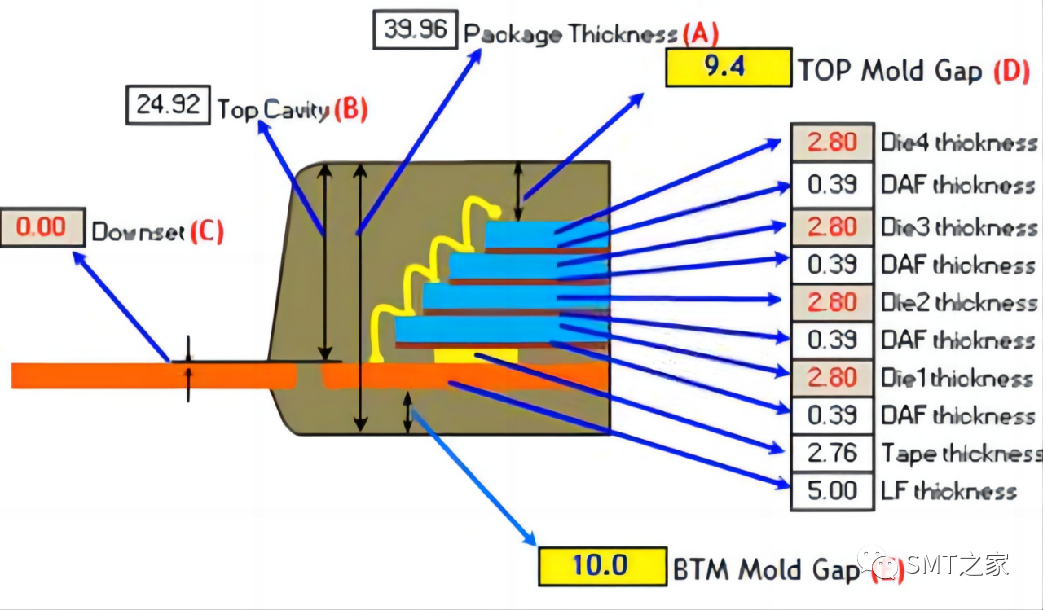

芯片连接方法 Die attach method:

Eutectic, Epoxy, soft solder, DAF

共晶,环氧,软钎料,DAF

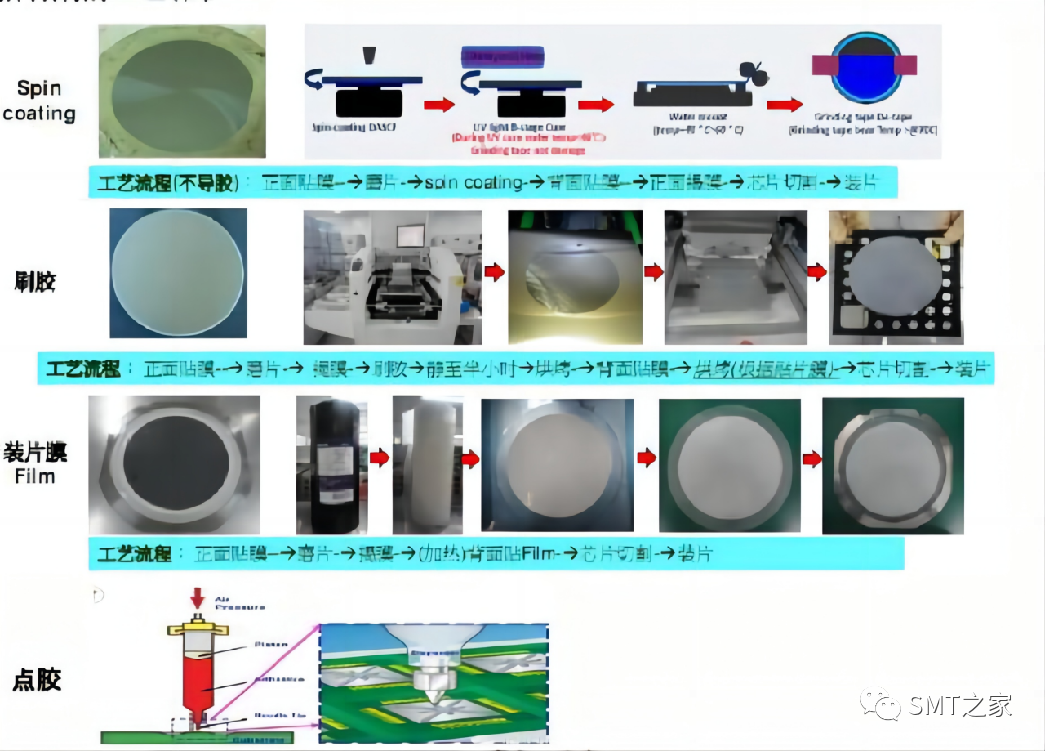

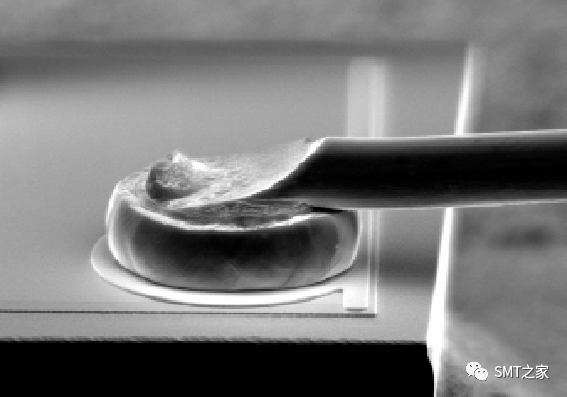

粘着剂的工艺流程:

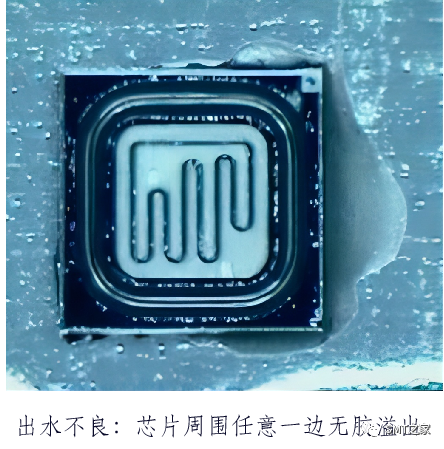

质量控制Quality Control:

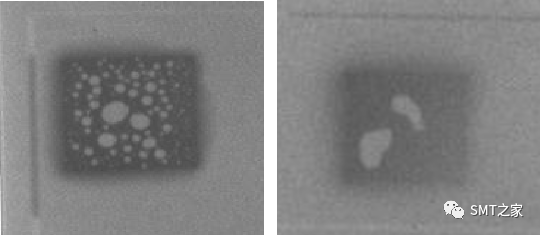

空洞不良:焊料装片单个空洞面积大于3%芯片面积,累计空洞面积大于8%芯片面积Solder paste 装片单个空洞面积大于5%芯片面积,累计空洞面积大于10%芯片面积

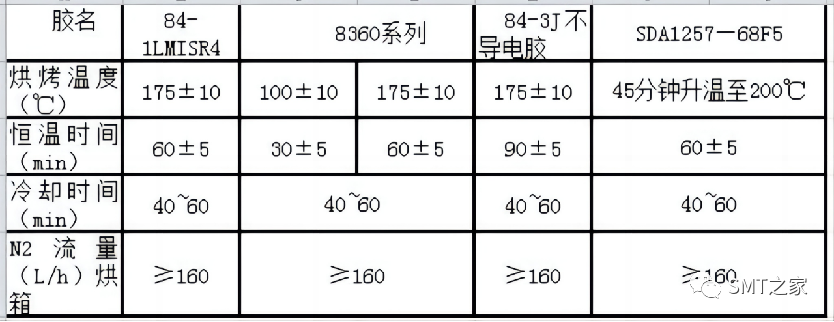

环氧固化 Epoxy cure:

目的Purpose:

Solidify the epoxy after D/A 固化环氧树脂后D/A

固化烤炉箱Oven

烤箱内Inside

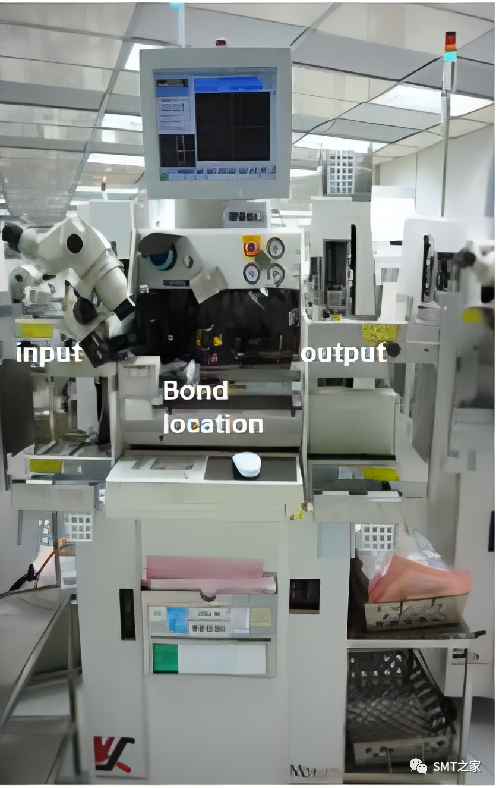

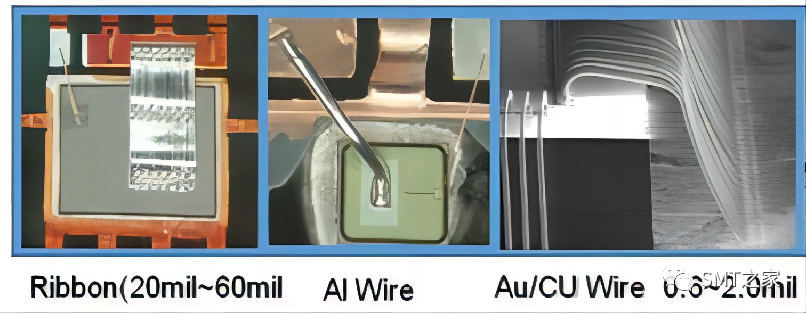

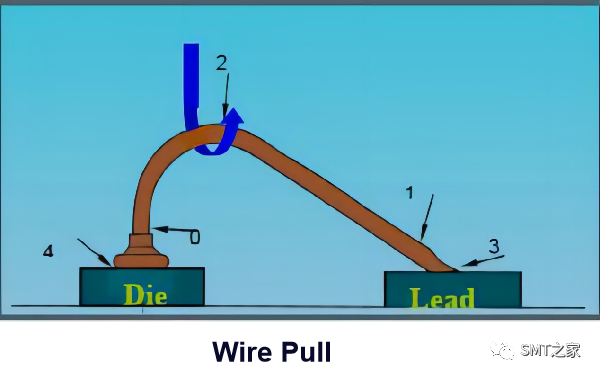

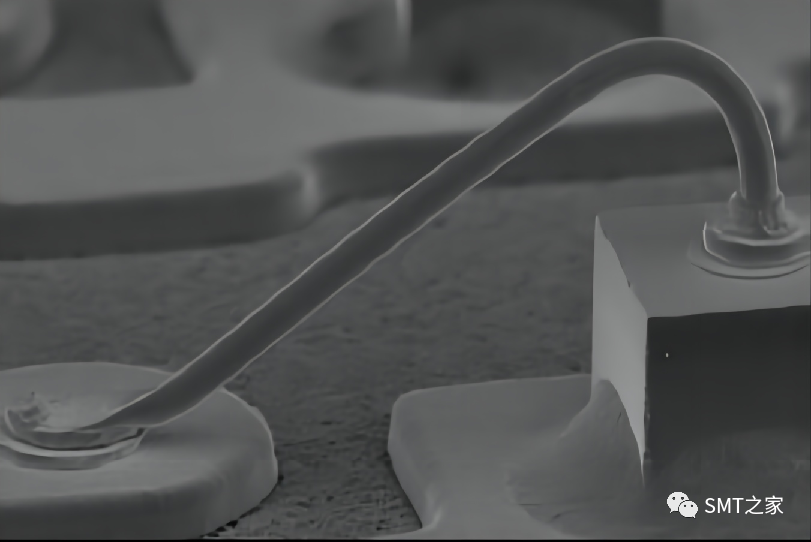

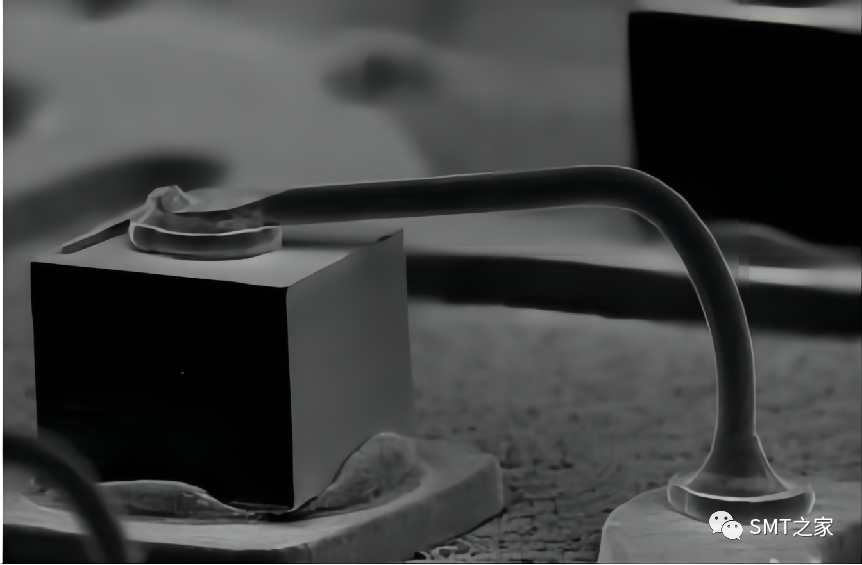

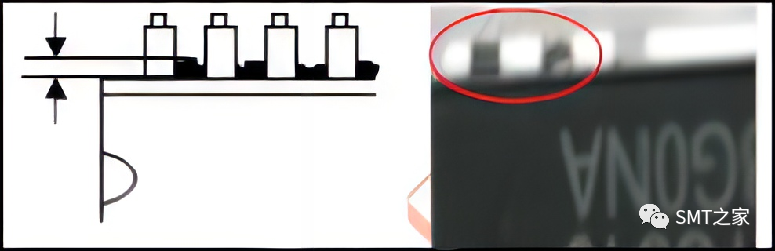

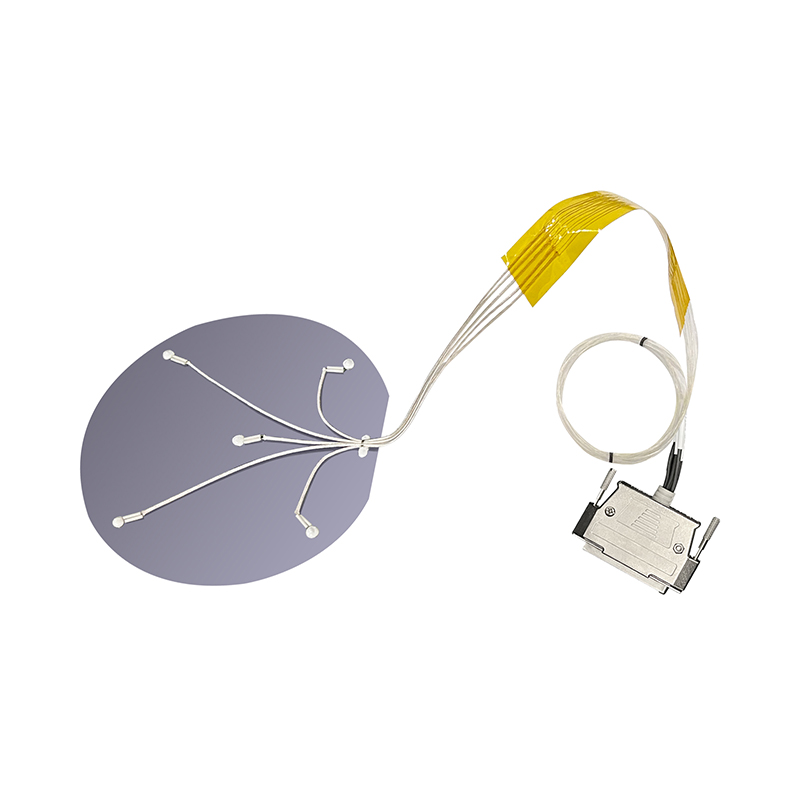

引线键合Wire Bonding:

目的 Purpose:

Use ultrasonic, force , temp, time to connect the bond pad with lead frame by gold/copper/Silver/Aluminium wire.

采用超声波、力、温度、时间等方法,将焊盘与引线框通过金/铜/银/铝导线连接。

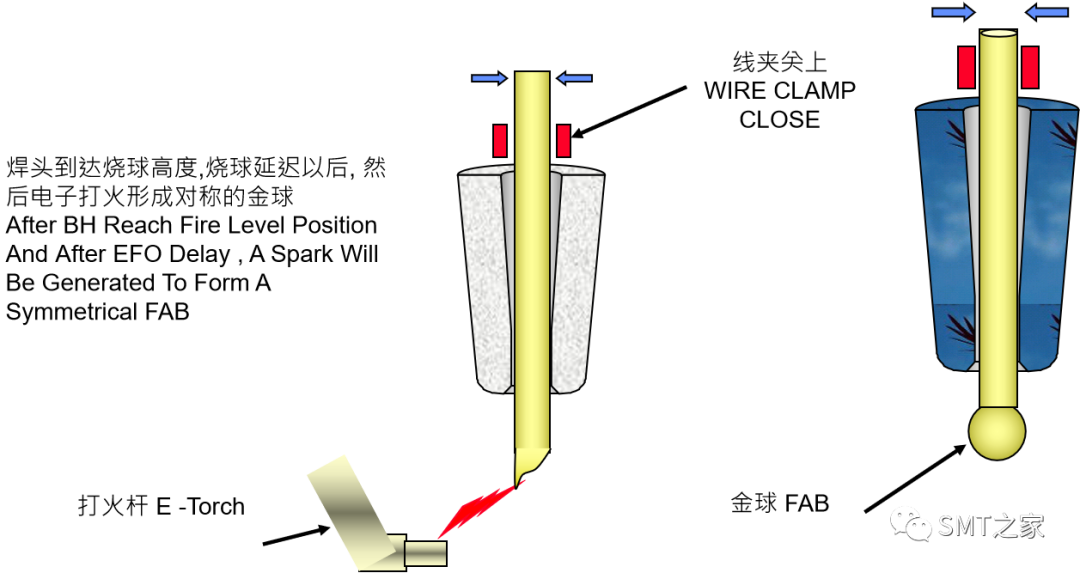

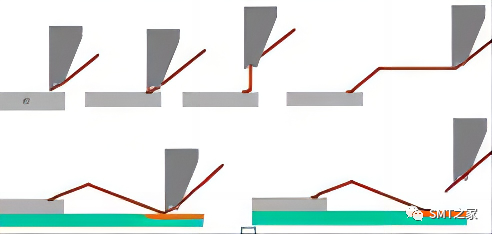

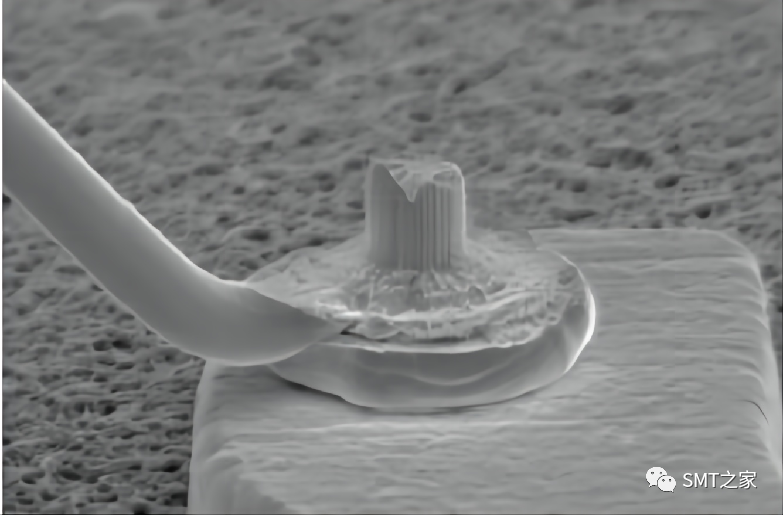

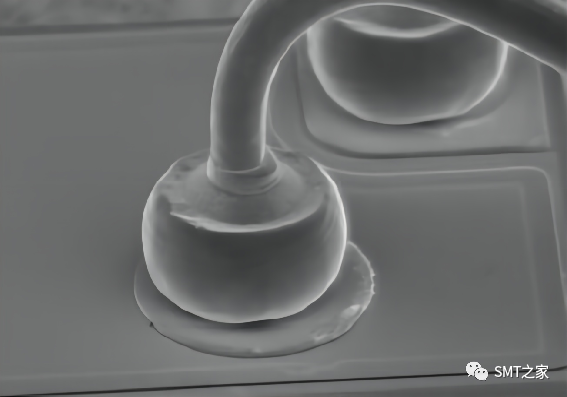

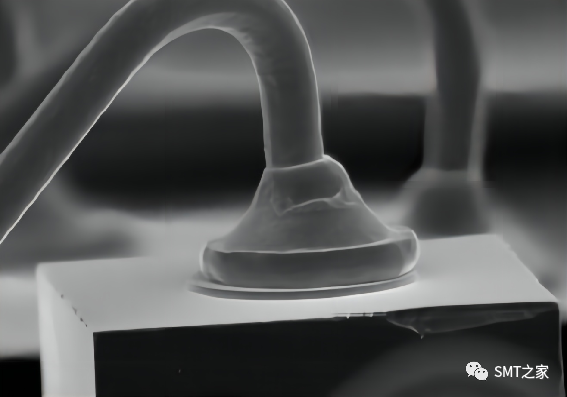

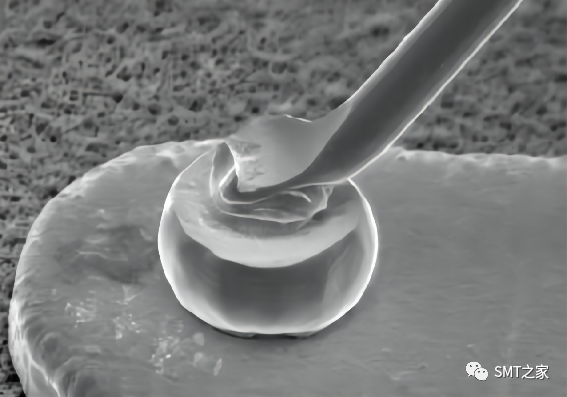

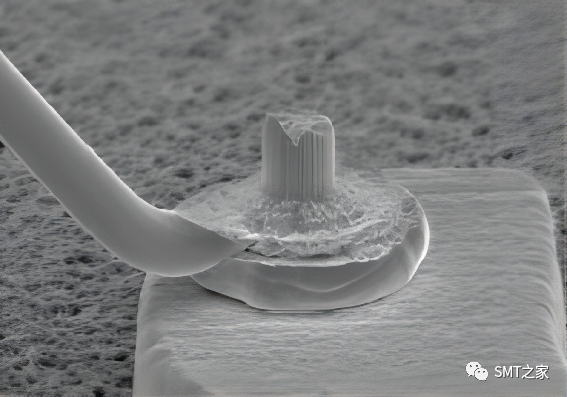

球键合Ball Bonding

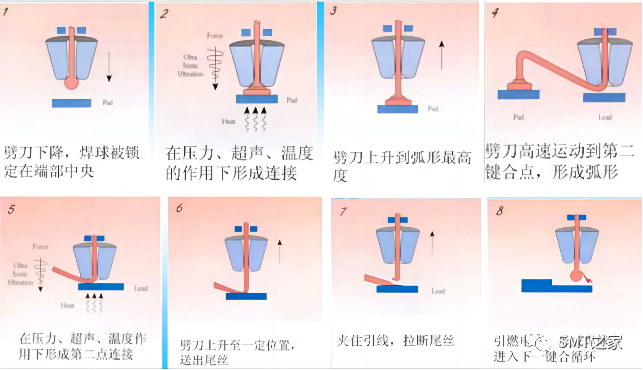

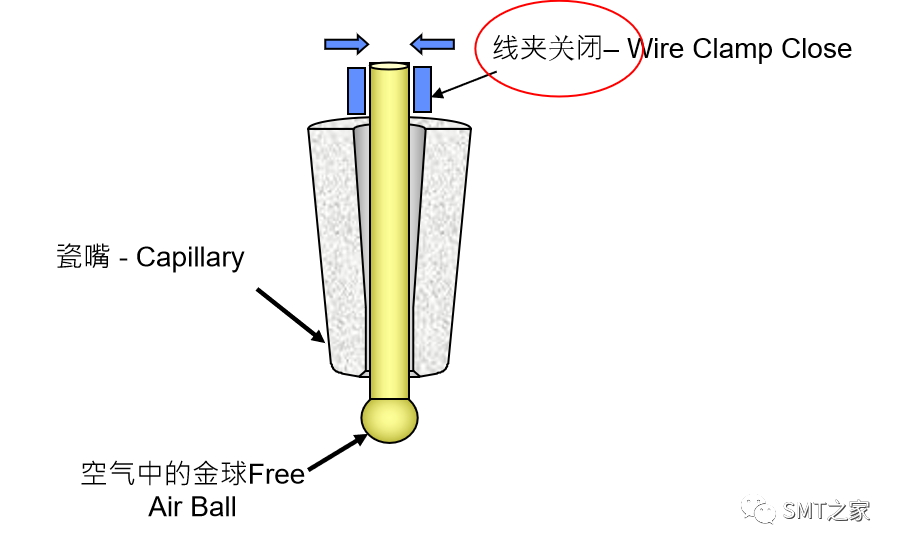

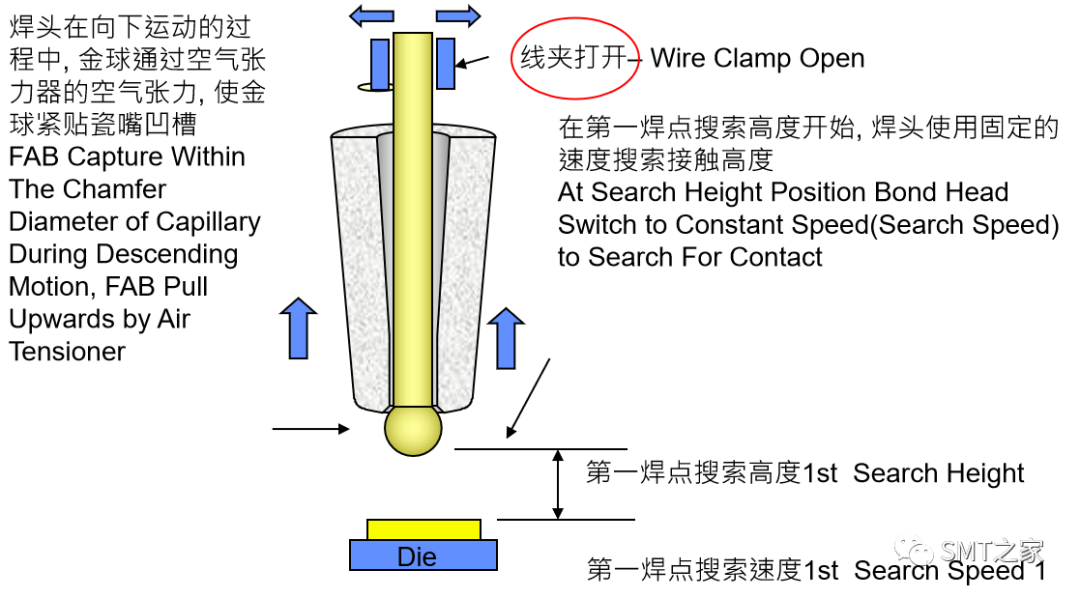

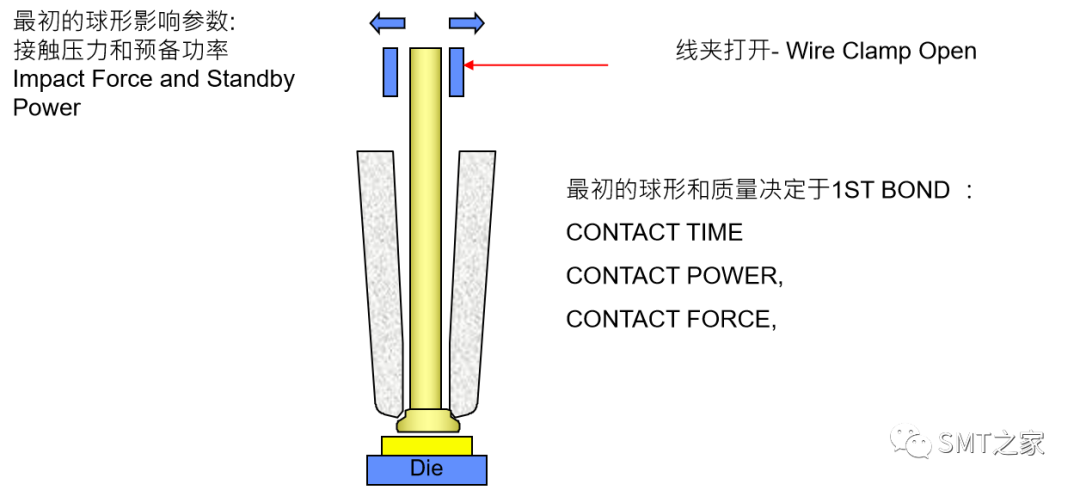

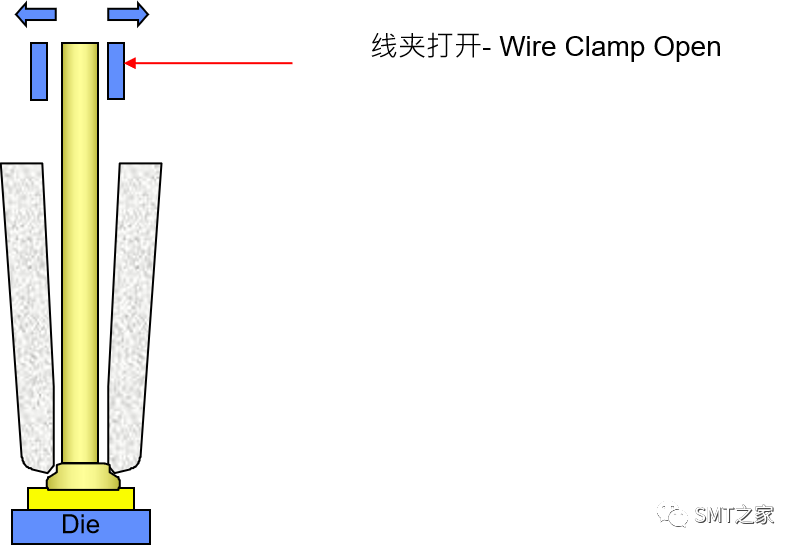

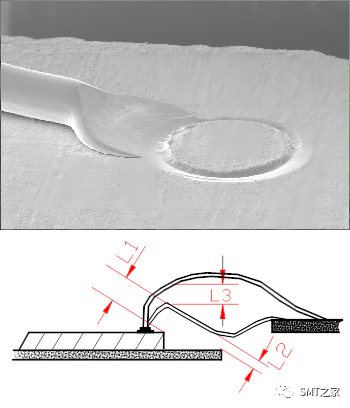

焊线焊头动作步骤分解:

1• 焊头在打火高度( 复位位置 )

2•焊头由打火高度下降到第一焊点搜索高度

3•第一焊点接触阶段

4•第一焊点焊接阶段

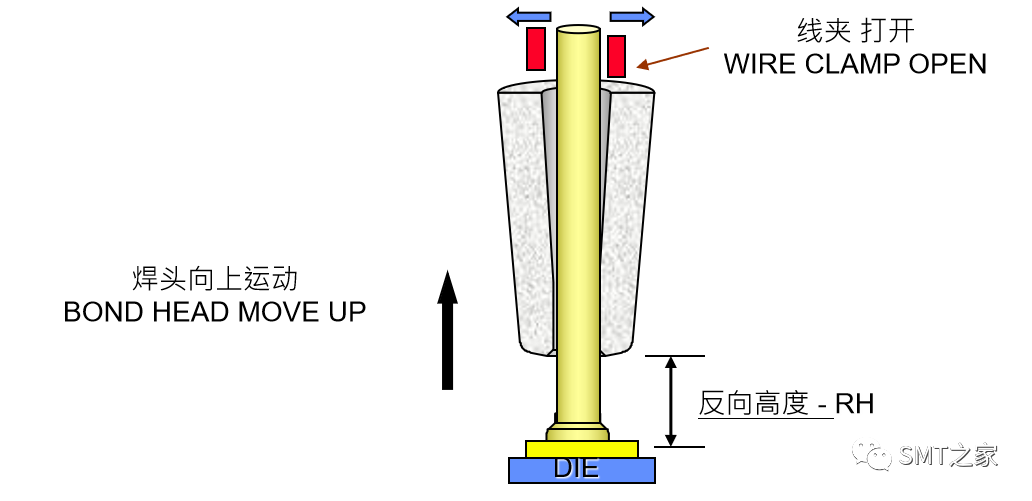

5•完成第一点压焊后, 焊头上升到反向高度

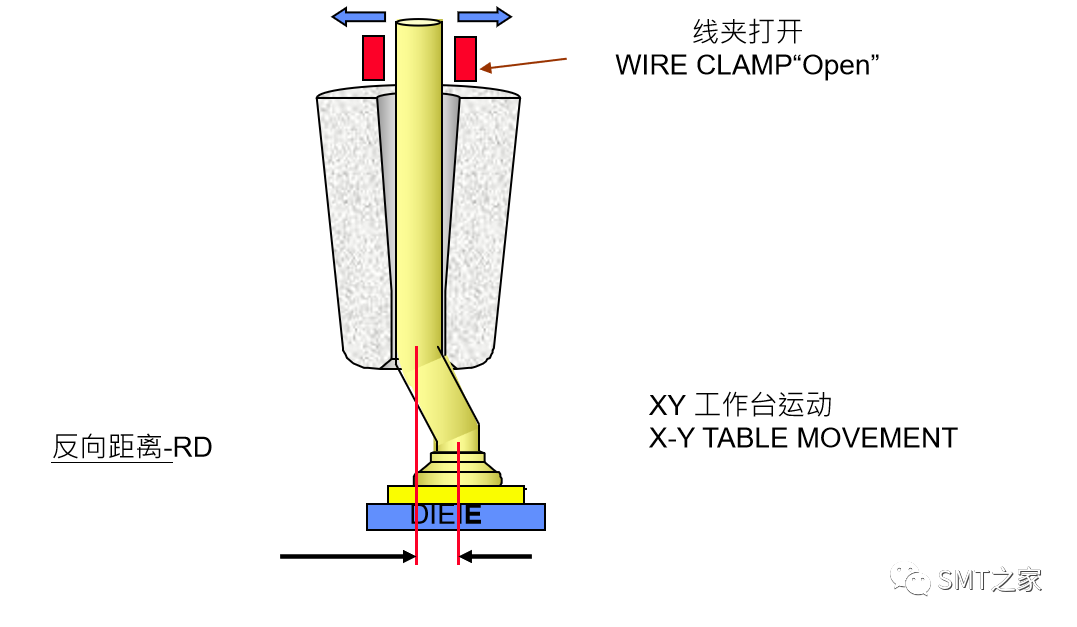

6•反向距离

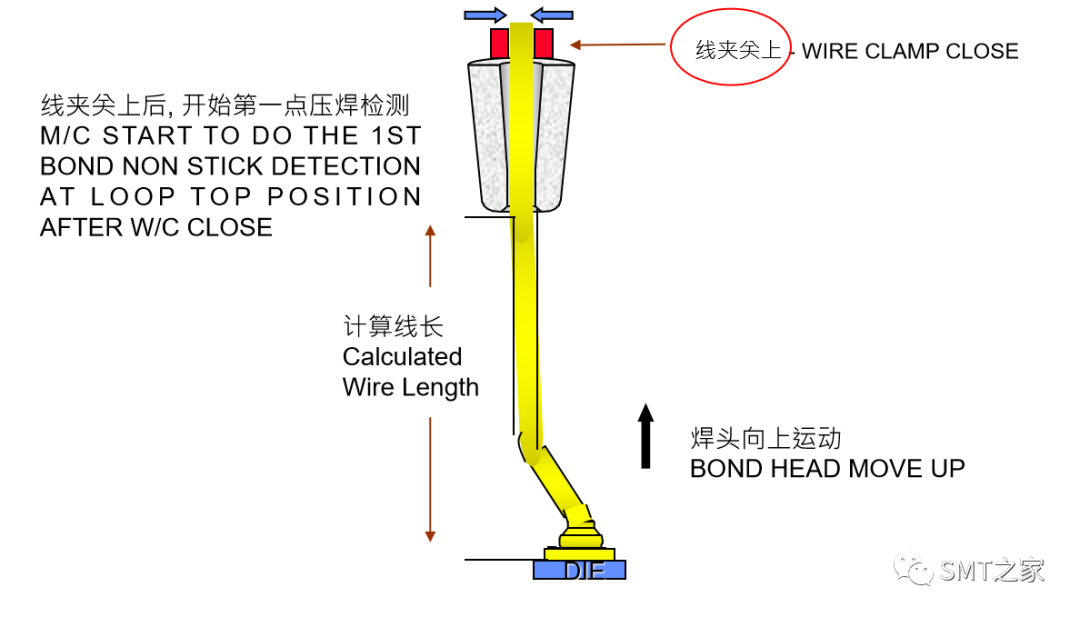

7•焊头上升到线弧高度位置

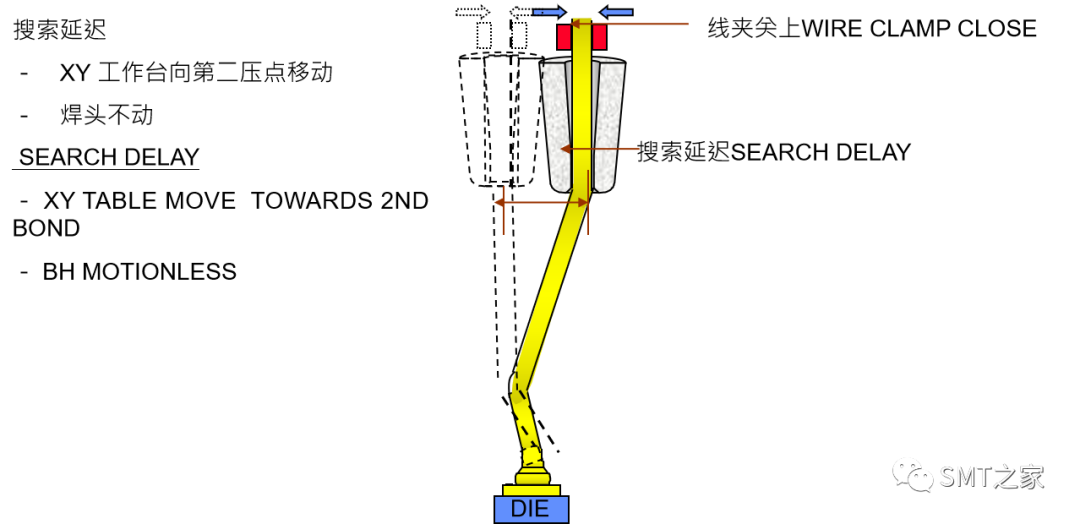

8•搜索延迟

9•XYZ 移向第二压点搜索高度

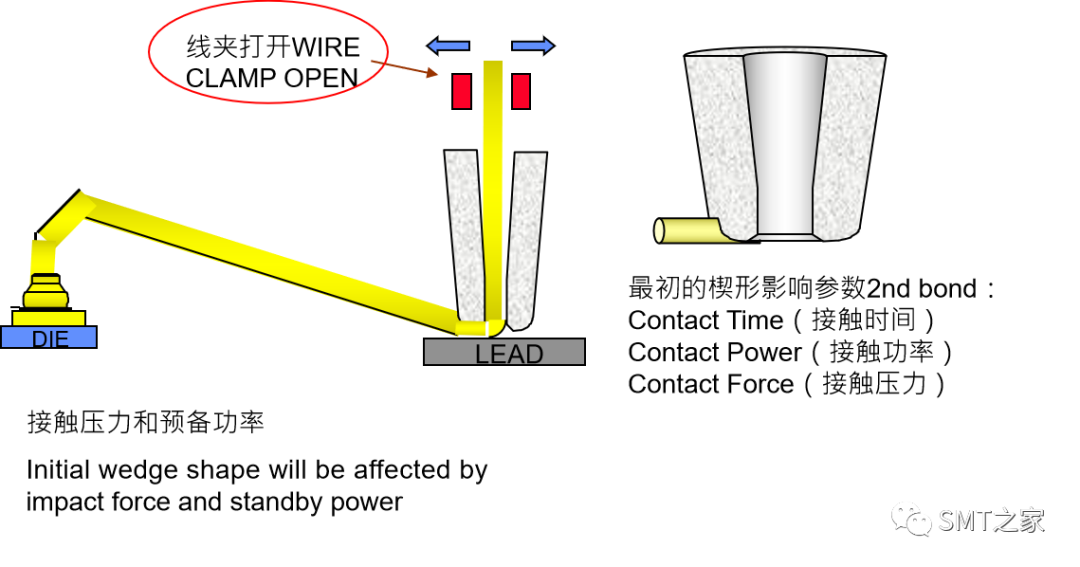

10•第二焊点接触阶段

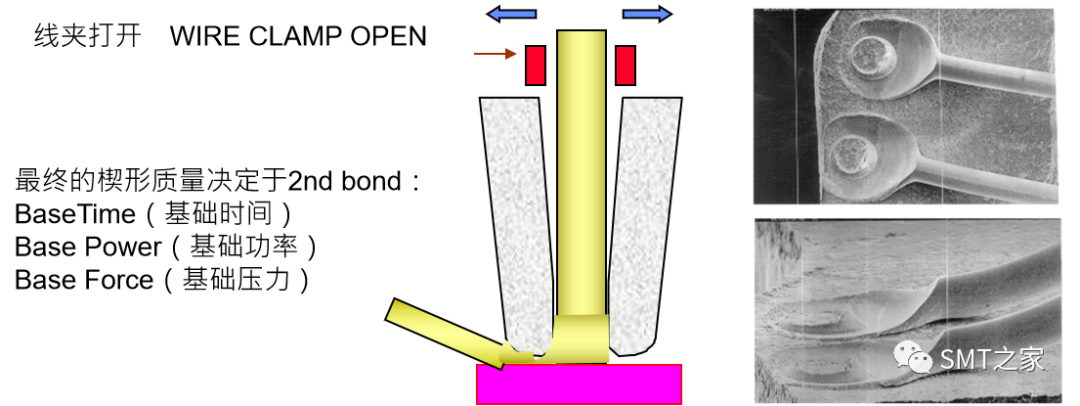

11•第二压点焊接阶段

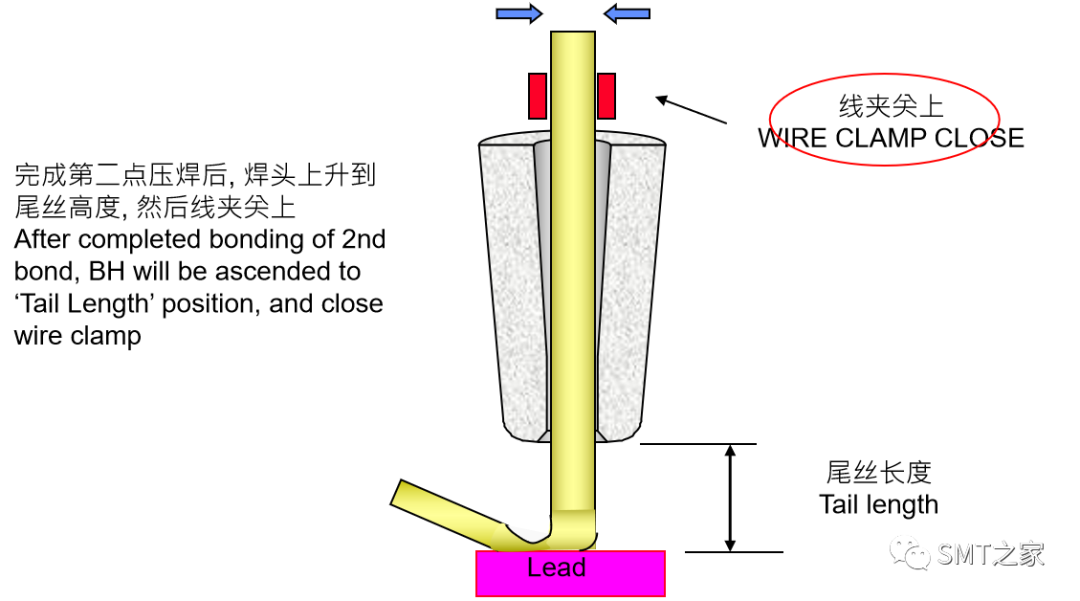

12•焊头在尾丝高度

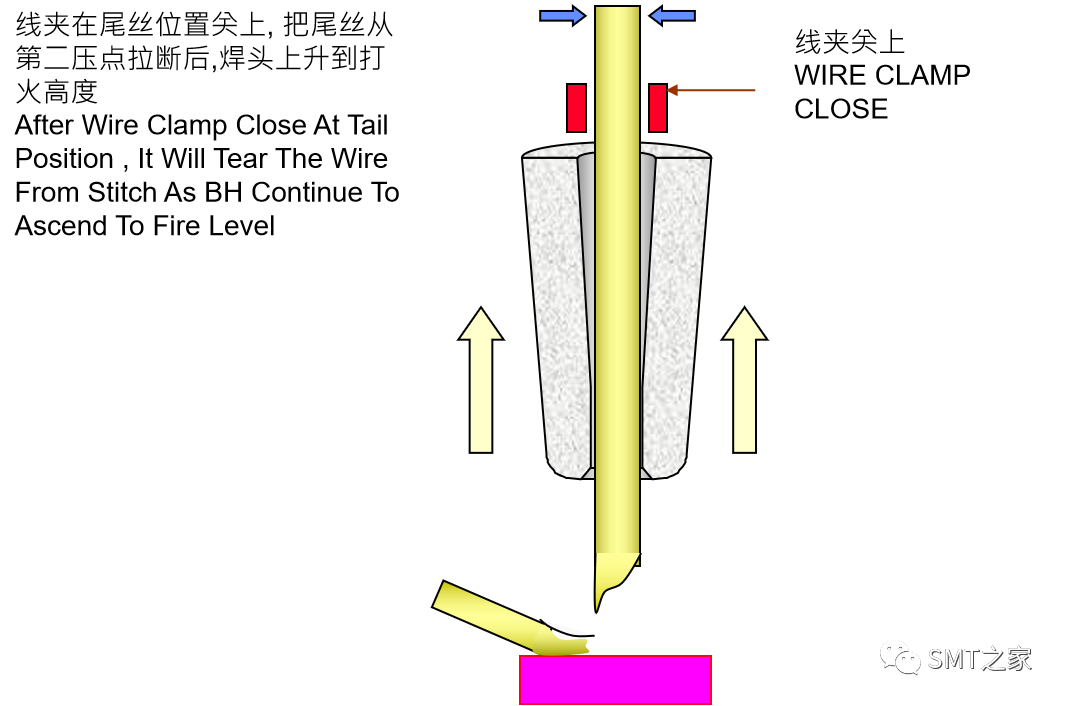

13•拉断尾丝

14•金球形成,开始下一个压焊过程

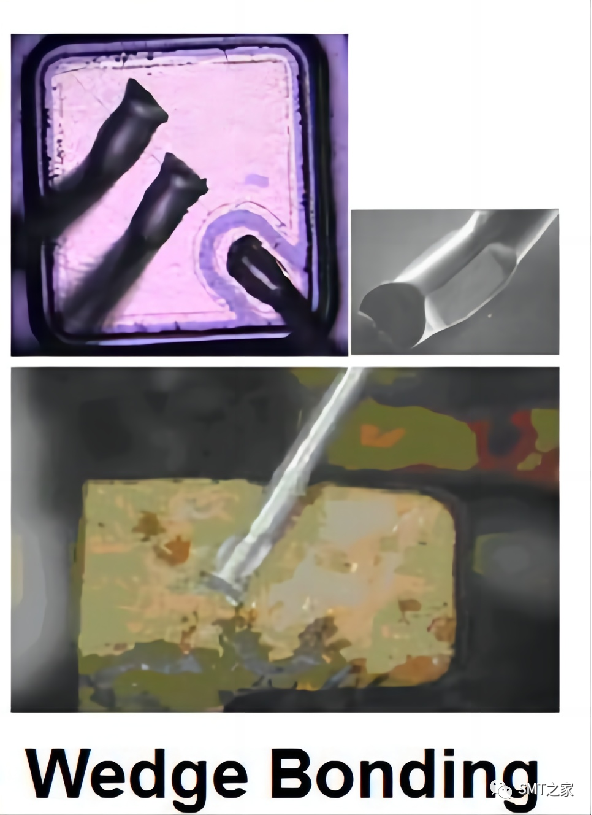

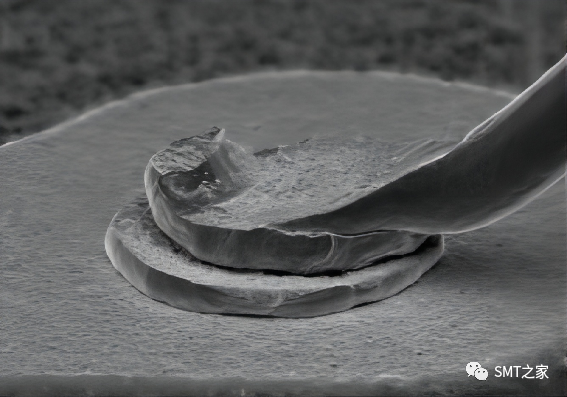

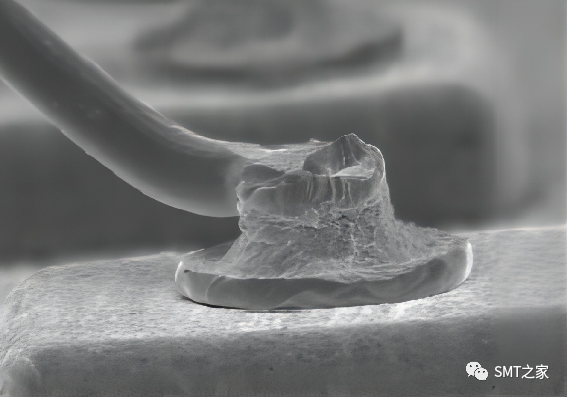

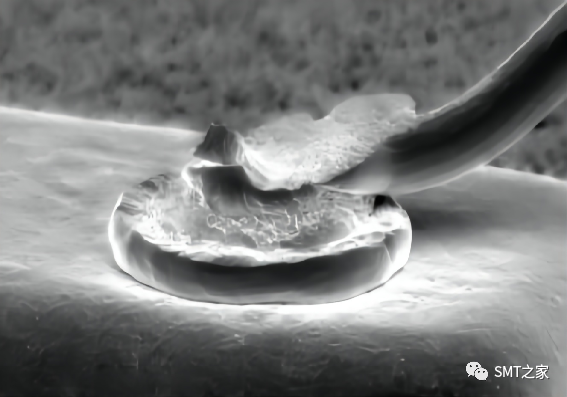

楔键合 Wedge Bonding

The difference between Ball Bonding and Wedge Bonding

球焊Ball Bonding和键合Wedge Bonding的区别

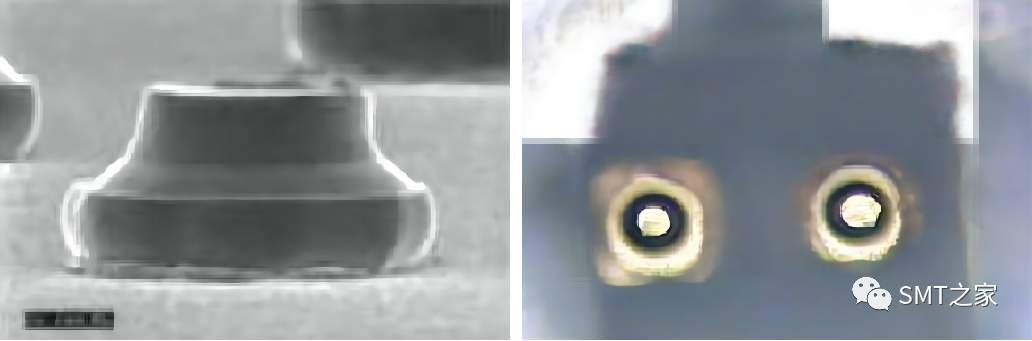

1、在一定温度下,在超声发生器作用下,通过焊能头使电能转变为机械振动,带动金球、铜球与铝层产生塑型形变,形成良好的牢度。(在形成球时需要用氢氮混合气体避免铜线氧化)

2、键合又叫锲形焊,是因为它的压点象锲形(三棱镜)。在常温下,铝丝通过换能头及劈刀的机械振动,与铝层粘合在一起。它的优点是不会产生化合物。

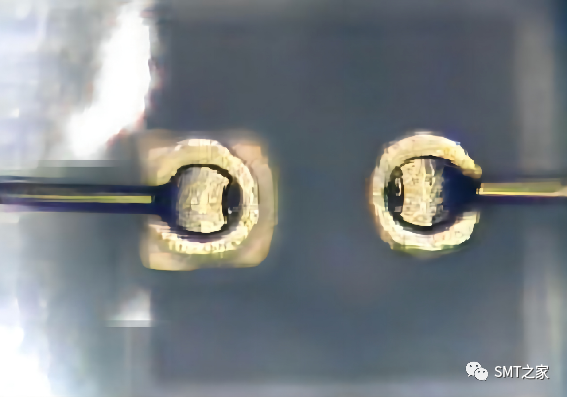

质量控制 Quality Control:

Wire Offset 0

Wire Offset 45

Wire Offset 55

Wire Offset 65

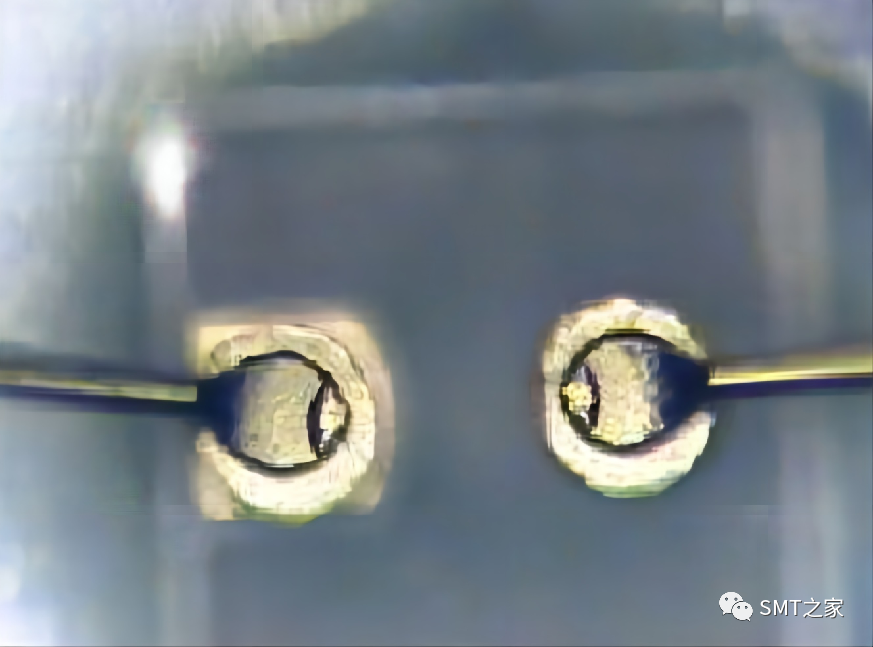

BSOB BALL

最佳BSOB效果

FAB过大,BASE参数过小

BASE参数过大

正常

BALL过大,STICH BASE参数过小

BALL过小,STICH BASE参数过大

正常

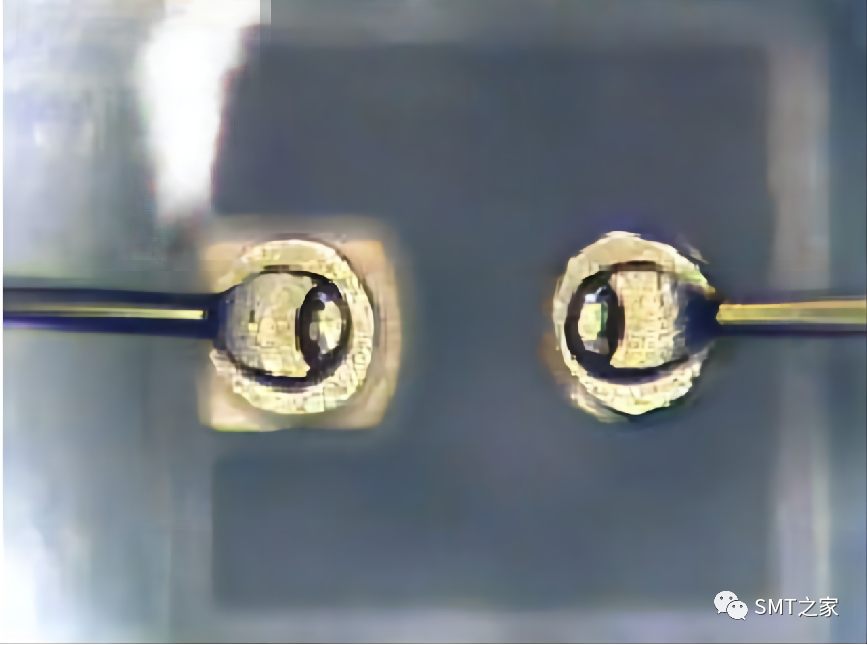

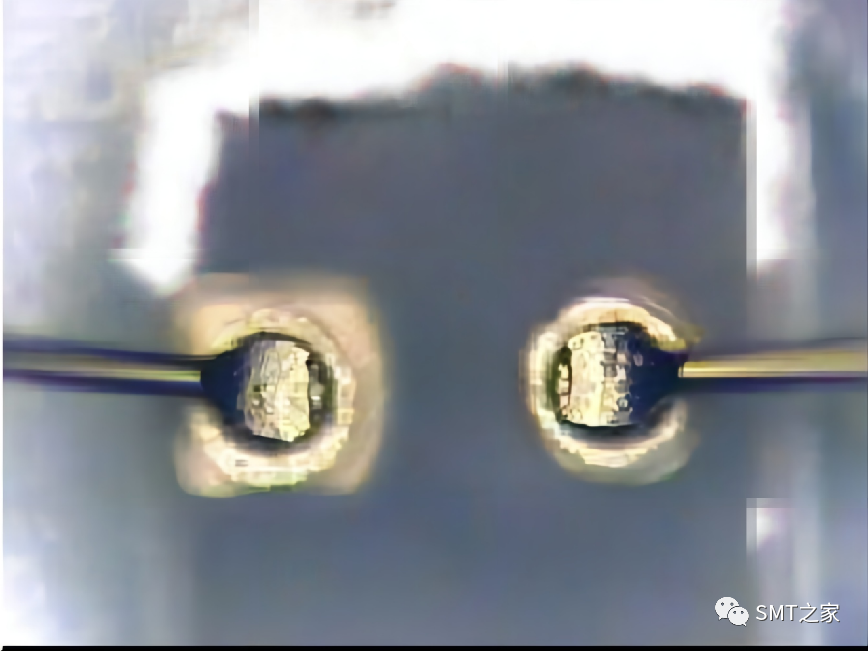

BSOB 2nd stich不良

好

不好

好

不好

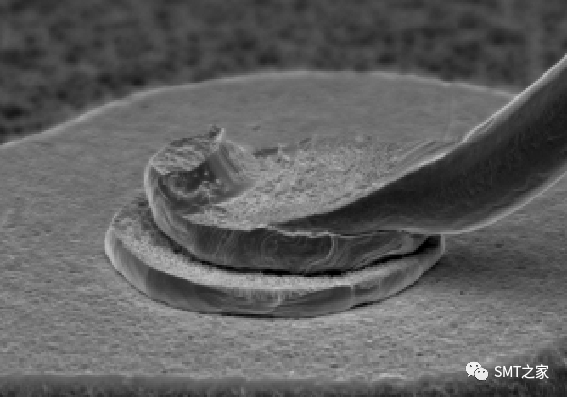

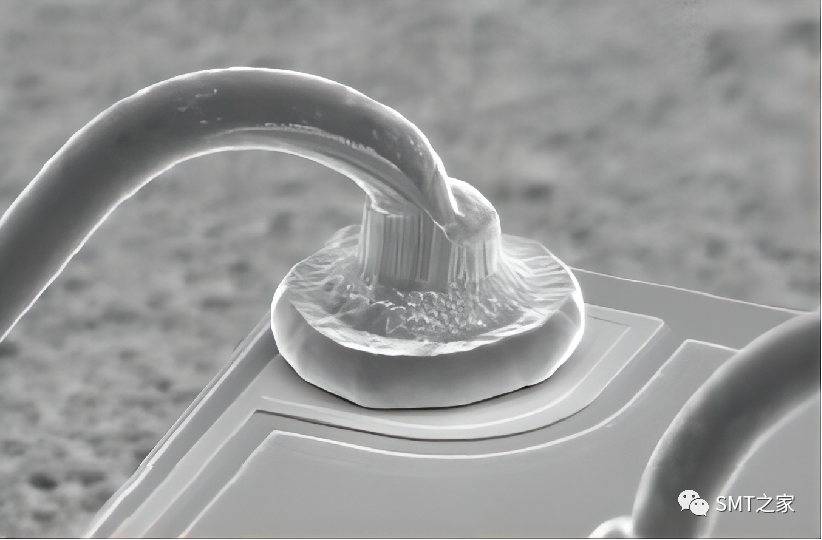

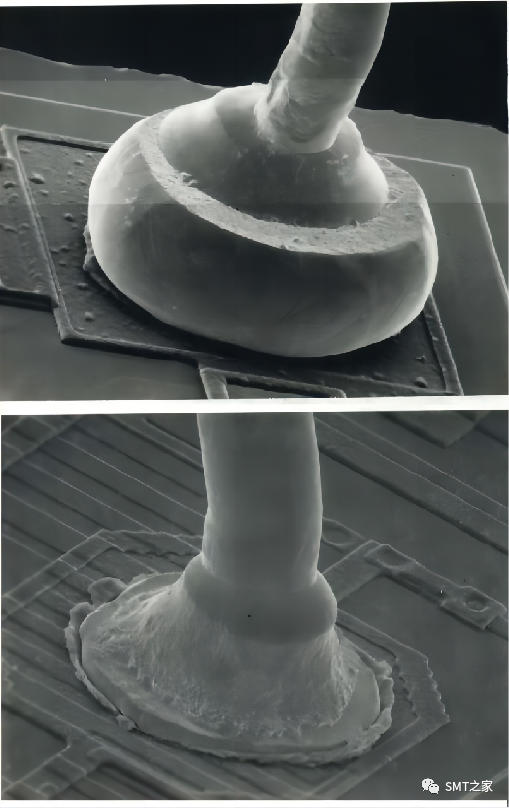

球形不良:球径大小不良,<2倍焊丝直径或>4倍 焊丝直径;特殊情况(压区尺寸小于常规 情况)下,球径<焊区单边边长的70%或>焊区单边边长为不良;

球厚度不良:压扁变形,球厚度<30%焊线直径或球厚度>70%焊线直径为不良

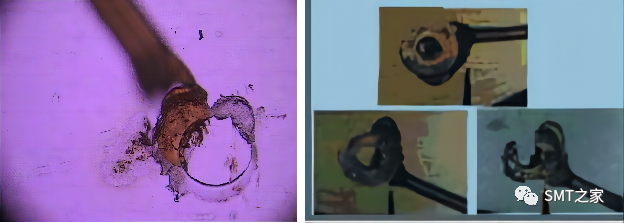

二焊点不良:第二焊点根部有撕裂或隐裂现象

二焊点不良:第二焊点根部有撕裂或隐裂现象

弧度不良:焊丝与芯片,引线框及其他焊丝的最短距离<2倍焊丝直径

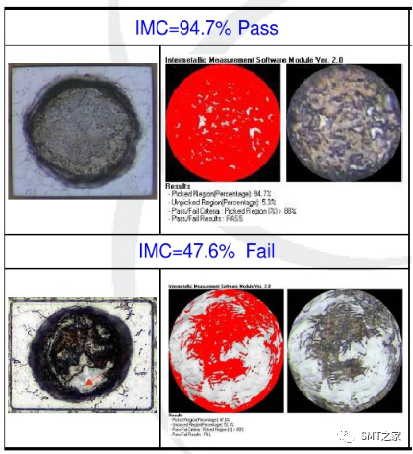

IMC Check

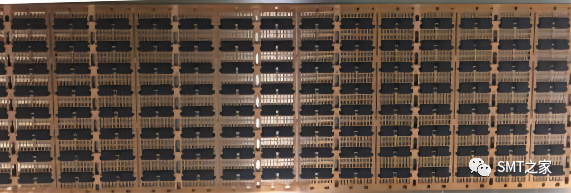

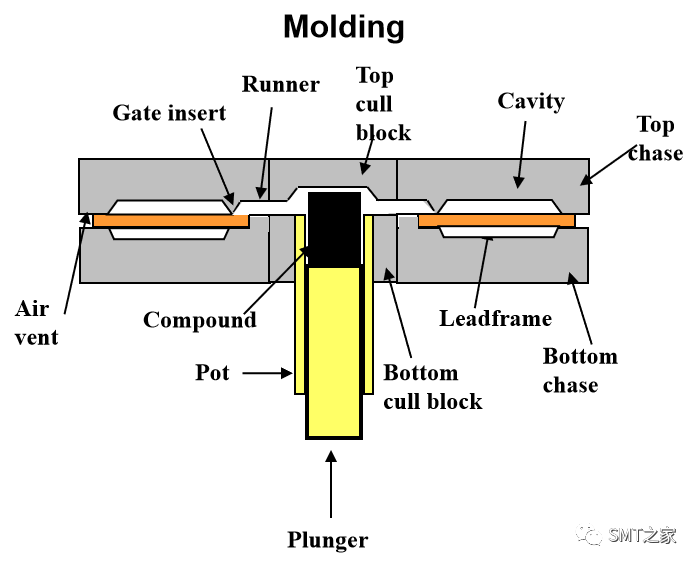

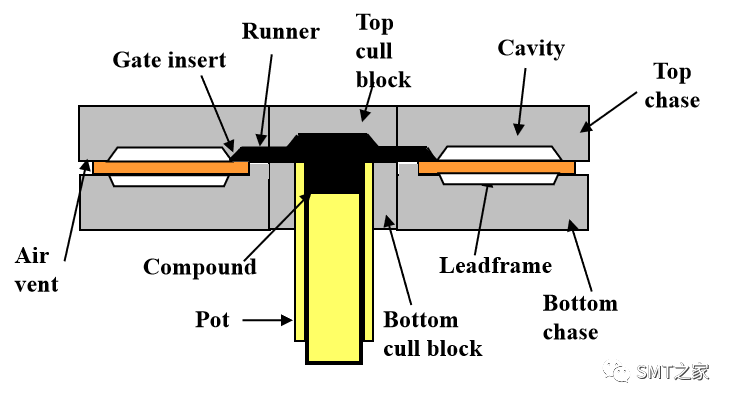

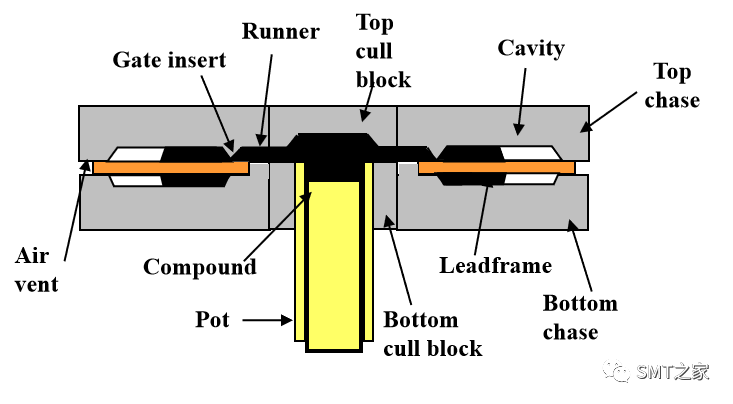

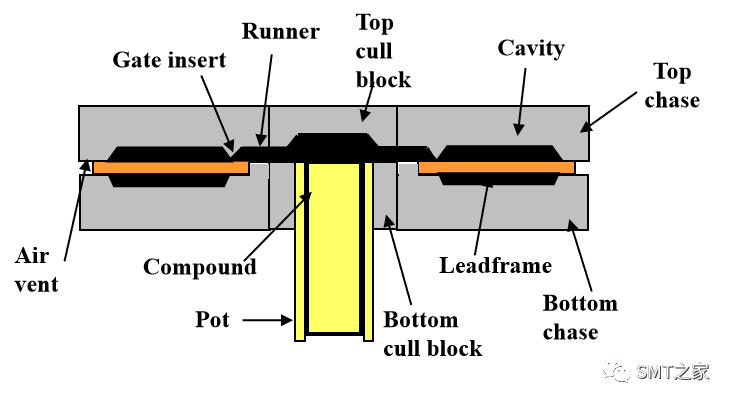

成型 Molding:

目的 Purpose:

Seal the product with EMC to prevent die, gold wire from being damaged, contaminated and oxygenic.

用电磁兼容性(EMC)对产品进行密封,以防止模具、金线被损坏、污染和氧化。

EMC为黑色块状,低温存储,使用前需先回温。其特性在高温下先处于熔融状态,然后会逐渐硬化,最终成型

|

Machine |

TOWA/ASM |

|

Material |

Compound |

|

Control |

MoldTemp;Clamppressure |

|

Transferpressure/time;Curetime |

|

|

Check |

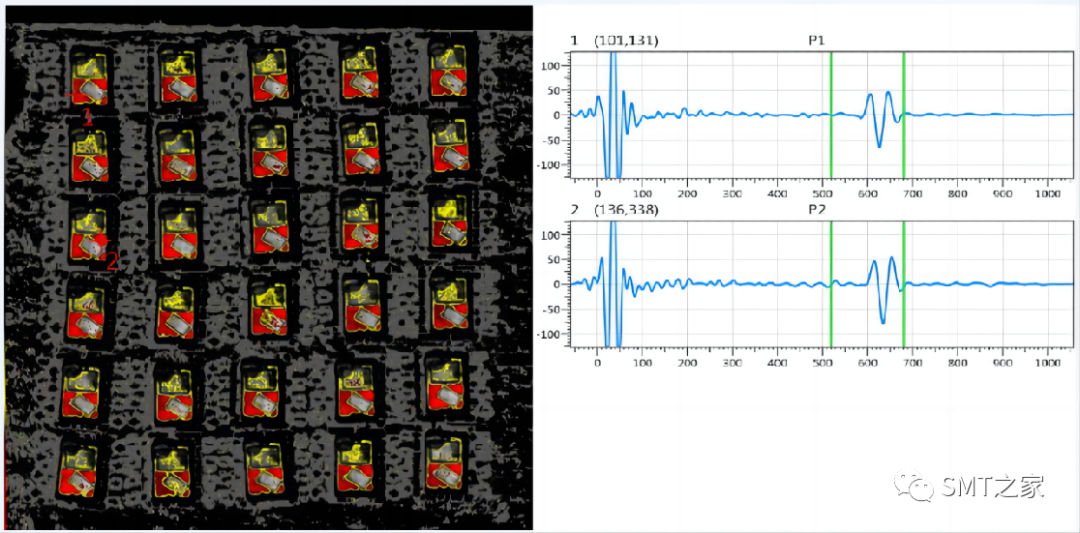

BodyThickness/WireCurvature |

|

Void/Delamination |

|

|

VisualInspection |

After Mold

After Mold

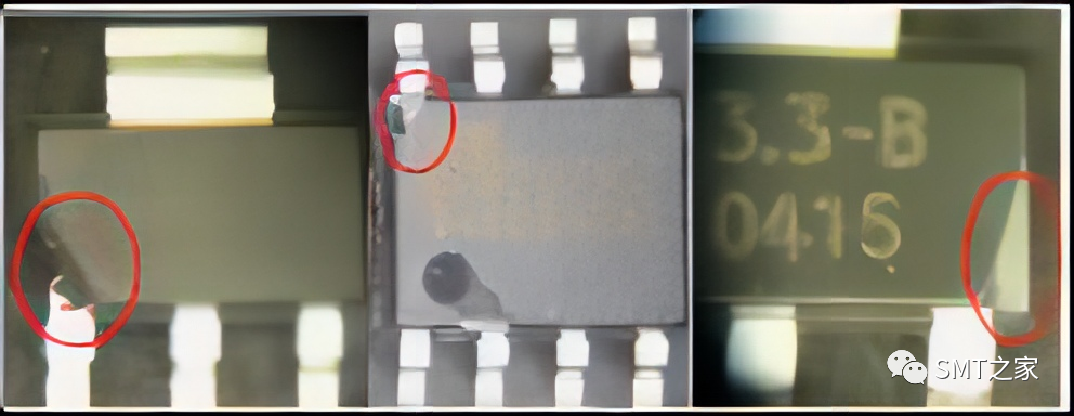

质量控制Quality Control:

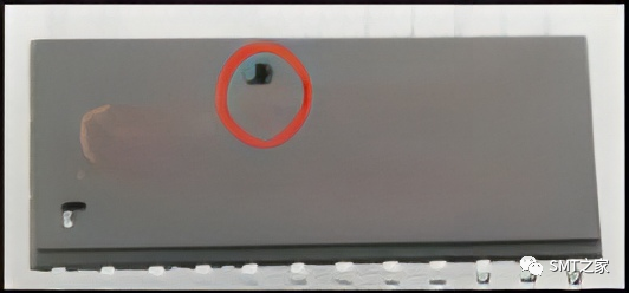

孔洞

孔洞

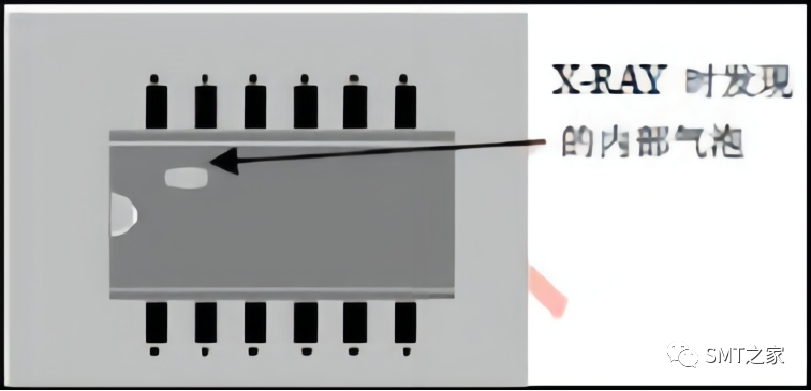

内部气泡

内部气泡

缺角

缺角

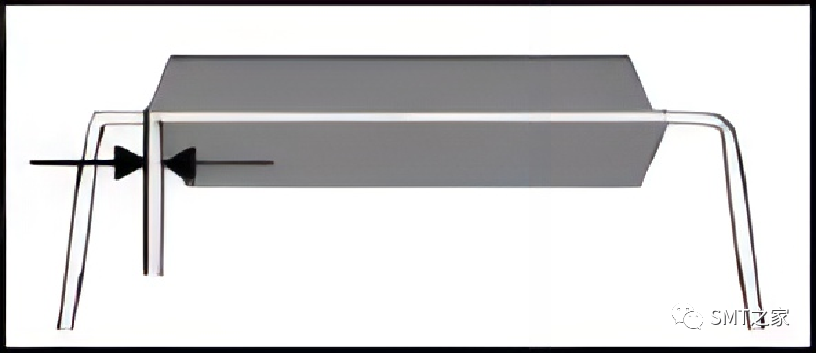

上下错位

上下错位

溢胶

溢胶

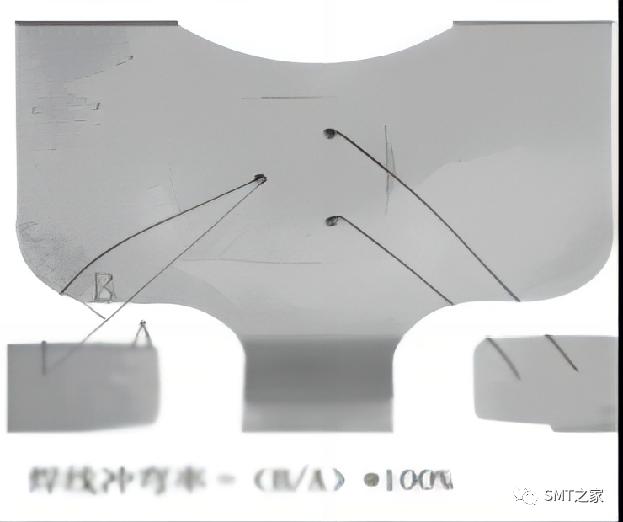

弧度不良:焊线冲歪率大于20%

弧度不良:焊线冲歪率大于20%

碰线不良:线与线的距离小于2倍线径、断线、接触芯片或外引脚

C-SAM 检查

C-SAM 检查

后成型固化 Post Mold Cure:

固化烤箱Oven

固化烤箱Oven

后固化目的:提高材料的交联密度;缓释制造应力。

后固化温度:通常在175度左右(接近Tg温度,分子链相对松弛;催化剂的活性较高。)

后固化时间:4-8H,通常恒温6H(后固化烘箱温度均匀性;后固化烘箱的升温速度。)

|

Machine |

C-Sun |

|

Material |

NA |

|

Control |

Curetemp. |

|

Curetime |

|

|

Check |

Profile |

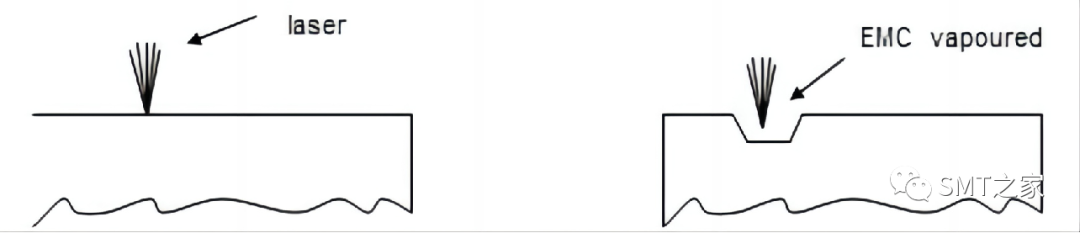

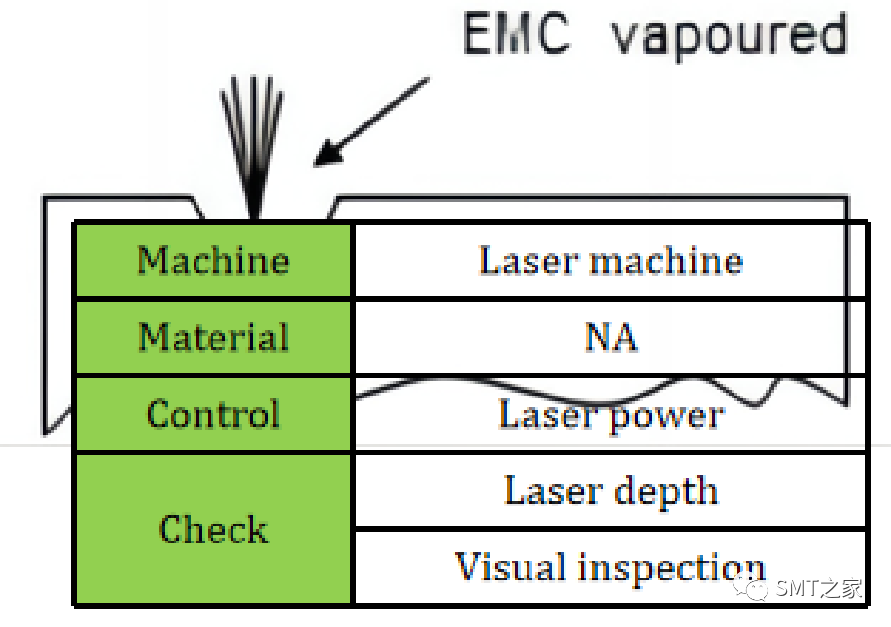

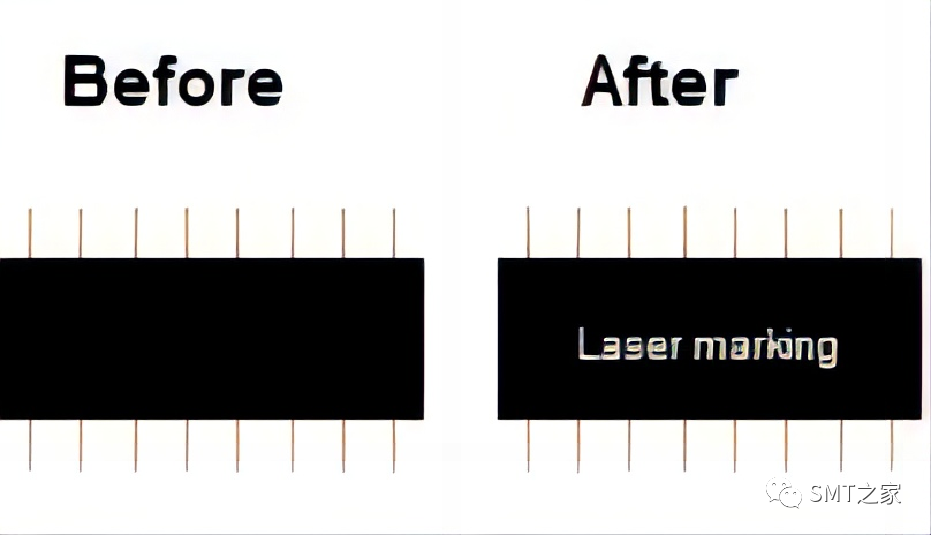

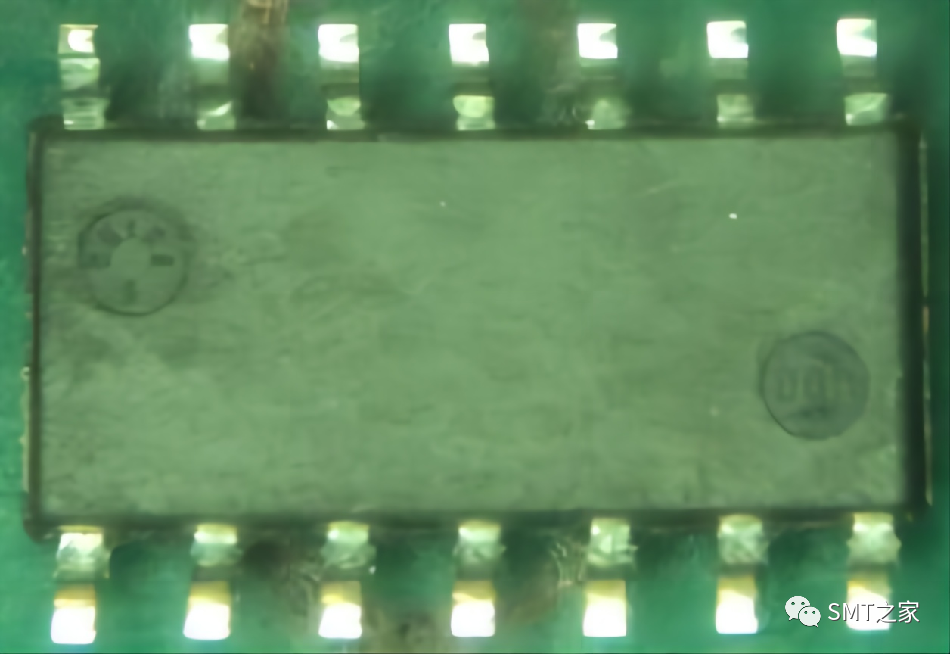

激光打标Laser Marking:

目的 Purpose:

Provide a permanent identification on product body

在芯片产品的本体上刻印上永久性标识

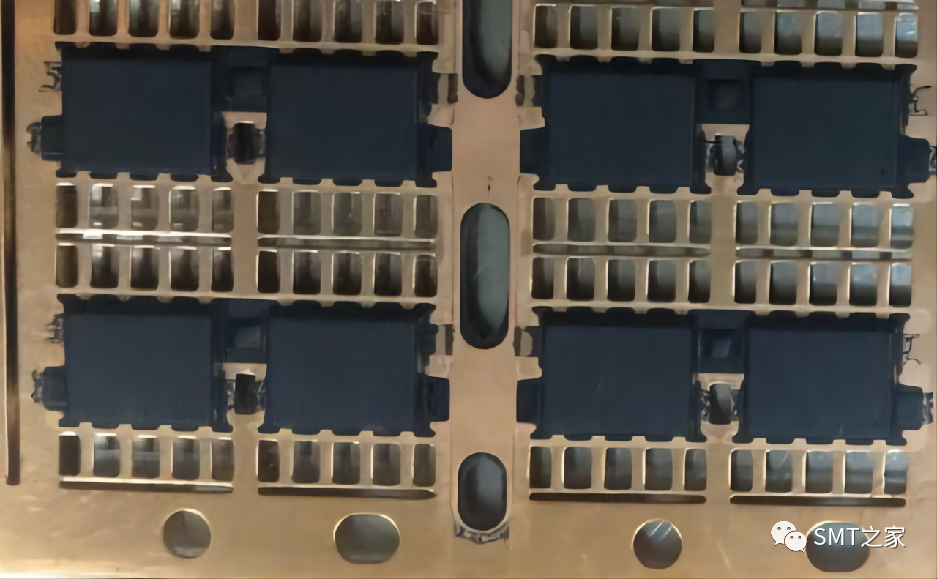

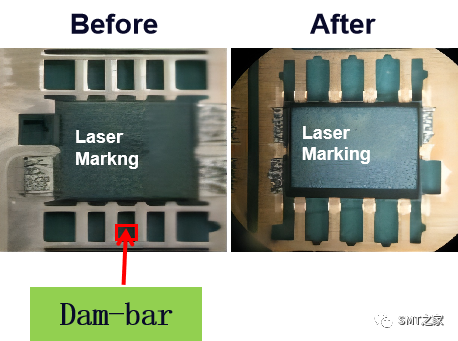

去除垃圾De-junk:

目的 Purpose:

Remove the dam-bar of leadframe

移除拆卸引线框的阻尼条

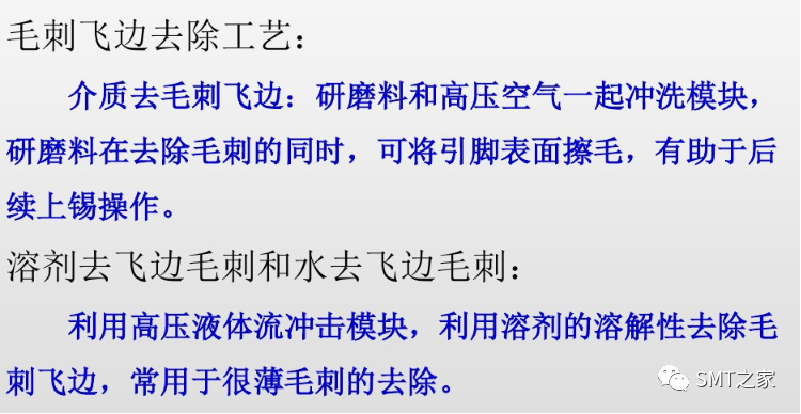

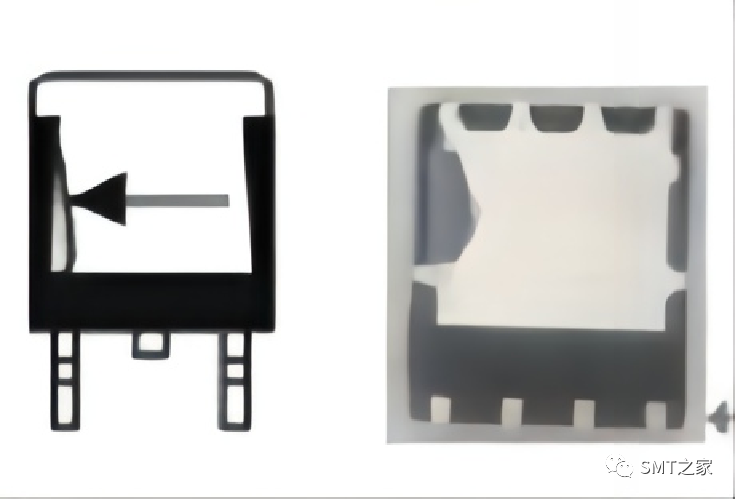

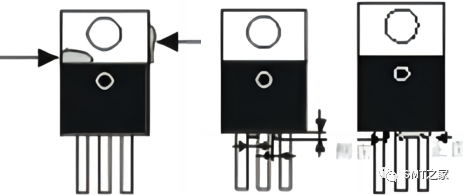

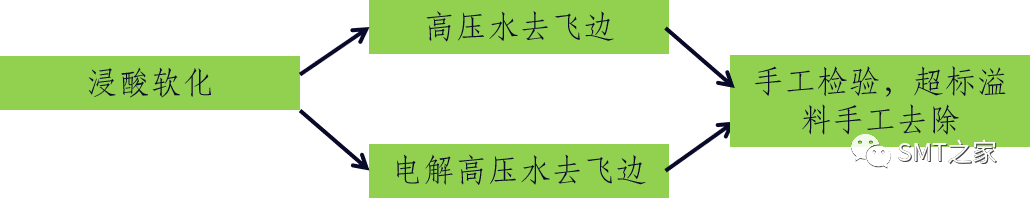

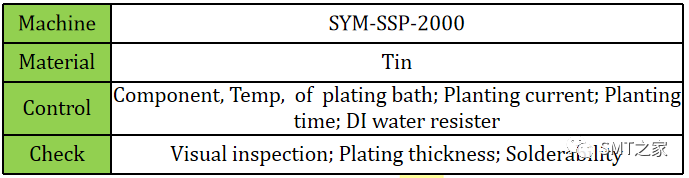

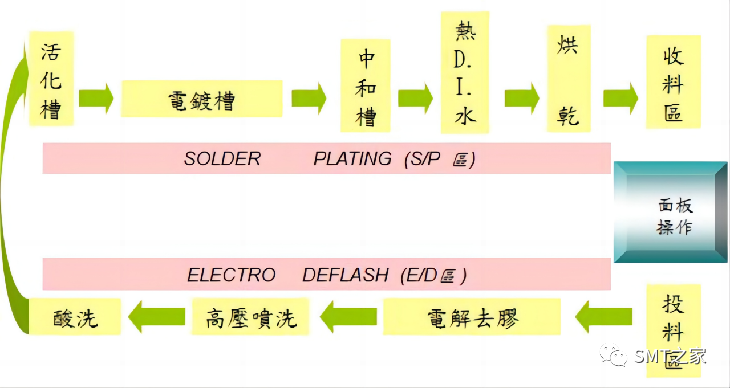

去除飞边 De-flash:

目的 Purpose:

Remove the residue of EMC around the package body and lead

清除封装本体和引线周围的EMC残留物

毛刺飞边是指封装过程中塑封料树脂溢出,贴带毛边,引线毛刺等飞边毛刺现象

控制项目:软化时间,软化液温度;电解电流,电解液浓度;高压水压力,传送速度

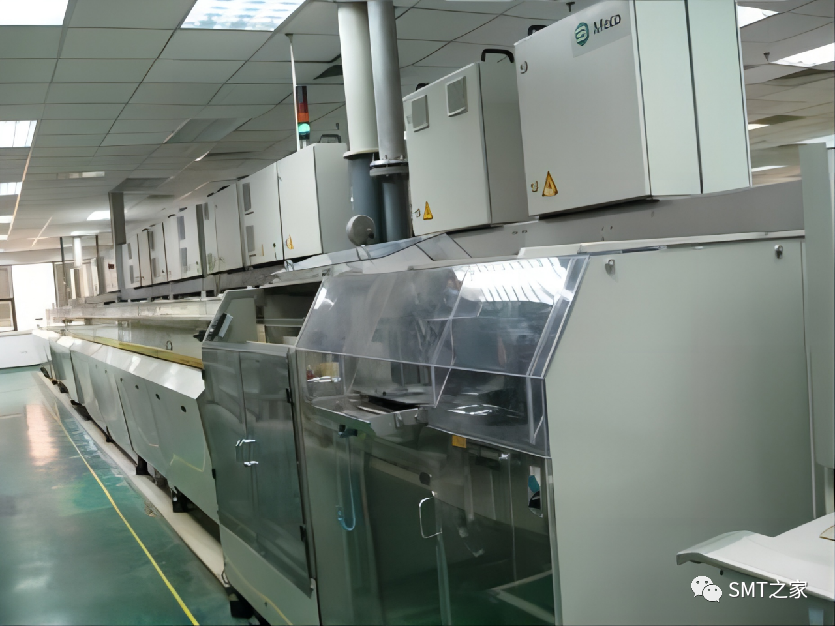

电镀 Plating:

Purpose:

To plating Sn on the lead which will mount on board pad.

利用金属和化学的方法,在框架表面镀上一层镀层,以防止外界环境的影响(潮湿和热),并使元器件在PCB板上容易焊接及提高导电性。

电镀两种类型:

Pb—Free:无铅电镀,锡(Tin)的纯度>99.95%,符合Rohs的要求;

Tin-Lead:铅锡合金。Tin占85%,Lead占15%,由于不符合Rohs,目前基本被淘汰。

(电镀退火)Baking after plating:

目的:让无铅电镀后的产品在高温下烘烤一段时间,以便消除电镀层潜在的锡须生长(Whisker Growth)的问题。

条件:150+/-5C;2Hrs

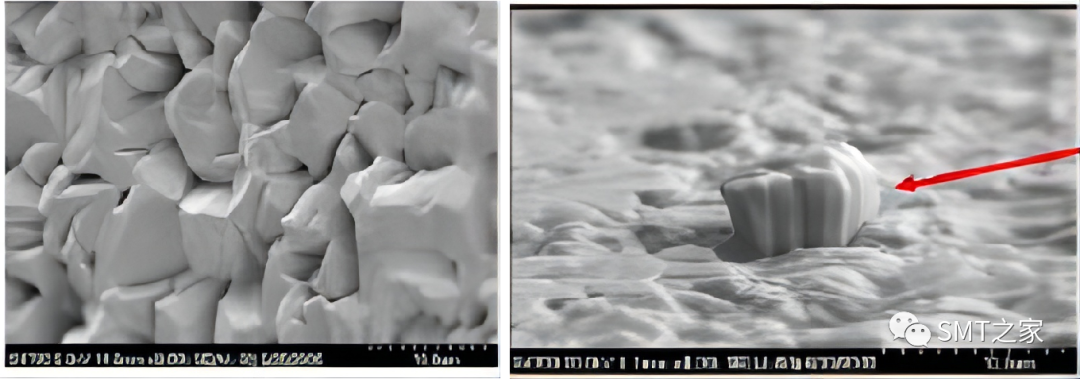

晶须(Whisker),是指锡在长时间的潮湿环境和温度变化的环境下生长出的一种须状晶体,可能导致产品引脚的短路。

晶须(Whisker),是指锡在长时间的潮湿环境和温度变化的环境下生长出的一种须状晶体,可能导致产品引脚的短路。

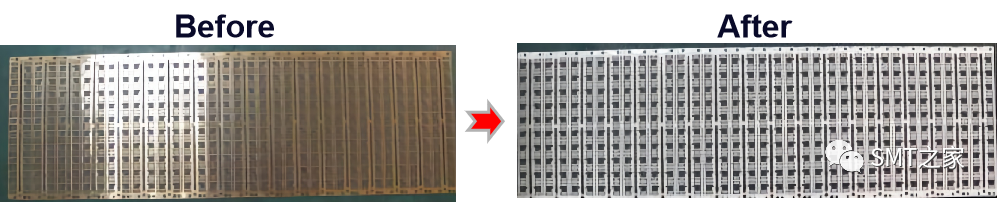

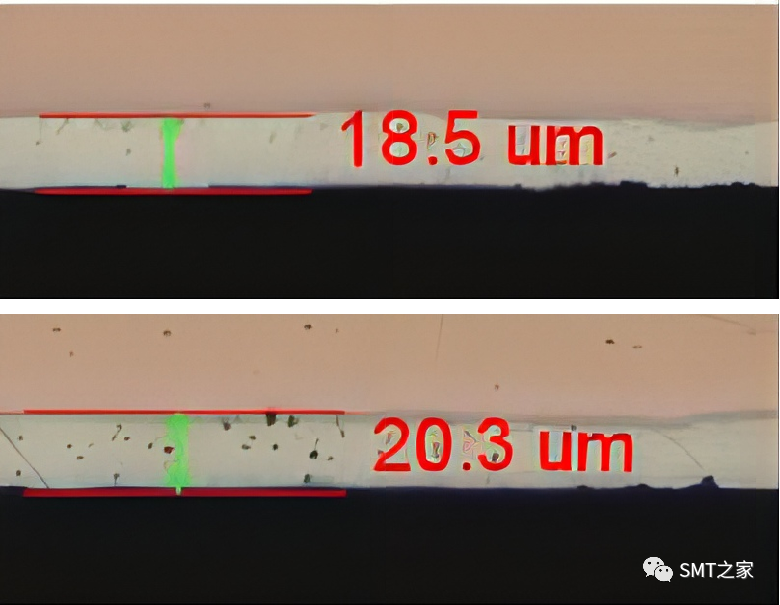

质量控制Quality Control:

外观检查

外观检查

镀层厚度量测

镀层厚度量测

可焊性测试Solderability test

可焊性测试Solderability test

Preconditioning: Steam aging 93℃+3℃/-5℃, 8 hrs

Solder dip: SnAgCu 245℃±5℃, 5±0.5s

solder coverage≥95%

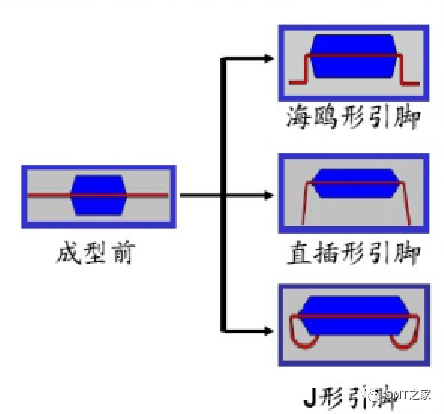

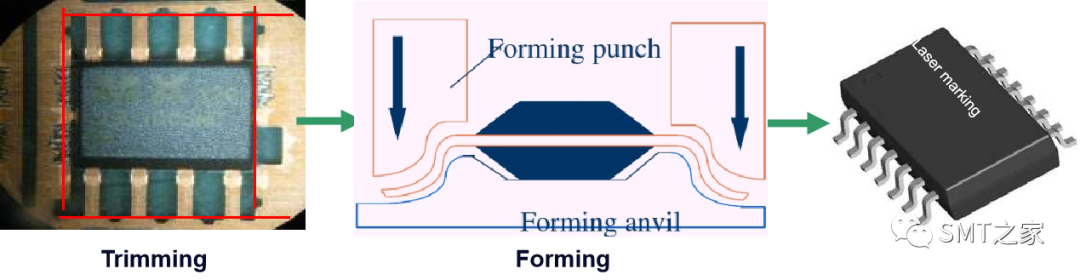

修形Trim Form:

Purpose:

Remove the tie-bar and lead-frame and form products to units from strips, fill them into tubes and then pass to next process.

拆下拉杆和引线框架,将带材成型成件,装入管材,然后进入下一道工序。

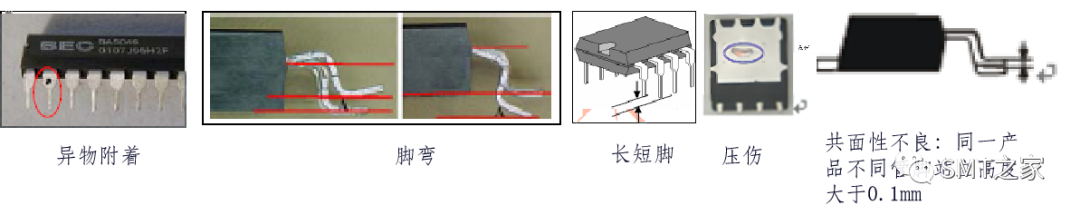

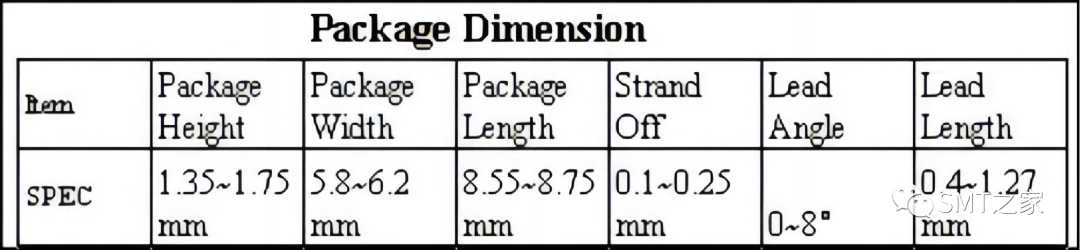

质量控制 Quality Control:

外观检查

外形尺寸量测:

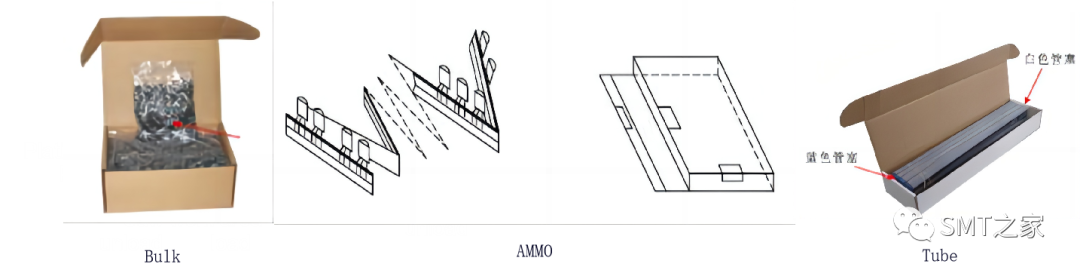

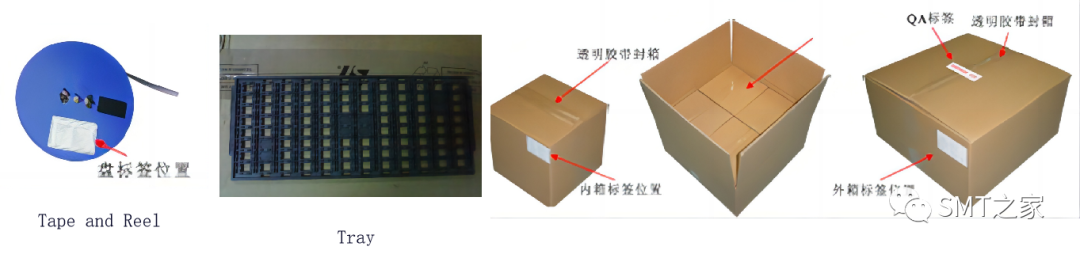

包装 Packing:

目的 Purpose:

Protect the product in the circulation process, convenient storage and transportation

保护产品在流通过程中,方便储运

审核编辑 :李倩

-

芯片

+关注

关注

453文章

50360浏览量

421625 -

晶圆

+关注

关注

52文章

4835浏览量

127760 -

Wafer

+关注

关注

0文章

19浏览量

5758

原文标题:Wafer晶圆半导体工艺介绍

文章出处:【微信号:半导体封装工程师之家,微信公众号:半导体封装工程师之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Wafer晶圆半导体工艺介绍

Wafer晶圆半导体工艺介绍

评论