当设计存在多个时钟时,根据时钟的相位和频率关系,分为同步时钟和异步时钟,这两类要分别讨论其约束

1、同步时钟

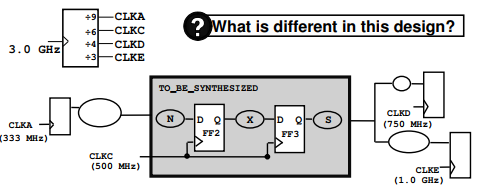

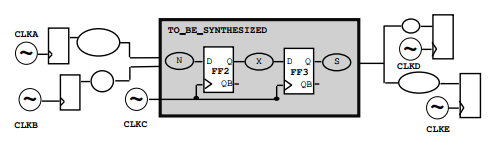

考虑分频器产生的各个时钟,它们来源于同一个晶振,受主时钟调配。如下图所示,由3GHz的时钟进行9、6、4、3分频产生clka,clkc,clkd,clke。

为了约束我们设计的逻辑N,X和S,需要给出clkc的周期、逻辑N的外部延时,逻辑S的外部延时。

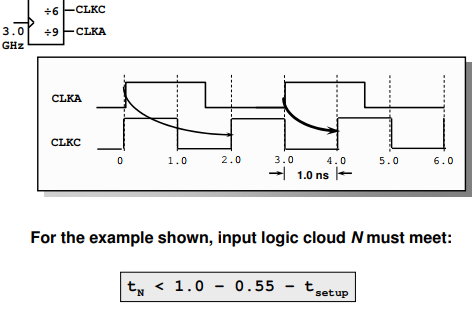

对于逻辑N而言,由clka产生数据,clkc采样数据,在它们周期的最小公倍数内,最严格的时序是3ns产生数据,在4ns采样。只要保证最严格的情形下,电路正常工作,其他时候都没问题

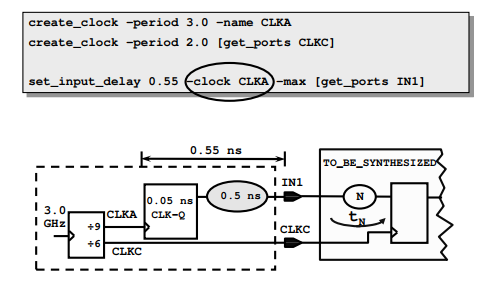

当我们写时序约束时,只需要创建时钟,其中clka为虚拟时钟,然后set_input_delay通过-clock指定产生数据的时钟,给出clka产生的数据延时(触发器+组合逻辑)

可见,写约束还是更简单,计算由时序分析工具处理。我们要提供产生数据的时钟和数据延时即可

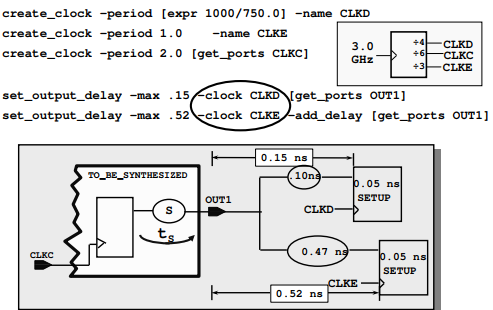

对于输出数据,可以驱动多个单元。如下图所示,clkc的输出OUT1会经过组合逻辑被clkd和clke采样。设置约束,同样创建外部的虚拟时钟,然后set_output_delay,指定采样时钟和外部延时。另外,增加-add_delay选项避免被覆盖,表示让时序工具计算两条约束,选择更严格的进行分析

在DC中,所有时钟都是同步的,即create_clock并不能创建异步时钟,异步电路静态时序分析不适合。

2、异步时钟

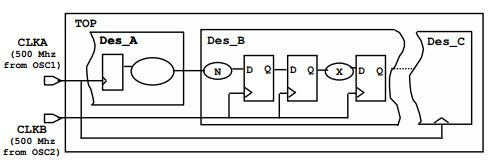

考虑不同时钟源的电路,由于每个时钟源独立工作,它们诸如延迟、转换时间等不一定一致,时钟之间的相位不固定,表现出异步电路。

异步电路要减少亚稳态产生,是设计者负责亚稳态处理,别指望工具帮助处理。我们需要在每个时钟域内约束路径,然后告诉工具不要检查跨时钟域路径。(否则工具会努力让该路径满足要求,导致浪费时间)

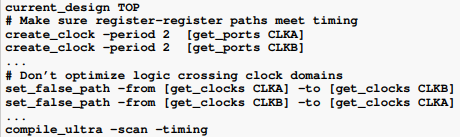

下图中,clka驱动的数据被clkb采样。很显然,两个不同时钟的触发器之间的路径都要告诉工具不要检查。

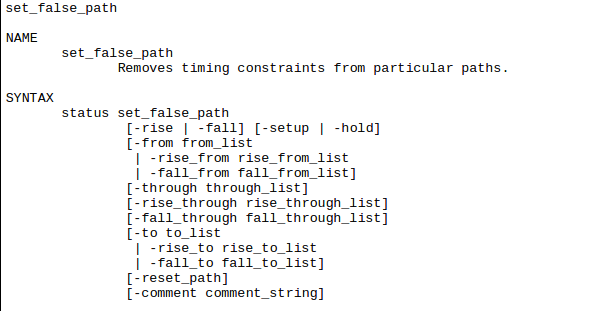

DC中,使用set_false_path告诉工具不要在指定的路径分析

通过-from指定路径起点,可以是clock、port、pin和cell,clock作为起点,所有和该clock有关的路径都会被影响。通过-to指定路径终点,类似于from。

约束如下,使用-from clock能够简化,不用将路径一一列举。

审核编辑 :李倩

-

分频器

+关注

关注

43文章

447浏览量

49997 -

时序

+关注

关注

5文章

389浏览量

37358

原文标题:时序约束--多时钟

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA主时钟约束详解 Vivado添加时序约束方法

时序约束--多时钟

时序约束--多时钟

评论