大型时钟树使用多种类型的传输线,跨越多块电路板和多条同轴电缆,通过多个时钟器件路由时钟信号的情况并不少见。即使采用最佳实践做法,这些介质中的任何一种都可能带来大于10ps的相位偏差。然而,在一些应用中,需要所有时钟信号实现小于1ps的偏差。其中一些应用包括相控阵、MIMO、雷达、毫米波成像、微波成像、仪表和软件定义无线电(SDR)。

本文指出了设计过程、制造过程和应用环境中可能导致1ps或以上相位偏差的几个关切问题。对于这些关切问题,本文将提供一些建议、示例和经验法则,帮助读者直观地了解相位偏差的根本原因和幅度。

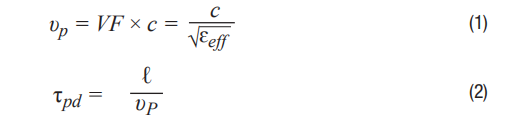

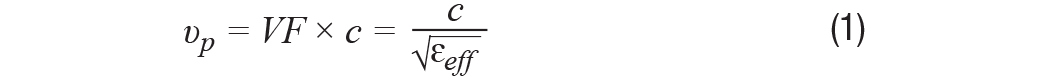

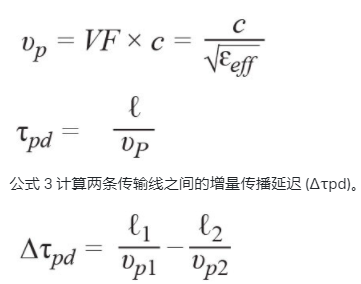

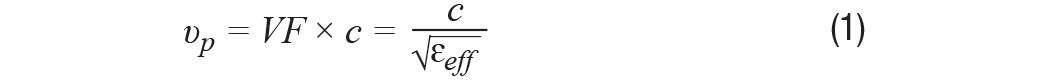

传输线的延迟等式

这里列出的等式用于估算单个时钟路径的传播延迟(τpd)和由于多个时钟传播途径或环境条件变化导致的传播延迟的变化值在大型时钟树应用中,时钟走线之间的∆τpd是总系统时钟偏移的一部分。等式1和等式2提供了两个主变量,它们用于控制一条传输线的τpd:传输线的物理长度(ℓ)和有效介电常数(Ɛeff)。对于等式1,vp表示传输线相速度,VF表示速度因子(%),c表示光速(299,792,458 m/s)。

等式3计算两条传输线之间的增量传播延迟(∆τpd)。

传输线介电材料具有随温度而变化的特性。介电常数的温度系数(TCDk)通常用相位变化(Δϕppm)与温度的关系曲线表示,单位为百万分之一(ppm);其中Δϕppm值为目标温度下的相位与基准温度(通常为25°C)下的相位的差值。已知温度,Δϕppm和传输线长度时,等式4用于估算传播延迟相对于基准温度的变化。

同轴电缆介电材料具有因电缆弯曲而改变的特性。电缆弯曲的半径和角度决定了有效介电常数的变化。一般地,通过比较特定电缆弯曲的相位与直线电缆的相位,将其表示为相位的变化(Δϕdeg)。对于已知Δϕdeg、信号频率(f)和电缆弯曲,等式5用于估算传播延迟的变化。

延迟变化注意事项

传输线的选择

建议:为了在多条走线之间获得最佳延迟匹配效果,就要匹配走线长度和传输线类型。

经验法则:

两条走线长度之间相差1mm,就相当于∆τpd ~6ps(两个走线长度之间相差6mil就相当于∆τpd~1ps)。

带状线比微带线或导体背衬的共面波导(CB-CPW)慢约1ps/mm。

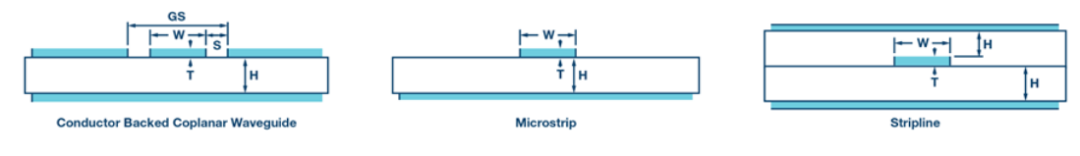

不同的传输线类型会产生不同的Ɛeff和vp。使用等式2,这意味着物理长度相同的不同传输类型则有不同的τpd。表1和图1提供了三种常见传输线(CB-CPW、微带线和带状线)的仿真结果,凸显了Ɛeff、vp和τpd之间的差异。该仿真估算得到,对于10厘米的CB-CPW走线,τpd比相同长度的带状线走线大100ps。仿真是用Rogers Corporation的微波阻抗计算器(Microwave Impedance Calculator)生成的。

图1. 匹配传输线类型。

表1. 图1中的Rogers 4003C仿真结果

Rogers 4003C的相对磁导率(Ɛr),也称为介电常数(Dk),为3.55。注

意,在表1中,CB-CPW和微带线的Ɛeff较低,因为它们暴露在空气之下,而空气的Ɛr=1。

要在同一层或者用同一种类型的传输线来对那些要求延时匹配的信号进行走线并不是总能实现的。表2提供了在为不同走线选择传输线类型时需要考虑的一些通用因素。如果需要匹配不同传输线类型的τpd,最好使用电路板仿真工具而不是手动计算和经验法则。

表2. 广义传输线的考虑因素

传输线过孔

建议:如果信号路径有过孔,请记住在计算传播延迟时,要考虑两个目标信号层之间的过孔长度。

若只是粗略计算传播延迟,假设连接两个信号层的过孔长度在相位速度上与传输线相同。例如,连接62mil厚板的顶部和底部信号层的过孔将占额外的τpd~10ps。

相邻走线、差分信号和单端信号

建议:在走线之间保持最少一个线宽度,避免在Ɛeff出现显著变化。

经验法则:

100Ω差分信号(奇模式)比50Ω单端信号快。

密集的同相50Ω单端信号(偶模式)比单个50Ω单端信号慢。

密集相邻走线的信号方向会改变Ɛeff,并且因而会改变等长走线之间的延迟匹配。图2和表3中提供了两个边缘耦合微带线走线与单个微带线走线的仿真情况。该仿真估计,两个10厘米边缘耦合偶数模式走线的τpd比等长独立单个走线大16ps。

图2. 相邻走线与隔离走线

表3. 相邻走线与隔离走线

当尝试将单端τpd与差分τpd匹配时,重要的是仿真两条路径的相位速度。在时钟应用中,当尝试发送与差分参考或时钟信号时间对齐的CMOS同步或SYSREF请求信号时,可能会出现这种情况。增加差分信号路径之间的间隔会在差分信号和单端信号之间产生更接近的相位速度匹配。然而,这是以差分信号的共模噪声抑制为代价的,后者的作用是使时钟抖动保持在最小限度。

同样重要的是,我们需要指出,密集的同相信号(偶数模式)会增大Ɛeff,从而导致τpd变长。当单端信号的多个副本密集走线时,结果就会发生这种情况。

延迟匹配与频率的关系

建议:为了最大限度地减少频率相关延迟匹配误差,请选择低Dk、低损耗因子(DF)的材料(Dk<3.7, DF<0.005)。DF也称为损耗角正切(tan δ)见等式6)。对于多GHz走线,请避免使用含镍的电镀技术。

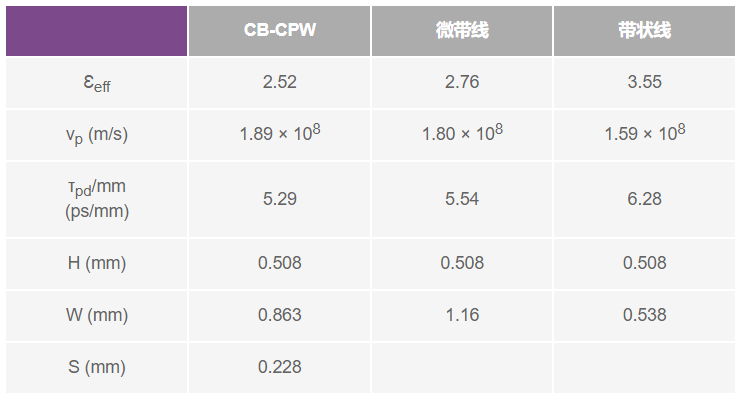

通过抵消变化量,将不同频率将信号之间的延时匹配到ps水平并非易事。图3显示随着频率的增加,介电常数通常会降低。基于上面的等式1和等式2,随着频率的增加,这种行为产生的τpd会变小。基于等式3和图3中的Roger材料,1在10厘米走线上,1GHz与20GHz正弦波之间的∆τpd约为4ps。

图3. Dk和DF与频率的关系。

图3同时显示,信号衰减随着频率的增加而增加,与基音相比,导致方波高阶谐波衰减增大。这种滤波的程度会导致上升时间(τR)和下降时间(τF)的不同。上升时间和下降时间的变化会表现在波形上的变化影响后继接受器件,从而体现在总的时延参数上,总延迟由走线的τpd和信号的τR/2或τF/2构成。另外,不同频率的方波也可能具有不同的群延迟。由于这些原因,在估计不同频率之间的延迟匹配时,方波比正弦波更具挑战性。

为了更好地理解衰减(以dB/ft为单位的α)与频率的关系,请参考等式7和等式8以及本文中提供的参考资料2,3,4,5,其中引入了损耗角正切(δ)和集肤效应。这些参考文献的一个关键点是集肤效应减小了等式8中的面积(A),结果增大了线路电阻(R)。3 为避免高频集肤效应引起过度衰减,请不要使用镀镍技术,例如镀金焊料掩模(SMOG)电镀技术和化学镀镍浸金(ENIG)电镀技术。4,5 避免使用镍的电镀技术的一个例子是裸铜焊料掩模(SMOBC)技术。总而言之,选择低Dk/DF的材料,避免使用镍的电镀技术,并在关键走线上进行电路板级延迟仿真,从而改善不同频率的延迟匹配。

延迟匹配与温度的关系

建议:为PCB和电缆选择温度稳定的介电材料。温度稳定型介电材料的Δϕppm通常小于50ppm。

介电常数随温度变化,导致传输线τpd的变化。等式4计算由于温度变化导致的介电常数变化从而引起的时延的变化∆τpd。

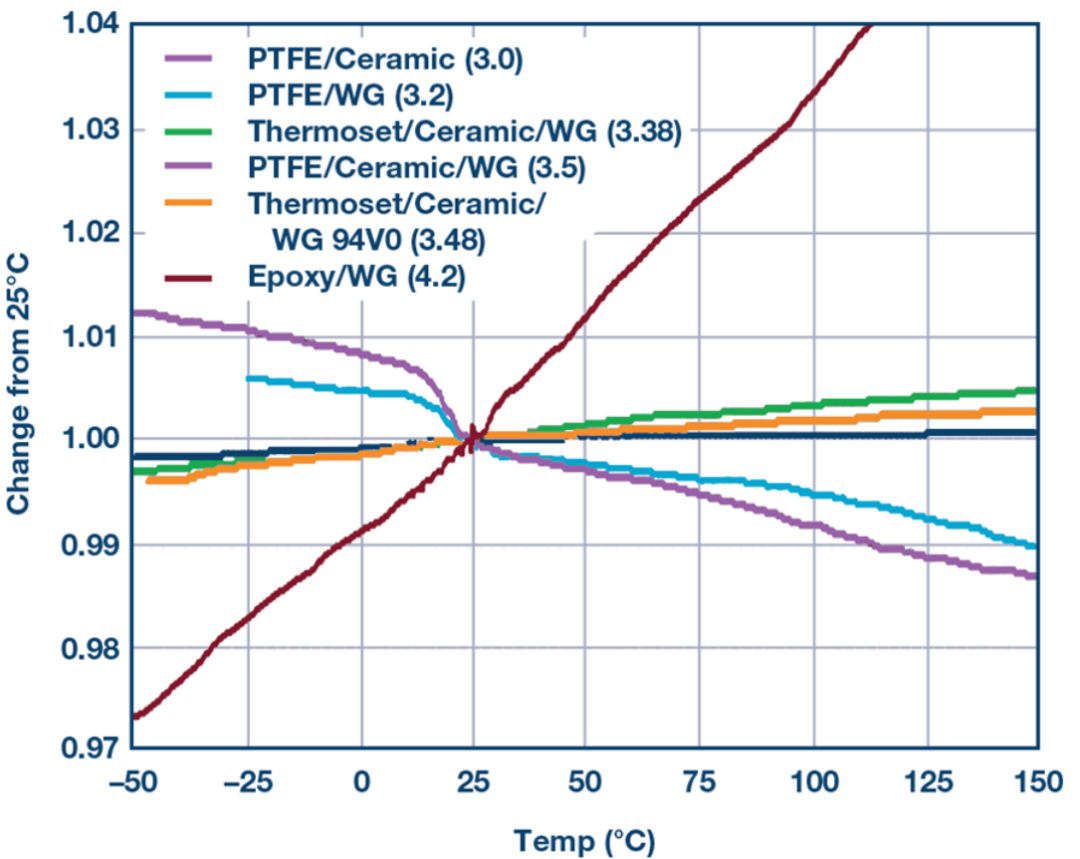

通常,PCB材料分为两类:玻璃纤维织物(WG)和无纺玻璃。由于玻璃的Dk=6,因此玻璃纤维通常更便宜并且Dk更高。图4比较了各种不同材料的Dk变化。图4显示,一些基于PTFE/WG的材料在10°C和25°C之间的TCDk比较陡峭。

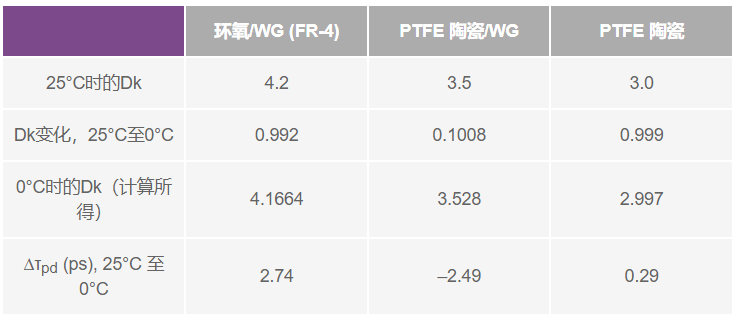

使用等式3和图4,表4计算出了不同PCB材料上10厘米带状线走线在温度于25°C至0°C之间变化时的∆τpd。在需要在不同温度下跨多条走线匹配τpd的系统中,PCB材料的选择可能在10厘米走线之间导致几皮秒的τpd失配。

图4. Dk变化与温度的关系。

表4. 10厘米带状线的Δτpd,25°C至0°C

同轴电缆介电材料也有类似的TCDk问题。同轴电缆通常比PCB走线长得多,这将在整个温度范围导致大得多的∆τpd。当温度从25°C变为0°C时,使用与表4第2列所示属性相同的两根1米电缆可能会产生25ps的τpd失配。

表4假设走线长度为10厘米时,温度恒定不变。在实际情况中,温度在整条走线或同轴电缆上可能并不恒定,使得分析比上面讨论的情况要复杂一些。

延迟匹配电缆

建议:了解购买延迟匹配电缆与开发校准程序以通过电子方式调整延迟失配这两种方式之间的成本权衡关系。

根据笔者的经验,比较同一供应商提供的相同长度和材料的同轴电缆,可以发现延迟失配在5ps至30ps之间。从与电缆供应商的讨论来看,这一变化范围是电缆切割、SMA安装和Dk批次之间变化的结果。

许多同轴电缆制造商在提供相位匹配电缆,其预定匹配延迟窗口为1ps、2ps或3ps。随着延迟匹配精度的增加,电缆的价格通常也会增加。为了制造延迟匹配<3ps的电缆,制造商通常会在电缆制造过程中增加若干延迟测量和电缆切割步骤。对于电缆制造商而言,这些增加的步骤会导致制造成本增加并降低产量。

延迟匹配与电缆弯曲

建议:在选择电缆材料时,要了解由于温度引起的延迟偏移与电缆弯曲引起的延迟偏移之间的权衡关系。

弯曲同轴电缆会导致不同的信号延迟。电缆供应商的数据手册通常会规定特定弯曲半径和频率下弯曲90°时的相位误差。例如,在频率为18GHz、弯曲角度为90°时,额定相位变化可能为8°。使用等式5,计算得到的延迟大约为1.2ps。

延迟匹配与SMA的安装和选择

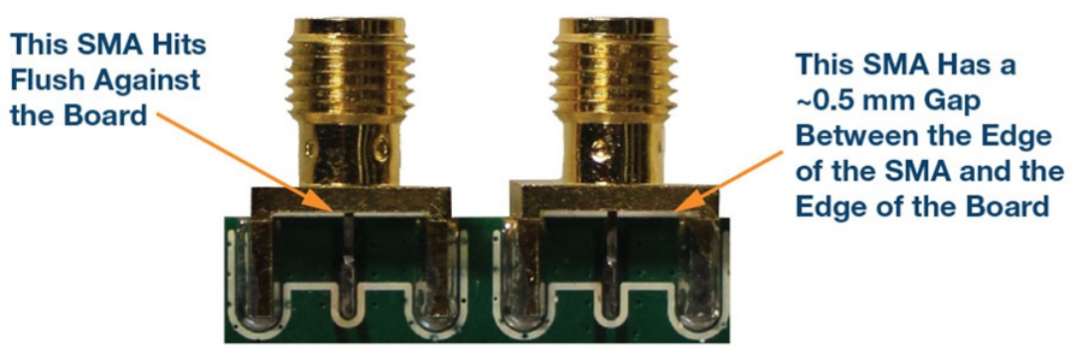

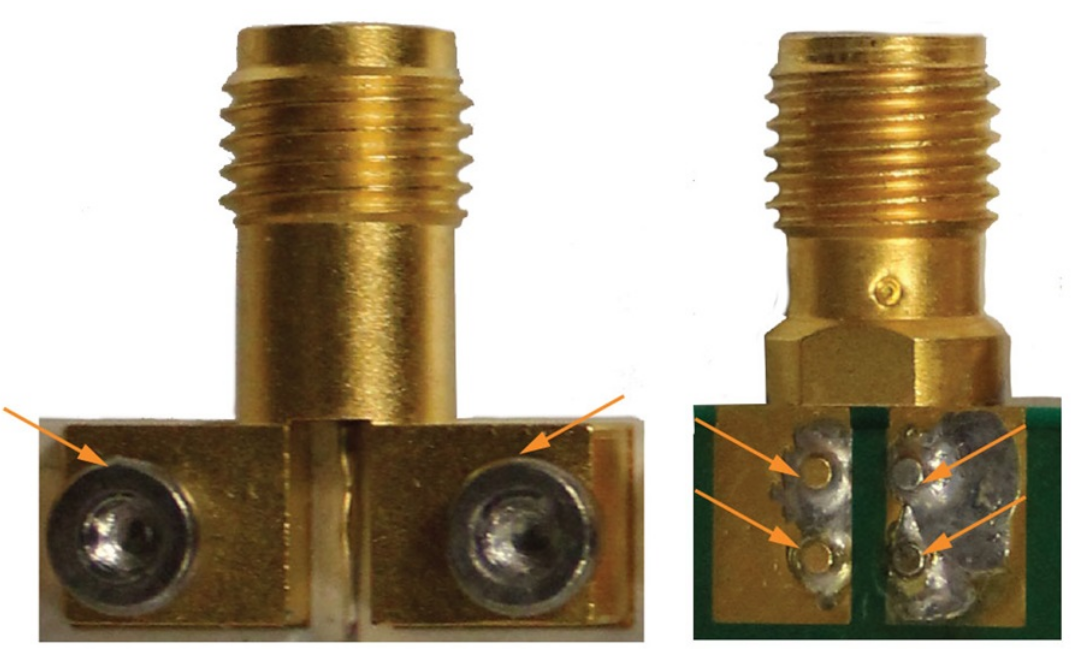

PCB边缘安装SMA在安装时的变化会增加时钟路径之间的延迟失配,如图5所示。通常不会测量这种性质的误差,因此很难量化。但是,我们可以合理地假设,这可能会在时钟路径之间增加1ps至3ps的延迟失配。

图5. SMA安装延迟失配。

控制SMA安装引起的延迟失配的一种方法是选择具有对齐特性的SMA,如图6所示。由于具有对准特性的SMA的额定频率通常高于没有对准特性的SMA,因此成本更高,二者之间存在折衷。SMA供应商经常为更高频率的SMA提供推荐的PCB到SMA发射板布局。该推荐的布局本身就有可能值得付出额外的代价,因为这样就可以节省电路板修订成本,当时钟频率大于5 GHz时,尤其如此。

图6. 具有对齐特性的SMA

跨多个PCB的延迟匹配

建议:了解购买批次间Ɛr控制良好的PCB材料与开发校准程序以通过电子方式调整延迟失配这两种方式之间的成本权衡关系。

试图在多块PCB上的走线之间匹配τpd会增加若干误差源。上面讨论了四个误差源:延迟匹配与温度;延迟匹配电缆;延迟匹配与电缆弯曲;以及延迟匹配与SMA的安装和选择。第五个误差源是Ɛr在多个PCB上因工艺导致的变化。联系PCB制造商,以了解Ɛr的工艺变化。

作为一个例子,FR-4的Ɛr可能在4.35到4.8之间变化。6对于不同PCB上10厘米长的带状线走线,在极端情况下,该范围会产生高达35ps的∆τpd。其他PCB的材料数据手册提供的Ɛr典型范围更小。例如,Rogers 4003C的数据手册称,其Ɛr的范围为3.38±0.05。对于不同PCB上的10厘米带状线走线,在极端情况下,该范围会将可能的∆τpd降至9 ps。

时间IC导致的相位偏差

建议:考虑偏差调整幅度<1ps的新型PLL/VCOIC。

过去,数据转换器时钟是从多个输出时钟器件生成的。这些时钟器件的数据手册规定了器件的相位偏差,范围通常为5ps至50ps,具体取决于所选的IC。据笔者所知,在拟定本文时市场上的所有多输出GHz时钟IC都不具备对每个输出调整时钟延迟的能力。

随着大于6GHz的数据转换器时钟频率不断普及,单输出或双输出PLL/VCO将成为首选时钟。单输出PLL/VCO时钟IC架构的优势在于,人们正在开发一些方法,以便以<1ps的步长调整参考输入到时钟输出的延迟。对每个时钟调整参考输入到输出的延迟,这种能力允许最终用户执行系统级校准,将相位偏差最小化到1 ps以下。这种系统级相位偏差校准有可能降低本文中缓解的所有PCB、电缆和连接器延迟匹配问题,从而降低系统的整体BOM成本。

结 论

本文讨论了可能延迟变化和延迟失配的几种来源。讨论表明,Ɛeff可能随温度、频率、工艺、传输线类型和线路间距而变化。同时表明,通过同轴电缆连接的多PCB设备会产生额外的延迟变化源。当选择材料以最小化大时钟树的相位偏差时,我们必须了解PCB和电缆Ɛr随温度、工艺和频率而变化的规律。对于所有这些变量,如果没有某种偏差校准,很难设计出偏差<10 ps的大时钟系统。此外,购买PCB材料、同轴电缆和SMA连接器以最大限度地减少相位偏差会显著增加材料成本。为简化校准方法并降低系统成本,IC制造商提供的许多新型PLL/VCO和时钟器件可实现低于1ps的延迟调整能力。

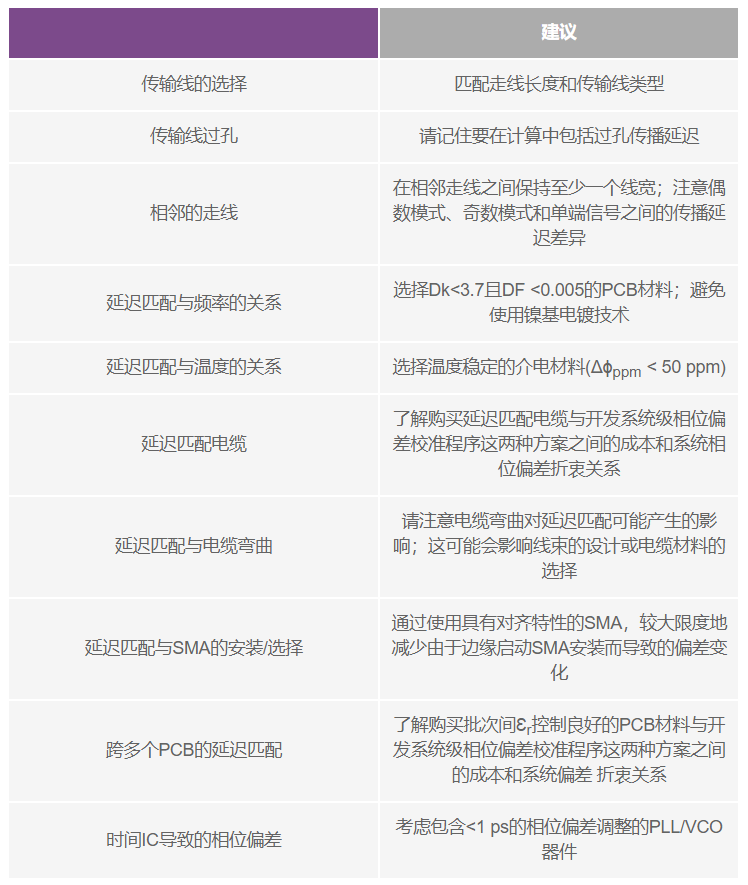

表5.总结了本文针对最小化相位偏差而讨论的建议

审核编辑:汤梓红

-

雷达

+关注

关注

50文章

2936浏览量

117533 -

无线电

+关注

关注

60文章

2143浏览量

116476 -

传输线

+关注

关注

0文章

376浏览量

24034 -

时钟树

+关注

关注

0文章

54浏览量

10752 -

毫米波

+关注

关注

21文章

1923浏览量

64812

原文标题:【世说知识】一文带你深度了解大型多GHz时钟树中的相位偏差

文章出处:【微信号:Excelpoint_CN,微信公众号:Excelpoint_CN】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

直观地了解相位偏差的根本原因和幅度

多GHz时钟树为什么会产生相位偏差?

【模拟对话】大型多GHz时钟树中的相位偏差

一文带你了解PLL器件的相位校准与控制

为什么要了解时钟树

想揭开相位偏差的“真面目”?这些经验之谈送给你

5.8G WiFi和2.4G WiFi如何选择?一文带你深度了解

一文带你深度了解大型多GHz时钟树中的相位偏差

一文带你深度了解大型多GHz时钟树中的相位偏差

评论