如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量,SoC时钟网络将由FPGA中的复杂时钟网络来解决,包括PLL、时钟分频、倍频以及本地时钟和全局时钟之间的同步。 一旦SoC设计规模很大,必须跨多个FPGA进行分区,则时钟方案的复杂性就上来了。

实际上,整个原型验证系统的时钟网络结构的顶层需要由FPGA原型验证系统板级解决,而不是在FPGA芯片内部解决,因为不同FPGA芯片内部的时钟源很难做到同步。我们可以将整个FPGA原型验证系统的硬件电路板视为“超级FPGA”,是一个更加宏观的系统,由FPGA加上将它们连接到整体平台中的顶级时钟资源连合组成。

要在原型验证系统的电路板级复制FPGA的时钟功能的完整层次结构,需要与每个FPGA内部的资源类似的资源。例如,我们需要板级PLL、时钟复用、时钟分频器和乘法器、时钟同步电路等等。

在许多情况下,我们可以通过使用工具或者技巧将SoC系统中的时钟简化为在FPGA原型验证系统电路板上处理的时钟来简化这一需求。例如,将SoC设计的一些门控时钟转换为等效的全局FPGA时钟,加上和此同源关系的时钟启用,以减少时钟域的总数。这种门控时钟转换可以在不改变RTL的情况下自动进行。

将灵活的时钟资源构建到一个FPGA原型验证系统的电路板中,以满足各种SoC设计的要求,需要大量的经验和专业知识。电路板仅使用时钟源和映射特定SoC设计所需的其他资源,这肯定比为所有基于FPGA的原型验证完全灵活使用要容易得多。然而,如果设计在项目期间发生某种程度的变化,时钟资源灵活性不足的母板将对分区决策造成更大的限制。

这也将大大降低整个FPGA原型验证系统电路板在多个项目中使用的能力,因为一个SoC项目的时钟资源可能与后续项目的时钟资源不匹配,我们需要的是一个通用的原型验证平台。

板间匹配时钟延迟

SoC中的时钟系统将在实际流片的芯片中实现,并对时钟分配延迟进行严格控制和分析。当这样的SoC系统被拆分到多个FPGA时,我们不能在系统FPGA时钟网络中引入偏差。将SoC设计划分为多个FPGA,那么就需要控制FPGA间延迟,特别是如果要使用多个FPGA平台板间级联,则需要控制板间延迟。

其中一些可以通过适当地限制FPGA工具来完成,并且可以通过降低原型的总体目标时钟速度来简化任务。然而,无论时钟速度如何,减轻这一任务的最佳方法是设计具有匹配和可预测时钟分布资源的板级电路。作为延迟匹配的一个例子,我们看SynopsysHAPS系列电路板。这些都是用延迟量来布置的,这些延迟量在时钟分布路径的关键点处重复。

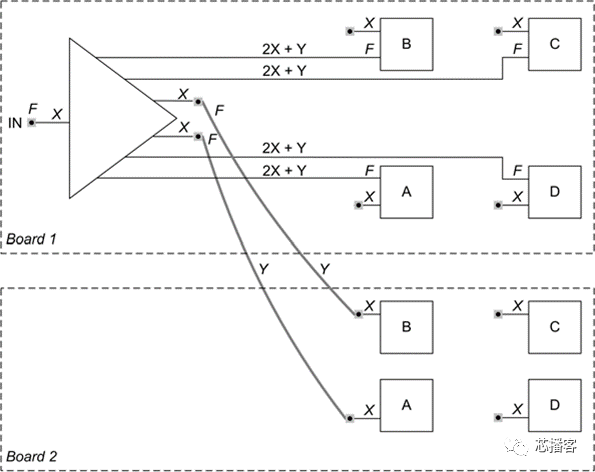

延迟X和Y,它们在电路板设计期间用作基本值。Y是典型时钟沿具有高质量屏蔽和同轴连接器的特定标准长度同轴电缆的延迟,该同轴电缆大量生产并广泛用于基于HAPS的平台。具有相对恒定延迟的单一类型和长度的电缆意味着板载可以设计为相同值Y。

对于PCB设计者来说,延迟电路板上的匹配是一件小事,尽管采用的Z字形迹线布线可能会增加对额外电路板布线层的需求。另一个延迟量X是FPGA引脚和附近连接器之间的线延迟,保持恒定相对简单。X和Y的值将是给定系列电路板的特征值,例如,对于一系列电路板,X=0.44ns,Y=1.45ns。

小心地,可以在新电路板设计中保持X和Y值,以便在同一原型中更容易地混合旧电路板和新电路板。我们现在可以从图中看到,时钟源和任何FPGA时钟引脚之间的时钟延迟将是相同的值,2X+Y。

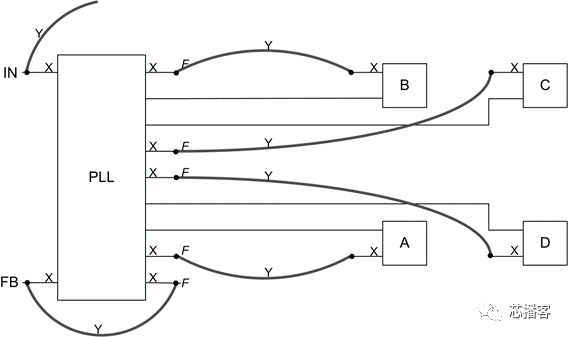

PLL对于消除交叉板时钟中的插入延迟非常有用

网络可以减少原型不同部分之间的时钟偏差。图中显示了驱动四个FPGA的板级PLL。通过使用长度匹配,可以使每个FPGA时钟输入端的短截线和PLL输出端的短截线等于值X。

在生产运行中,X的绝对值可能会变化,但对于任何给定的电路板都足够一致。另外,FPGA通过等长电缆或延迟Y连接到PLL输出。强烈建议使用同轴电缆和高保真时钟连接,以获得最佳可靠性和性能。

我们可以看到从PLL到每个FPGA的板上延迟是匹配的。为了在“超级FPGA”的顶层提供必要的时钟资源,电路板应包括PLL功能,这对于许多任务都很有用。尽管所使用的FPGA可能包括其自己的PLL功能,但电路板应包括分立的PLL设备,例如从众多供应商商购的那些。

系统时钟生成

一旦了解FPGA原型验证系统中的可用时钟资源,我们应该确定哪些额外的外部时钟源并正确利用它们,并为所有未来应用保持最大的灵活性。 时钟来源于哪里?FPGA板上的时钟源生成。主板外部时钟源。在FPGA中的时钟源生成。

需要什么时钟速率?估计可能的FPGA时钟频率范围。计划生成具有一定精度的任意时钟速率。 可以容忍什么样的时钟偏移?FPGA间同步:确保所有FPGA以可接受的偏差接收时钟源。板间同步:在大型系统中,确保所有时钟以可接受的偏差到达所有FPGA。

在解决上述问题时,通常可能包括以下大部分或全部要素:

板载时钟合成:通常是由晶振参考驱动的PLL,具有可配置的参数以选择所需的时钟频率。为了增加灵活性,晶振是可移除的。可能需要多个时钟发生器来支持具有多个时钟的系统。

输入时钟源选择器:考虑到可以从中获取时钟的多个源,例如本地(板上、FPGA)或外部,应实现时钟源多路复用器。多路复用器的管理可以通过手动开关进行,也可以通过单独的软件实用程序进行编程。

时钟分布:无论时钟源如何,时钟分布必须确保时钟以可接受的偏差在整个FPGA系统当中。过度偏斜可能会导致不正确的逻辑传播,并降低两个或多个FPGA或子系统之间的的裕度,从而将同步信号传递给彼此。在保持可接受的信号质量的同时,必须考虑和均衡板间和连接器延迟。

外部时钟源:必须考虑从一个FPGA板到另一个FPGA板的传播延迟,并且应通过适当的相移来均衡传播延迟。必须特别注意在时钟路径的源和目标之间级联多个PLL的情况,因为如果设计不当,可能会发生不稳定和锁不住稳定时钟的情况。

特殊的高速时钟:除了应用时钟之外,可能需要高速时钟在一个引脚上多路复用多个信号。这通常在两个FPGA之间的信号数量大于它们之间的可用引脚数量时使用。使用高速时钟,信号可以在源端的单个引脚上进行时间复用,然后在接收端进行解复用。为了使该方案正常工作,接口的两侧必须具有相同的高速时钟,且偏差最小。

时钟分频与倍频:时钟的灵活性要求顶级时钟可以缩放到设计各个部分的正确频率。虽然分频器和其他逻辑资源可以在FPGA设备内部用于此,但PLL也有其作用。

审核编辑:刘清

-

FPGA设计

+关注

关注

9文章

428浏览量

26458 -

分频器

+关注

关注

43文章

447浏览量

49735 -

SoC芯片

+关注

关注

1文章

605浏览量

34824 -

乘法器

+关注

关注

8文章

204浏览量

36927 -

时钟网络

+关注

关注

0文章

16浏览量

6559

原文标题:FPGA原型验证系统的时钟资源

文章出处:【微信号:于博士Jacky,微信公众号:于博士Jacky】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

验证中的FPGA原型验证 FPGA原型设计面临的挑战是什么?

ASIC设计-FPGA原型验证

高频RFID芯片的FPGA原型验证平台设计及验证

基于FPGA原型的GPS基带验证系统设计与实现

FACE-VUP:大规模FPGA原型验证平台

FPGA开发板vs原型验证系统

FPGA原型验证系统的时钟资源设计

FPGA原型验证系统的时钟资源设计

评论