评估对比xilinx以及altera两家FPGA芯片逻辑资源。

首先要说明,

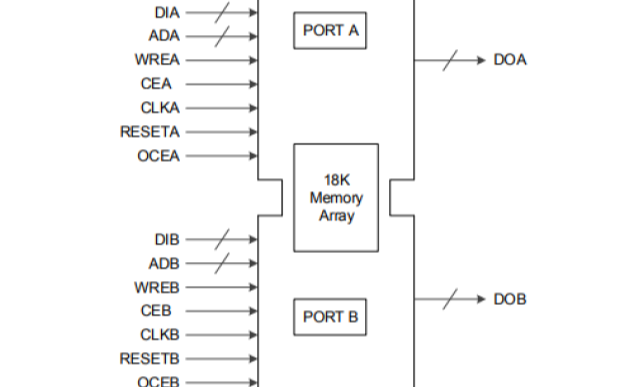

现今FPGA除了常规逻辑资源,还具有很多其他片内资源比如块RAM、DSP单元、高速串行收发器、PLL、ADC等等,用以应对不同的场合,逻辑量只能作为选型的重要依据之一。

不同厂家FPGA架构各异,具有很多独有的专利设计,量级相当的FPGA在应对不同应用场景下(比如视频处理、通讯总线、加密算法)时表现可能会差异很大,逻辑资源评估只是作为通常意义上的选型参考。

本文以占有率最大的X家和A家为例来进行比较。

首先对比下两家的芯片架构,

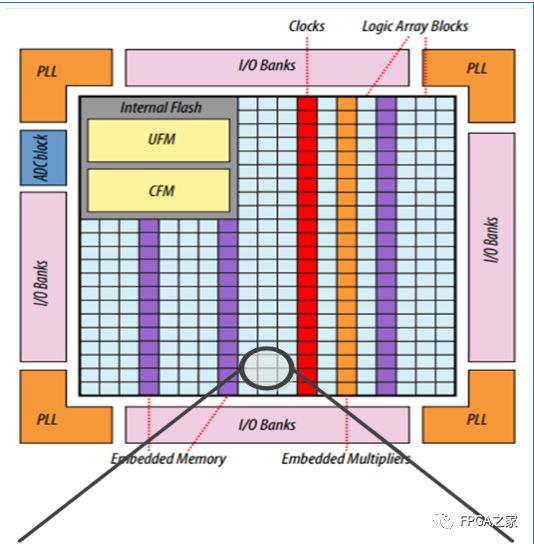

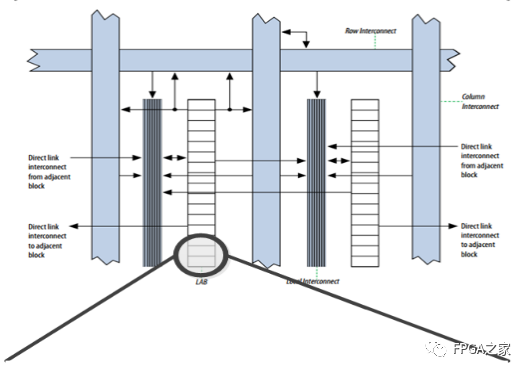

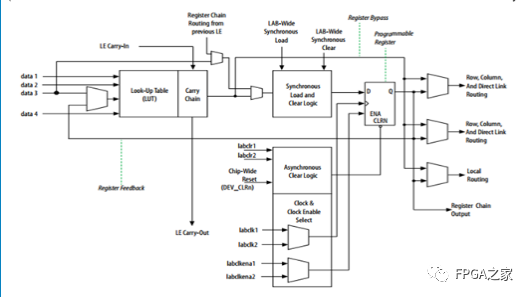

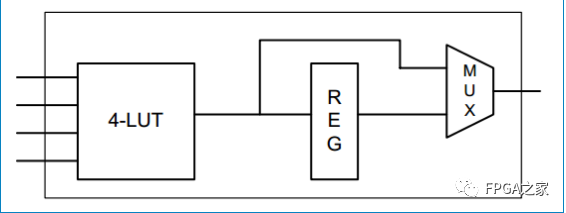

Altera LUT4架构(以入门级MAX10为例,以下材料来源于m10_handbook)

基本的逻辑单元由LAB组成,每个LAB包含16个LE,LE主要由一个LUT-4以及一个触发器。

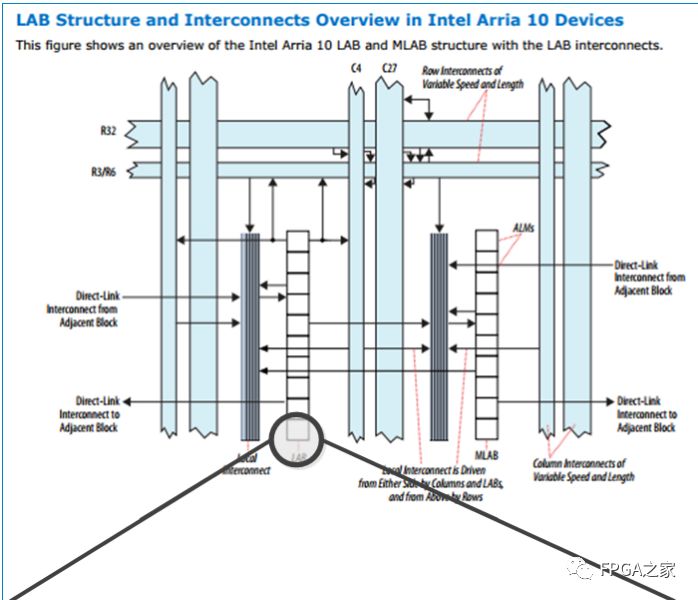

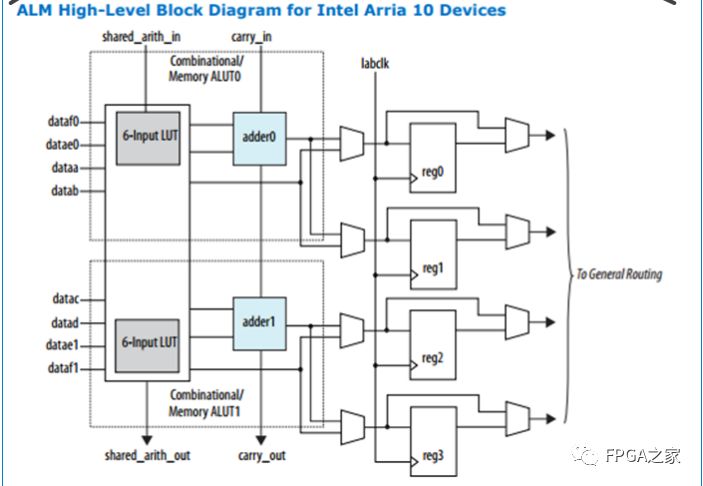

Altera ALM架构(以Arria10系列为参考)

基本逻辑单元LAB包含10xALM,ALM全程为Adaptive Logic Module,具有8输入和2输出,一个ALM可以配置成不同的LUT组合,比如2个单独LUT4、单独LUT5+LUT3、共享一个输入的LUT5+LUT4等等。ALM相比单独的LUT4架构显然具有更大的灵活性。

(a10_handbook.pdf)

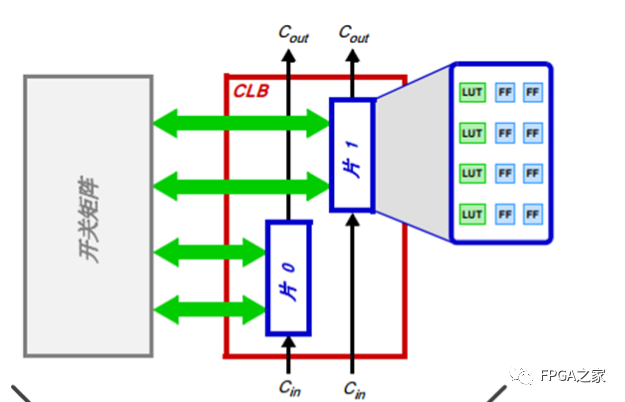

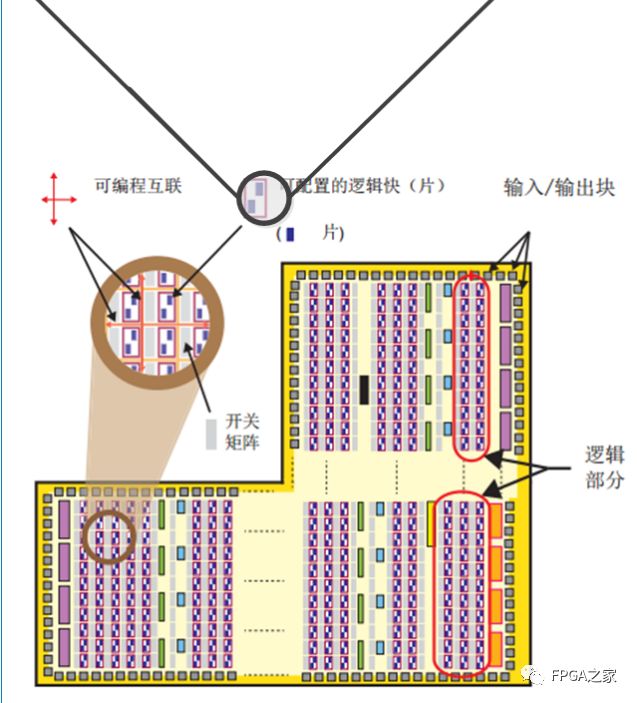

Xilinx(以7系列为例)

赛灵思基本逻辑单元叫做CLB,CLB内有具有两片Slice,每个Slice由4片LUT6及8个触发器组成。可见每个CLB约等于8 x LUT6。

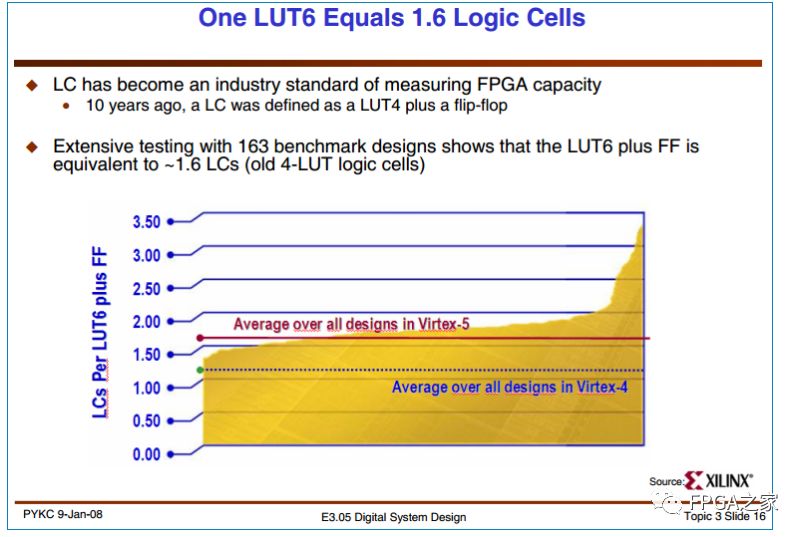

由于最早的FPGA多为基于LUT4组成,惯用的做法是用LUT4的数量近似表示逻辑量。现在FPGA不一定是基于LUT4,但可以转换成等效LUT4数量。XIlinx的叫做LC,ALTERA叫做LE,都可以理解成一个LUT4加触发器的单元的数量。

对MAX10来说,LE的数量就等于LUT4的数量,而xilinx 7系列基于LUT6,LUT与LC有如下换算关系:

审核编辑 :李倩

-

FPGA

+关注

关注

1664文章

22502浏览量

639151 -

架构

+关注

关注

1文章

537浏览量

26644 -

加密算法

+关注

关注

0文章

221浏览量

26295

原文标题:A/X家FPGA架构及资源评估

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Xilinx 7系列FPGA的时钟资源架构

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

FPGA 内部详细架构 精选资料分享

Xilinx FPGA底层资源架构与设计规范

FPGA的RAM存储资源详细资料说明

FPGA架构中的全局时钟资源介绍

Xilinx 7系列中FPGA架构丰富的时钟资源介绍

A/X家FPGA架构及资源评估

A/X家FPGA架构及资源评估

评论