继《XDC 约束技巧之 I/O 篇(上)》详细描述了如何设置 Input 接口 约束后,我们接着来聊聊怎样设置 Output 接口约束,并分析 UCF 与 XDC 在接口约束上的区别。

Output 接口类型和约束

FPGA 做 Output 的接口时序同样也可以分为系统同步与源同步。在设置 XDC 约束时,总体思路与 Input 类似,只是换成要考虑下游器件的时序模型。另外,在源同步接口中,定义接口约束之前,需要用 create_generated_clock 先定义送出的随路时钟。

系统同步接口

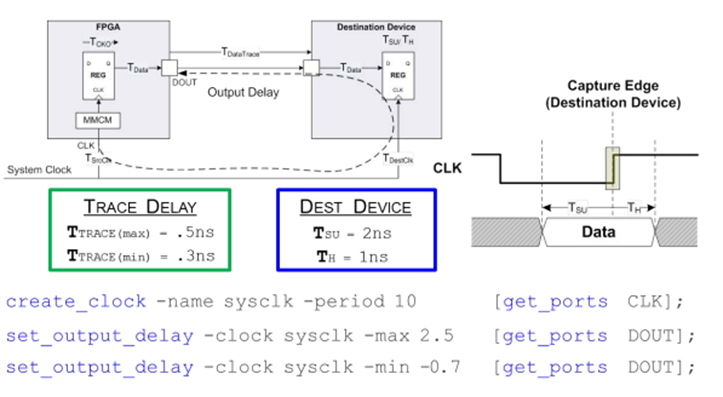

与 Input 的系统同步接口一样,FPGA 做 Output 接口的系统同步设 计,芯片间只传递数据信号,时钟信号的同步完全依靠板级设计来对齐。 所以设置约束时候要考虑的仅仅是下游器件的 Tsu/Th 和数据在板级的延时。

上图是一个 SDR 上升沿采样系统同步接口的 Output 约束示例。其 中,-max 后的数值是板级延时的最大值与下游器件的 Tsu 相加而得出, -min 后的数值则是板级延时的最小值减去下游器件的 Th 而来。

源同步接口

与源同步接口的 Input 约束设置类似,FPGA 做源同步接口的 Output 也有两种方法可以设置约束。

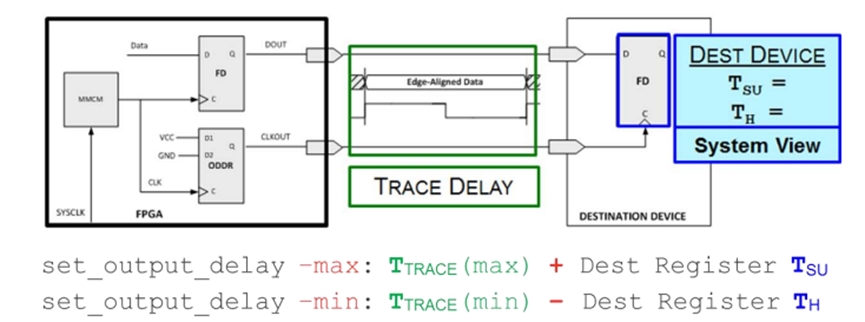

方法一我们称作 Setup/Hold Based Method,与上述系统同步接口的设置思路基本一致,仅需要了解下游器件用来锁存数据的触发器的 Tsu 与 Th 值与系统板级的延时便可以设置。方法二称作 Skew Based Method, 此时需要了解 FPGA 送出的数据相对于时钟沿的关系,根据 Skew 的大小和时钟频率来计算如何设置 Output 约束。

具体约束时可以根据不同的已知条件,选用不同的约束方式。一般而言,FPGA 作为输出接口时,数据相对时钟的 Skew 关系是已知条件(或者说,把同步数据相对于时钟沿的 Skew 限定在一定范围内是设计源同步接口的目标),所以方法二更常见。

Vivado IDE 的 LanguageTemplates 中关于源同步输出接口的 XDC 约束模板包含了以上两种方式的设置方法。

方法一 Setup/Hold Based Method

Setup/Hold Based Method 的计算公式如下,可以看出其跟系统同步输出接口的设置方法完全一样。如果换成 DDR 方式,则可参考上一篇 I/O 约束方法中关于 Input 源同步 DDR 接口的约束,用两个可选项 -clock_fall 与 -add_delay 来添加针对时钟下降沿的约束值。

如果板级延时的最小值(在源同步接口中,因为时钟与信号同步传递,所以板级延时常常可以视作为 0)小于接收端寄存器的 Th,这样计算出的结果就会在 -min 后出现负数值,很多时候会让人误以为设置错误。其实这里的负数并不表示负的延迟,而代表最小的延迟情况下,数据是在时钟采样沿之后才有效。同样的,-max 后的正数,表示最大的延迟情况下,数据是在时钟采样沿之前就有效了。

这便是接口约束中最容易混淆的地方,请一定牢记 set_output_delay 中 -max/-min 的定义,即时钟采样沿到达之前最大与最小的数据有效窗口。

如果我们在纸上画一下接收端的波形图,就会很容易理解:用于 setup 分析的 -max 之后跟着正数,表示 数据在时钟采样沿之前就到达,而用于 hold 分析的 -min 之后跟着负数,表示数据在时钟采样沿之后还保持了一段时间。只有这样才能满足接收端用于锁存接口数据的触发器的 Tsu 和 Th 要求。

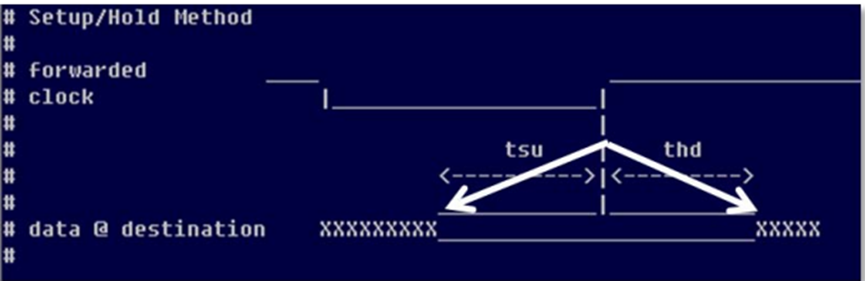

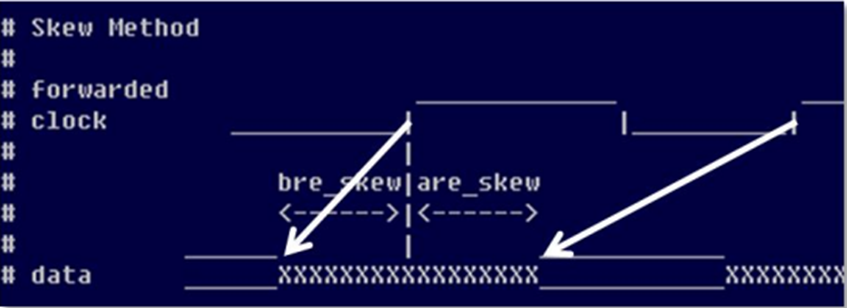

方法二 Skew Based Method

为了把同步数据相对于时钟沿的 Skew 限定在一定范围内,我们可以基于 Skew 的大小来设置源同步输出接口的约束。此时可以不考虑下游采样器件的 Tsu 与 Th 值。

我们可以通过波形图来再次验证 set_output_delay 中 -max/-min 的定义,即时钟采样沿到达之前最大与最小的数据有效窗口。

DDR 接口的约束设置

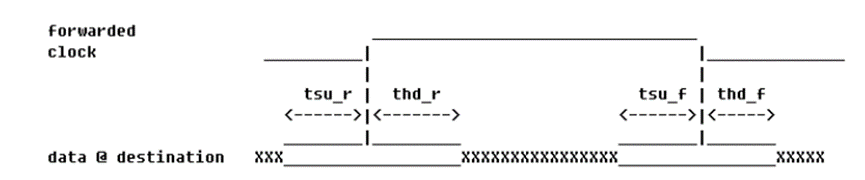

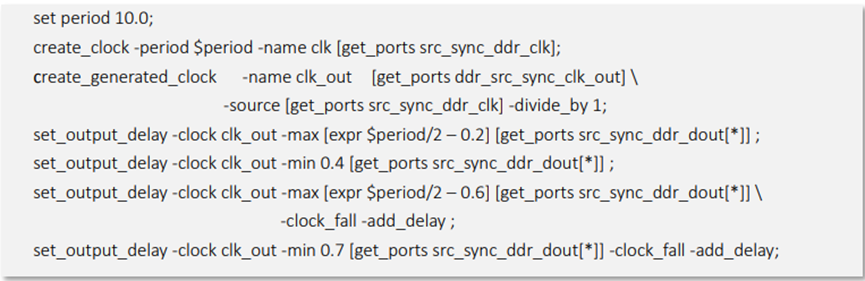

DDR 接口的约束稍许复杂,需要将上升沿和下降沿分别考虑和约束,以下以源同步接口为例,分别就 Setup/Hold Based 方法和 Skew Based 方法举例。

方法一 Setup/Hold Based Metho

已知条件如下:

时钟信号 src_sync_ddr_clk 的频率: 100 MHz

随路送出的时钟 src_sync_ddr_clk_out 的频率: 100 MHz

数据总线: src_sync_ddr_dout[3:0]

接收端的上升沿建立时间要求 ( tsu_r ) : 0.7 ns

接收端的上升沿保持时间要求 (thd_r ) : 0.3 ns

接收端的下降沿建立时间要求 (tsu_f) : 0.6 ns

接收端的下降沿保持时间要求 (thd_f ) : 0.4 ns

板级走线延时:0 ns

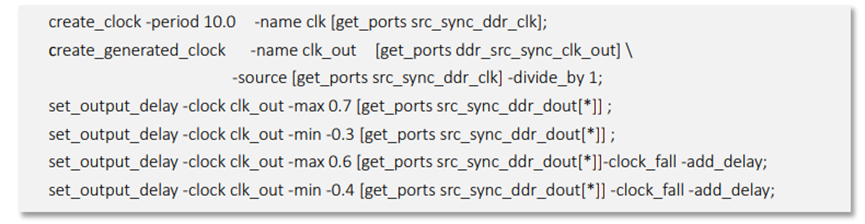

可以这样计算输出接口约束:已知条件包含接收端上升沿和下降沿的建立与保持时间要求,所以可以分别独立计算。上升沿采样数据的 -max 是板级延时的最大值加上接收端的上升沿建立时间要求(tsu_r),对应的 -min 就应该是板级延时的最小值减去接收端的上升沿保持时间要求(thd_r);下降沿采样数据的 -max 是板级延时的最大值加上接收端的下降沿建立时间要求(tsu_f),对应的-min 就应该是板级延时的最小值减去接收端的下降沿保持时间要求(thd_f)。所以最终写入 XDC 的 Output 约束应该如下所示:

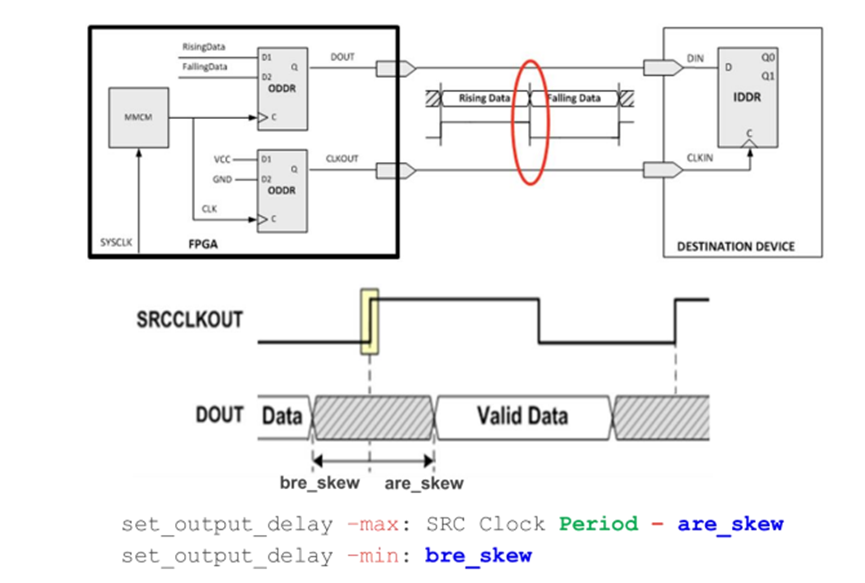

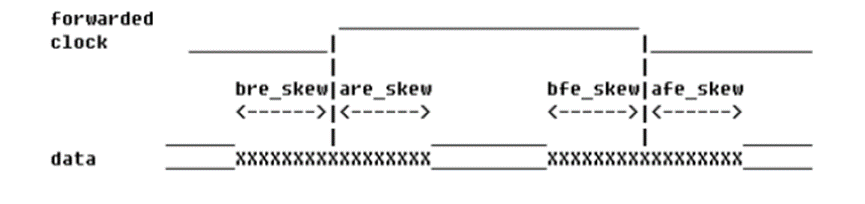

方法二 Skew Based Method

已知条件如下:

时钟信号 src_sync_ddr_clk 的频率: 100 MHz

随路送出的时钟 src_sync_ddr_clk_out 的频率: 100 MHz

数据总线: src_sync_ddr_dout[3:0]

上升沿之前的数据 skew ( bre_skew ) : 0.4 ns

上升沿之后的数据 skew ( are_skew ) : 0.6 ns

下降沿之前的数据 skew ( bfe_skew ) : 0.7 ns

下降沿之后的数据 skew ( afe_skew ) : 0.2 ns

可以这样计算输出接口约束:时钟的周期是 10ns,因为是 DDR 方式,所以数据实际的采样周期是时钟周期的一半;上升沿采样的数据的 -max 应该是采样周期减去这个数据的发送沿(下降沿)之后的数据 skew 即 afe_skew,而对应的-min 就应该是上升沿之前的数据 skew 值bre_skew ;同理,下降沿采样数据的 -max 应该是采样周期减去这个数据的发送沿(上升沿)之后的数据 skew 值 are_skew,而对应的-min 就应该是下 降沿之前的数据 skew 值 bfe_skew 。

所以最终写入 XDC 的 Output 约束应该如下所示:

对以上两种方法稍作总结,就会发现在设置 DDR 源同步输出接口时,送出的数据是中心对齐的情况下,用 Setup/Hold Based 方法来写约束比较容易,而如果是边沿对齐的情况,则推荐使用 SkewBased 方法来写约束。

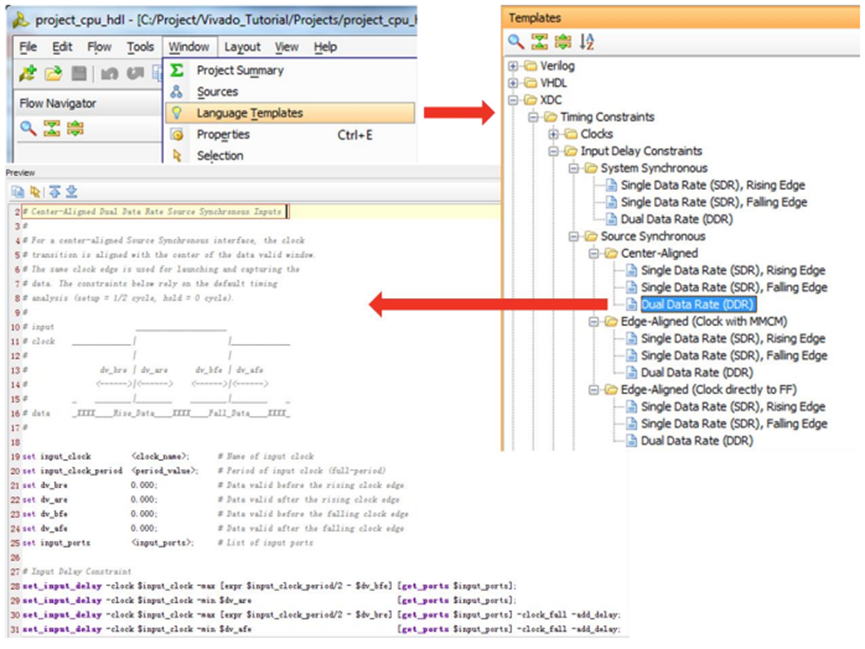

在 Vivado 中设置接口约束

FPGA 的接口约束种类多变,远非一篇短文可以完全覆盖。在具体设计中,建议用户参照 Vivado IDE 的 Language Templates 。其中关于接口约束的例子有很多,而且也是按照本文所述的各种分类方法分别列出。

具体使用时,可以在列表中找到对应的接口类型,按照模板所示调整成自己设计中的数据,然后可以方便地计算出实际的约束值,并应用到 FPGA 工程中去。

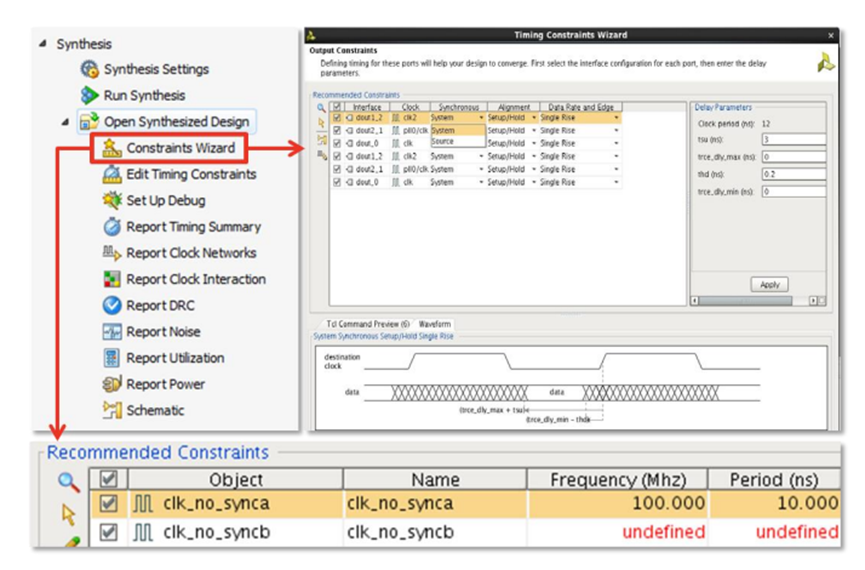

自 2014.1 版开始,Vivado 还提供一个 Constraints Wizard 可供用户使用。只需打开综合后的设计,然后启动 Wizard,工具便可以根据读到的网表和设计中已有的 XDC 时序约束(也可以任何约束都不加而开始用 Wizard)一步步指引用户如何添加 Timing 约束,包括时钟、I/O 以及时序例外约束等等。

Constraints Wizard 的调出方法和界面如下图所示。

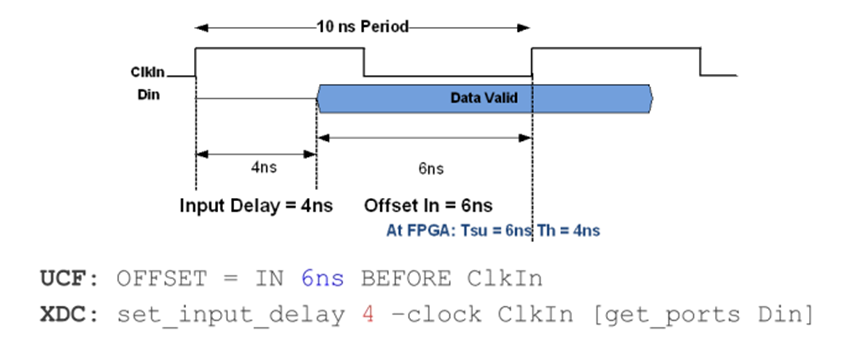

UCF 与 XDC 的区别

《XDC 约束技巧》开篇描述 XDC 基础语法时候曾经提到过设置接口约束时 UCF 与 XDC 的区别,简单来讲,UCF 是原生的 FPGA 约束,所以分析问题的视角是 FPGA 本身,而 XDC 则是从系统设计的全局角度来分析和设置接口约束。

以最基础的 SDR 系统同步接口来举例。输入侧的设置,UCF 用的是 OFFSET = IN,而 XDC 则是 set_input_delay 。

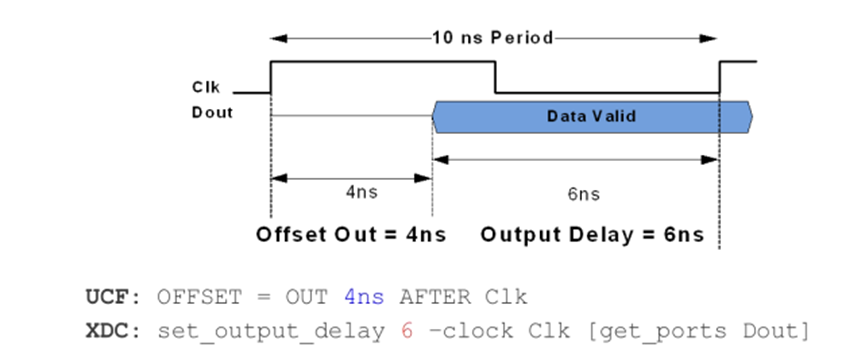

输出侧的设置,UCF 用的是 OFFSET =OUT,而 XDC 则是 set_output_delay 。

如果需要从旧设计的 UCF 约束转到 XDC 约束,可以参考上述例子。以一个采样周期来看,UCF 中与 XDC 中设置的接口约束值加起来正好等于一个周期的值。

小结

这一系列《XDC 约束技巧》的文章至此暂时告一段落。其实读懂了这几篇涵盖了时钟、CDC 以及接口约束的短文,基本上已经足够应对绝大多数的 FPGA 设计约束问题。当然在这么短小的篇幅内,很多问题都无法更加深入地展开,所以也提醒读者,需要关注文中推荐的各类 Xilinx 官方文档,以及 Vivado 本身自带的帮助功能与模板。

希望各位能从本文中吸取经验,少走弯路,尽快地成为 Vivado 和 XDC 的资深用户,也希望本文能真正为您的设计添砖加瓦,达到事半功倍的效果。

-

接口

+关注

关注

33文章

8822浏览量

152638 -

信号

+关注

关注

11文章

2823浏览量

77528 -

时序

+关注

关注

5文章

392浏览量

37585 -

约束

+关注

关注

0文章

82浏览量

12839 -

xdc

+关注

关注

1文章

24浏览量

5985

原文标题:XDC约束技巧之I/O篇(下)

文章出处:【微信号:FPGA算法工程师,微信公众号:FPGA算法工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

XDC约束技巧之I/O篇(下)

XDC约束技巧之I/O篇(下)

评论