01为什么是 RISC-V?

由行业偶像Jim Keller掌舵的初创公司Tenstorrent组建了一支一流的AI和CPU工程师团队,制定了涉及通用处理器和人工智能加速器的宏伟计划。

目前,该公司正在研发业界首款能够同时处理客户端和HPC工作负载的8宽解码RISC-V内核,该内核将首先用于面向数据中心的128核高性能CPU。该公司还有多代处理器的路线图,我们将在下面介绍。

我们最近与Tenstorrent的首席CPU架构师Wei-Han Lien就公司的愿景和路线图进行了交谈。Lien 拥有令人印象深刻的背景,曾在 NexGen、AMD、PA-Semi、Apple 工作过,最著名的可能是他在Apple的A6、A7(世界上第一款64位Arm SoC)和M1 CPU微架构和实施方面的工作。

公司有许多在 x86 和 Arm 设计方面拥有丰富经验的世界级工程师,有人可能会问为什么 Tenstorrent 决定开发 RISC-V CPU,因为这种指令集架构 (ISA) 的数据中心软件堆栈不如 x86和Arm 的全面。Tenstorrent 给我们的答案很简单:x86 由 AMD 和 Intel 控制,而 Arm 由 Arm Holding 控制,这限制了创新的步伐。

“世界上主要只有两家公司可以生产 x86 CPU,”Wei-Han Lien 说。“由于 x86 许可限制,创新基本上由一两家公司控制。当公司变得非常大时,它们就会变得官僚化,创新的步伐 [ 放缓 ]。[...] Arm 有点类似。他们声称他们就像一家 RISC-V 公司,但如果你看一下他们的规范,[它] 变得如此复杂。它实际上也有点由一位架构师主导。[…] Arm 有点规定所有可能的场景,甚至是架构[许可]合作伙伴。”

相比之下,RISC-V发展迅速。据Tenstorrent称,由于它是一个开源ISA,因此使用它进行创新更容易、更快速,尤其是在涉及新兴和快速开发的 AI 解决方案时。

“我一直在为 [Tenstorrent 的] AI 解决方案寻找配套的处理器解决方案,然后我们想要 BF16 数据类型,然后我们去找Arm说,'嘿,你能支持我们吗?'他们说‘不’,这可能需要两年的内部讨论以及与合作伙伴的讨论等等,”Lien 解释道。“但我们和 SiFive 谈过;他们只是把它放在那里。所以,没有限制,他们为我们建造了它,这是自由的。”

一方面,Arm Holding 的方法确保了高质量的标准和全面的软件堆栈,但这也意味着 ISA 创新的步伐变慢,这对于AI处理器等新兴应用来说可能是一个问题,这些应用旨在得到快速发展。

02一个微架构,一年五个 CPU IP

由于Tenstorrent着眼于并解决整个AI应用,它不仅需要不同的片上系统或系统级封装,还需要各种CPU微架构实现和系统级架构来实现不同的功率和性能目标。这正是Wei-Han Lien 的部门所致力于解决的问题。 不起眼的消费电子SoC和强大的服务器处理器几乎没有共同之处,但可以共享相同的ISA和微体系结构(管实现方式不同)。这就是Lien的团队发挥作用的地方。Tenstorrent 表示,公司CPU团队开发了一种无序 RISC-V 微架构,并以五种不同的方式实现它,以解决各种应用程序的问题。

Tenstorrent现在有五种不同的RISC-V CPU核心IP——具有两宽、三宽、四宽、六宽和八宽解码——用于其自己的处理器或许可给感兴趣的各方。对于那些需要非常基本的CPU的潜在客户,该公司可以提供具有两个宽度执行的小内核,但对于那些需要更高性能的边缘、客户端PC和高性能计算的客户,它有六个宽度的Alastor和八个宽Ascalo 内核。

每个带八位解码的乱序Ascalon ( RV64ACDHFMV) 内核都有六个ALU、两个FPU和两个256位向量单元,使其非常强大。考虑到现代x86设计使用四宽 (Zen 4) 或六宽 (Golden Cove) 解码器,我们正在寻找一个非常强大的内核。

Wei-Han Lien 是负责苹果“宽”CPU 微架构的设计师之一,该架构每个时钟最多可执行8条指令。例如,Apple的A14和M1 SoC具有八个宽的高性能 Firestorm CPU内核,在推出两年后,它们仍然是业内最节能的设计之一。Lien 可能是业界“宽”CPU微架构方面最好的专家之一,据我们所知,他是唯一一位领导工程师团队开发八宽RISC-V高性能CPU内核的处理器设计师。

除了各种RISC-V通用内核外,Tenstorrent还拥有为神经网络推理和训练量身定制的专有 Tensix 内核。每个 Tensix 内核包含五个RISC内核、一个用于张量运算的数组数学单元、一个用于矢量运算的SIMD单元、1MB或 2MB的 SRAM,以及用于加速网络数据包运算和压缩/解压缩的固定功能硬件。Tensix内核支持多种数据格式,包括BF4、BF8、INT8、FP16、BF16,甚至 FP64。

03令人印象深刻的路线图

目前,Tenstorrent 有两种产品:一种称为Grayskull的机器学习处理器,可提供约315 INT8 TOPS的性能,可插入PCIe Gen4插槽,以及网络Wormhole ML处理器,具有约 350 INT8 TOPS 的性能并使用GDDR6 内存子系统,一个PCIe Gen4 x16接口,并具有与其他机器的400GbE连接。

这两种设备都需要一个主机CPU,可以作为附加板使用,也可以在预构建的 Tenstorrent 服务器中使用。一台包含32个 Wormhole ML卡的4U Nebula服务器在6kW时提供大约12 INT8 POPS的性能。

今年晚些时候,该公司计划推出其第一个独立的CPU+ML解决方案——Black Hole——结合了24个SiFive X280 RISC-V内核和多个第三代Tensix内核,这些内核使用两个在机器的相反方向运行的2D环面网络互连学习工作量。该设备将提供1 INT8 POPS的计算吞吐量(与其前身相比性能提升约三倍)、八个GDDR6内存通道、1200 Gb/s以太网连接和PCIe Gen5通道。

此外,该公司期待为双芯片解决方案以及未来使用添加2TB/s 的die to die接口。该芯片将采用6nm级制造工艺(我们预计它是台积电N6,但 Tenstorrent 尚未证实这一点),但在600mm²时,它将比台积电12nm级节点生产的前代产品更小. 需要记住的一件事是,Tenstorrent 尚未开发出其 Blackhole,其最终功能集可能与公司今天披露的不同。

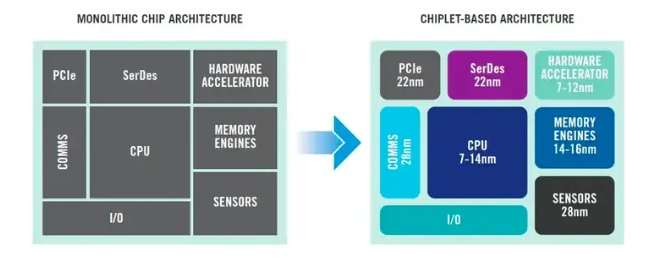

明年,该公司将发布其终极产品:名为Grendel的多小芯片解决方案,该解决方案具有自己的Ascalon通用内核,具有自己的RISC-V微架构,具有八位解码器以及用于ML工作负载的基于 Tensix 的小芯片。

Grendel 是 Tenstorrent 将于明年发布的终极产品集:多chiplet 解决方案包括一个具有高性能 Ascalon 通用内核的 Aegis chiplet 和一个或多个具有用于 ML 工作负载的 Tensix 内核的 chiplet。根据业务需求(以及公司的财务能力),Tenstorrent 可以使用 3nm 级工艺技术实现AI chiplet,从而利用更高的晶体管密度和Tensix核心数,或者它可以继续使用 Black Hole chiplet进行AI工作负载(甚至将一些工作分配给24个 SiFive X280内核,该公司表示)。小芯片将使用上述 2TB/s 互连相互通信。

Aegis小芯片具有128个通用 RISC-V八宽Ascalon内核,组织在四个32核集群中,具有集群间一致性,将使用3nm级工艺技术制造。事实上,Aegis CPU小芯片将率先使用3纳米级制造工艺,这可能会使该公司在高性能CPU设计方面名列前茅。 同时,Grendel 将使用LPDDR5内存子系统、PCIe和以太网连接,因此它将提供比公司现有解决方案明显更高的推理和训练性能。说到Tensix内核,需要注意的是,虽然Tenstorrent的所有AI内核都被称为Tensix,但这些内核实际上是在进化的。

“[Tensix]的变化是渐进的,但它们确实存在,”该公司创始人Ljubisa Bajic 解释道。“[他们添加了]新的数据格式、FLOPS/SRAM 容量的变化比率、SRAM 带宽、片上网络带宽、新的稀疏特性以及一般特性。”

有趣的是,不同的Tenstorrent幻灯片提到了Black Hole和Grendel产品的不同内存子系统。这是因为该公司一直在寻找最高效的内存技术,并且因为它获得了DRAM控制器和物理接口 (PHY) 的许可。因此,它在选择确切的内存类型时具有一定的灵活性。事实上,Lien 表示,Tenstorrent也在为未来的产品开发自己的内存控制器,但对于2023~2024年的解决方案,它打算使用第三方的MC和PHY。同时,出于本考虑,目前Tenstorrent不打算使用任何奇特的内存,例如HBM。

04商业模式:销售解决方案和许可IP

虽然 Tenstorrent 有五个不同的CPU IP(尽管基于相同的微架构),但它只有 AI/ML 产品在流水线中(如果不考虑完全配置的服务器)使用SiFive的 X280 或 Tenstorrent 的八宽 Ascalon CPU 内核. 因此,有理由问为什么它需要这么多的CPU内核实现。

对这个问题的简短回答是,Tenstorrent 有一个独特的商业模式,包括 IP 许可(以 RTL、硬宏,甚至 GDS 形式)、销售小芯片、销售附加 ML 加速卡或具有 CPU 和 ML 小芯片的 ML 解决方案,并销售包含这些卡的完全配置的服务器。 构建自己的 SoC 的公司可以授权 Tenstorrent 开发的 RISC-V 核心,广泛的 CPU IP 组合使公司能够竞争需要不同级别性能和功率的解决方案。

服务器供应商可以使用 Tenstorrent 的 Grayskull 和 Wormhole 加速器卡或 Blackhole 和 Grendel ML 处理器来构建他们的机器。同时,那些不想构建硬件的实体可以购买预构建的 Tenstorrent 服务器并进行部署。

这种商业模式看起来有些争议,因为在许多情况下,Tenstorrent 与自己的客户竞争并将竞争。然而,归根结底,如Nvidia 等厂商提供了基于这些主板的附加卡和预制服务器,而且戴尔或 HPE 等公司似乎并不太担心这一点,因为它们为特定客户提供解决方案,而不仅仅是积木。

05总结

大约两年前,随着 Jim Keller 的聘用,Tenstorrent 一跃成为人们关注的焦点。在两年内,该公司招募了一批顶尖工程师,他们正在为数据中心级 AI/ML 解决方案和系统开发高性能 RISC-V 内核。开发团队的成就包括全球首个八位 RISC-V 通用 CPU 内核,以及可用于 AI 和 HPC 应用的适当系统硬件架构。

该公司有一个全面的路线图,包括基于 RISC-V 的高性能 CPU 小芯片和先进的 AI 加速器小芯片,它们有望为机器学习提供功能强大的解决方案。请记住,AI 和 HPC 是有望实现爆炸式增长的主要大趋势,提供 AI 加速器和高性能 CPU 内核似乎是一种非常灵活的商业模式。

AI 和 HPC 市场竞争激烈,因此当您想与老牌竞争对手(AMD、英特尔、Nvidia)和新兴玩家(Cerebras、Graphcore)竞争时,必须聘请一些世界上最优秀的工程师。与大型芯片开发商一样,Tenstorrent 拥有自己的通用 CPU 和 AI/ML 加速器硬件,这是得天独厚的优势。同时,由于该公司使用 RISC-V ISA,因此目前无法解决一些市场和工作负载,至少就 CPU 而言是这样。

审核编辑:刘清

-

处理器

+关注

关注

68文章

19349浏览量

230310 -

ARM

+关注

关注

134文章

9111浏览量

368047 -

加速器

+关注

关注

2文章

802浏览量

37941 -

RISC-V

+关注

关注

45文章

2300浏览量

46261

原文标题:Jim Keller究竟在做什么芯片?

文章出处:【微信号:算力基建,微信公众号:算力基建】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Tenstorrent获7亿美元融资,贝索斯参投挑战英伟达

RISC-V,即将进入应用的爆发期

如何做一个hpm6750evk2的bootloader?

HPM6750 Bootloader设计

超高频读写器究竟是什么,能做什么?一文读懂!

香港应科院与苏州国芯联合组建新型AI芯片实验室,推动AI芯片行业发展

Jim Keller:NVIDIA私有协议弊端多,倡导开放技术以省数十亿

请问ucos libMicrium.a文件是做什么的?

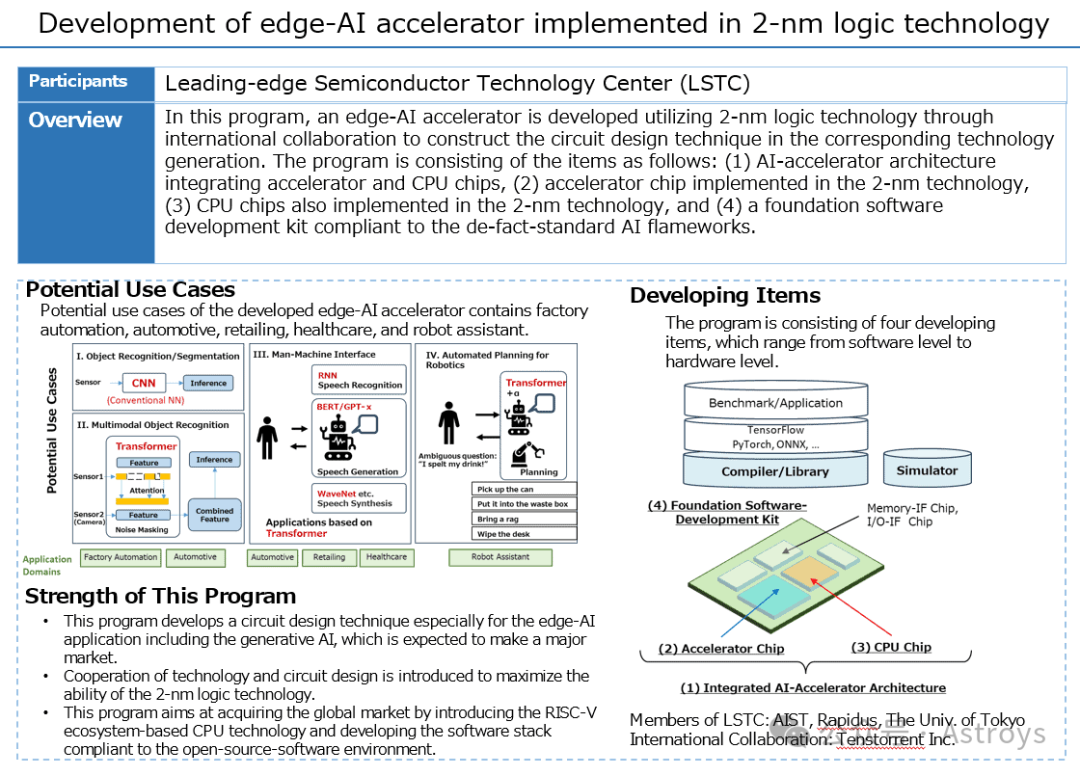

日本为何押注于Jim Keller?

前特斯拉、前苹果工程师开始与日本“领先半导体技术中心”合作

填充胶是做什么用的?

Jim Keller究竟在做什么芯片

Jim Keller究竟在做什么芯片

评论