ADSP-2156x 处理器的速度高达 1 GHz,属于 SHARC 系列产品。ADSP-2156x 处理器基于 SHARC+ 单内核。ADSP-2156x SHARC 处理器是 SIMD SHARC 系列数字信号处理器 (DSP) 中的一款产品,采用 ADI 公司的超级哈佛架构。这些 32 位/40 位/64 位浮点处理器已针对高性能音频/浮点应用进行优化,具有大型片内静态随机存取存储器 (SRAM)、打破输入/输出 (I/O) 瓶颈的多个内部总线和创新型数字音频接口 (DAI)。SHARC+ 内核的新增特性包括高速缓存增强和分支预测,同时保持了指令集与以往 SHARC 产品的兼容性。

SHARC+ 处理器集成了一组丰富的行业较领先系统外设和存储器(请参见数据手册上的表 1),因此对于需要在集成封装中提供类似于精简指令集计算 (RISC) 的可编程性、多媒体支持和较领先信号处理能力的应用,该处理器是优选平台。这些应用涵盖广泛的市场,包括汽车、专业音频和需要高浮点性能的工业型应用。

应用

汽车:

音频放大器、主机、ANC/RNC、后座娱乐系统、数字座舱、ADAS

消费电子和专业音频:

扬声器、条形音箱、AVR、会议系统、调音台、麦克风阵列、耳机

-

处理器

+关注

关注

68文章

19259浏览量

229653 -

dsp

+关注

关注

553文章

7987浏览量

348756

原文标题:ADSP-21565 高达 1GHz SHARC+ DSP 带 640KB L1

文章出处:【微信号:兆亿微波,微信公众号:兆亿微波】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

LMX2571EVM如何实现1GHz的时钟输出?

THS3202能输出1GHz,2Vpp信号吗?

采用低于1GHz Simplelink™无线MCU的无线运动检测器

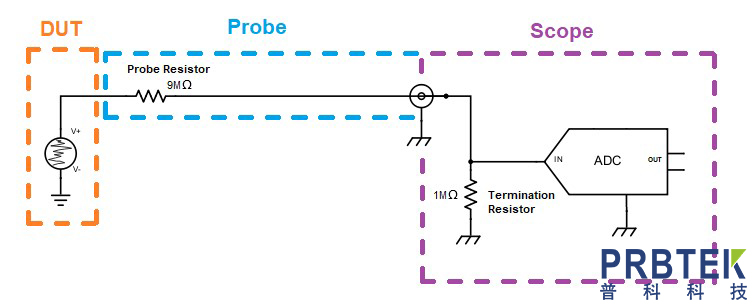

为什么TPP1000(泰克无源探头1GHz)与我的示波器不兼容?

OPA847能实现1GHZ以上信号的电压跟随吗?

FPGA输出一个1GHz的数字信号,需要buffer,要怎么实现?

LMH6629设计高通滤波器,为什么高频1Ghz会出现峰值peak?

BK1661 全集成的单芯片 L1 频段 GNSS 解决方案

BK1662 单芯片L1/L5双频GNSS解决方案

BK1616P 全集成的单芯片 L1 频段 GNSS 解决方案(高性价比FLASH版本)

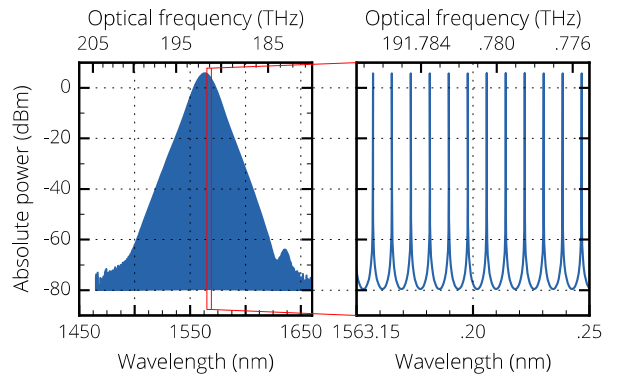

如何搭建简易1GHz低噪声光频梳系统

请问sigmastudio算法集成对什么资源有要求,以及有什么方法可以查看系统资源占用情况?

搭建简易1GHz低噪声光频梳系统

ADSP-21565 高达 1GHz SHARC+ DSP 带 640KB L1

ADSP-21565 高达 1GHz SHARC+ DSP 带 640KB L1

评论