在尝试将锁相环(PLL)锁定时,你是否碰到过麻烦?草率的判断会延长调试过程,调试过程变得更加单调乏味。根据以下验证通行与建立锁定的程序,调试过程可以变得非常简单。

第1步:验证通信

第一步是验证PLL响应编程的能力。如果PLL没有锁定,无法读回,则尝试发送需要最小量硬件命令工作的软件命令。一种方法是通过软件(而非引脚)调节PLL的通电断电寻找引脚的可预测电流变化或偏置电压电平变化。许多PLL在其输入(OSCin)引脚的电平在通电时为Vcc/2,在断电时为0V。

如果PLL集成了压控振荡器(VCO),则查看低压差(LDO)输出引脚电压是否对通电和断电命令做出反应。还可能可以切换输入/输出 (I/O)引脚,比如许多LMX系列PLL的MUXout引脚。如果采用上述方法能够验证通信,就可以继续尝试进行锁定。

如果无法验证通信,则查找常见的原因,例如以下原因:

编程串行

锁存使能(也称为芯片选择条(CSB))过高

对软件输入的低通滤波过多

与串行外围设备接口总线(SPI)存在时序问题

电源引脚焊接有误

第2步:建立锁定

验证通信后,下一步就是尝试对PLL进行锁定。下面是PLL无法锁定的一些更常见的原因:

对锁定检测引脚的错误解读。如果配置有误,锁定检测引脚会在实际已经锁定的情况下显示出PLL未锁定。可以通过查看频谱分析仪输出或VCO调谐电压验证这一情况。

编程问题。向PLL发送错误的信息会很容易导致无法锁定。一些常见的编程错误包括:VCO编程频率超出范围、VCO校准设置不正确或寄存器时序有误。

VCO校准问题。对于集成VCO的PLL而言,频率范围通常分成几个不同的频段。错误的编程会导致VCO锁定错误的频段。对特定寄存器的编程通常会启动VCO校准;因此必须确定在编程此寄存器时,其他软件和硬件(尤其是基准输入)状态正确,以确保校准正常工作。

输入或反馈路径问题。如果VCO输入或基准输入因电源水平较低、压摆率较低、匹配较差或谐波较高而存在问题,会导致PLL打开锁定。大多数PLL有方法输出内部频率计数器的实际频率输出,将其发送到引脚。

环路滤波器中与地连接或短路。可以通过查看调谐电压或切换鉴相器两极,根据频率变化确定连接或短路。

PLL环路滤波器不稳定。如果降低电荷泵电流导致PLL锁定通常是不稳定的表现,但是仅凭这项技术不起作用不能排除不稳定这一因素。导致环路滤波器不稳定的产检原因有忽略考虑VCO输入电容;使用过度限制环路带宽的集成滤波器;或者使用与PLL初始设计不同的PLL设置(电荷泵增益、VCO频率或鉴相器频率)。许多TI的工具如PLLatinum™模拟器工具能够模拟环路滤波器的不稳定性。

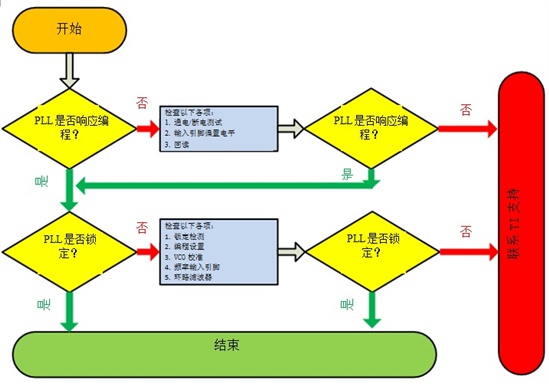

遵循系统的方法,不作出草率的假设能够使PLL锁定调试程序变得简单许多。图1为指导此程序的流程图。

图1:PLL调试流程图

审核编辑:郭婷

-

寄存器

+关注

关注

31文章

5317浏览量

120000 -

pll

+关注

关注

6文章

774浏览量

135044 -

VCO

+关注

关注

12文章

190浏览量

69148

发布评论请先 登录

相关推荐

AD9694输入时钟低于337.5MHz时,serdes锁相环无法锁定怎么解决?

AD9694的204B接口锁相环无法锁定是怎么回事?

ADF4360-7对VCO电感位置进行移动后锁相环无法锁定

电荷泵锁相环电路锁定检测的基本原理,影响锁相环数字锁定电路的关键因子是什么?

AD9779内部锁相环无法锁定怎么解决?

详解FPGA数字锁相环平台

利用开关的控制加速锁相环锁定的设计方法

教大家如何解决锁相环无法锁定

如何解决锁相环无法锁定

如何解决锁相环无法锁定

评论