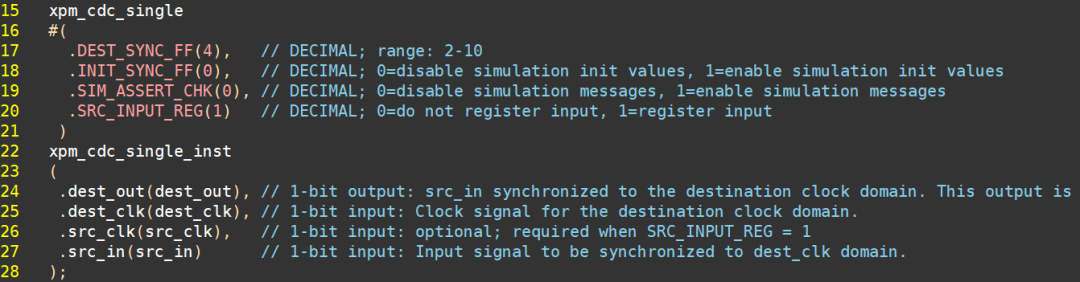

单位宽(Single bit)信号即该信号的位宽为1,通常控制信号居多。对于此类信号,如需跨时钟域可直接使用xpm_cdc_single,如下图代码所示。参数DEST_SYNC_FF决定了级联触发器的个数,取值范围为2~10;参数INIT_SYNC_FF决定了仿真时是否使用初始值;参数SIM_ASSERT_CHK用于检查仿真中的问题;参数SRC_INPUT_REG用于是否对输入信号(待跨时钟域信号)在自身时钟下寄存一拍。

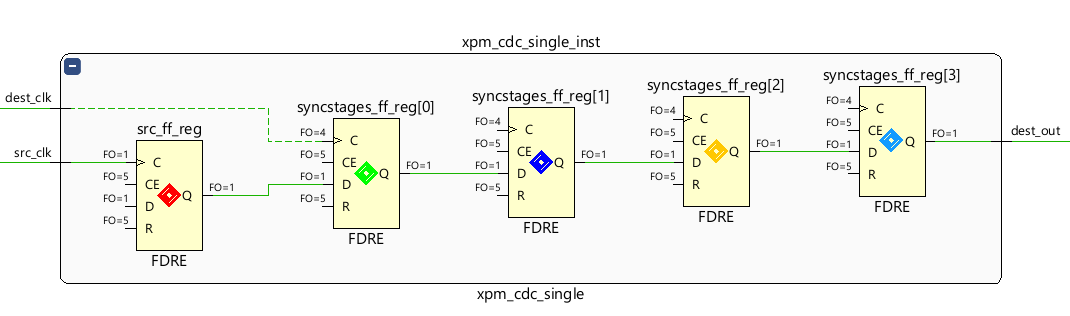

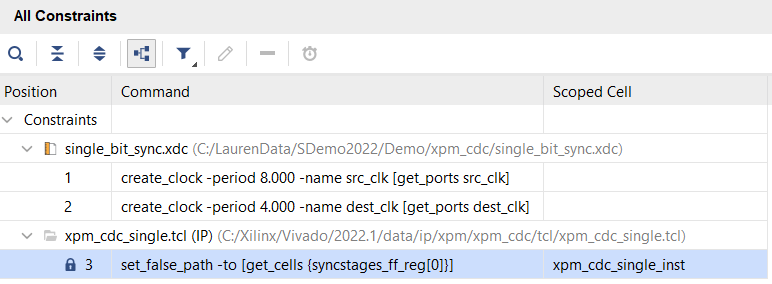

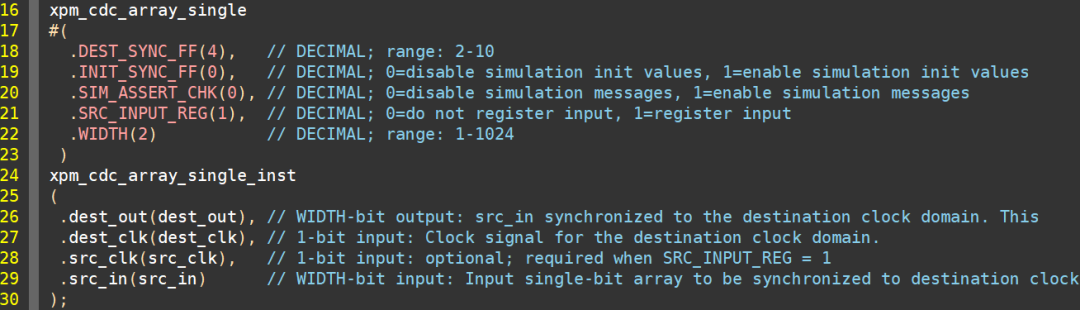

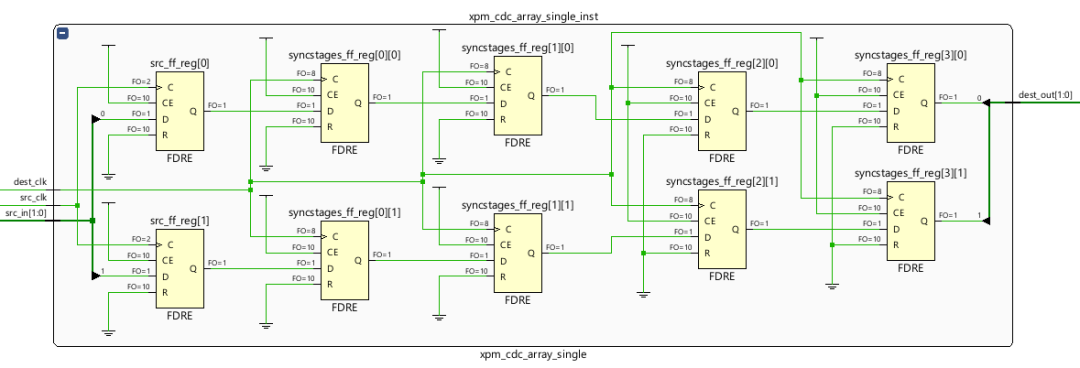

从综合结果来看,当DEST_SYNC_FF设置为4,SRC_INPUT_REG设置为1时,形成如下图所示电路。可用看到第一个触发器位于src_clk时钟域下,后续4个触发器位于dest_clk时钟域下。同时,xpm_cdc_single自带约束将图中红色标记触发器到绿色标记触发器之间的路径设置为伪路径,使用set_false_path约束。

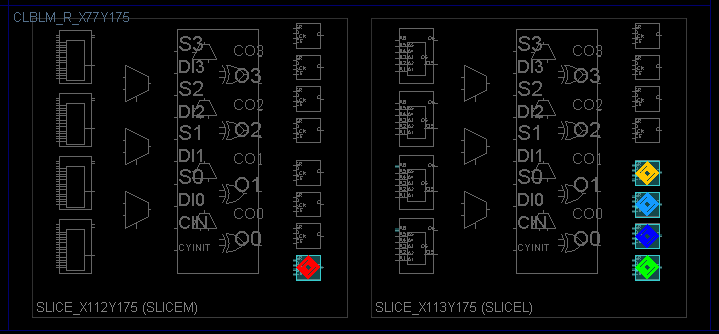

从最终的布线结果来看,工具会将后面4个触发器放置的同一个SLICE内,这是因为这4个触发器的属性ASYNC_REG都被设置为TRUE。

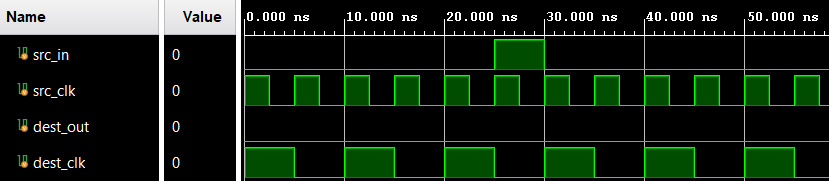

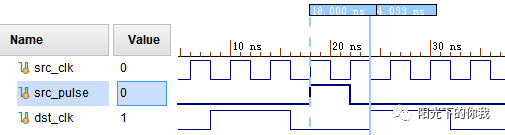

从仿真结果来看,如果出现如下情形,即输入信号在高有效时无法被接收时钟稳定地采样到至少两次,那么仿真就会给出Error信息。

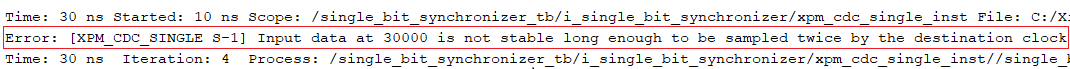

满足此条件时,就不会显示此Error信息。这也告诉我们,工程实践中,要确保待跨时钟域信号在高有效时可以被接收时钟至少稳定地采样到两次。

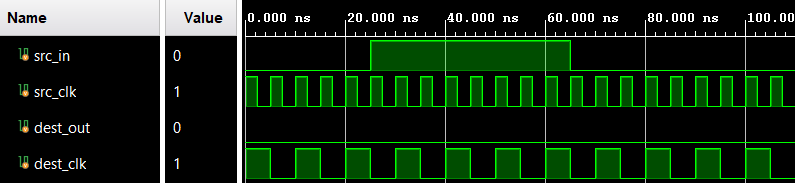

此外,XPM_CDC还提供了xpm_cdc_array_single,与xpm_cdc_single相比只多了一个参数WIDTH,用于指定位宽,但是需要注意的是尽管从形式上看传输的是一个多位宽数据,但实际上,每位是彼此相对独立没有关联的。

例如,位宽为2,综合结果如下,可以看到其实就是两个xpm_cdc_single合并而成。

审核编辑:刘清

-

触发器

+关注

关注

14文章

2000浏览量

61132 -

XPM

+关注

关注

0文章

12浏览量

8670 -

SRC

+关注

关注

0文章

60浏览量

17983 -

时钟信号

+关注

关注

4文章

448浏览量

28542 -

CDC技术

+关注

关注

0文章

9浏览量

6859

原文标题:跨时钟域电路设计(3):单位宽信号如何跨时钟域

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于FPGA的跨时钟域信号处理——MCU

单位宽信号如何跨时钟域

单位宽信号如何跨时钟域

评论