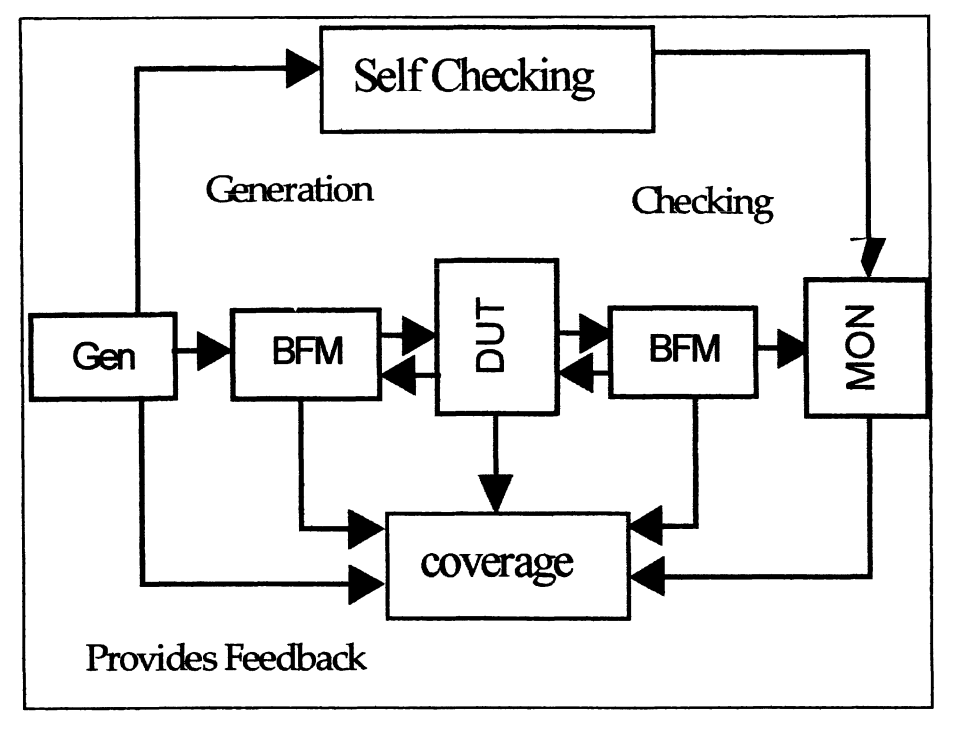

下图是一个典型的EDA仿真验证环境,其中主要的组件就是激励生成、检查和覆盖率收集。

这三者缺一不可。

激励生成是我们验证环境的第一个关键组件,用于驱动DUT到一个预期的状态。

在DUT正在处理激励以及完成激励处理之后我们需要实时的或者离线的checker机制来确保芯片按照预期行为工作。

覆盖率是最终的量化机制、也可以理解为激励的反馈机制。我们不断地激励着DUT,同时也在进行检查,整个过程中通过覆盖率的量化来反馈验证工程师有没有验证完成?哪里还需要继续验证?

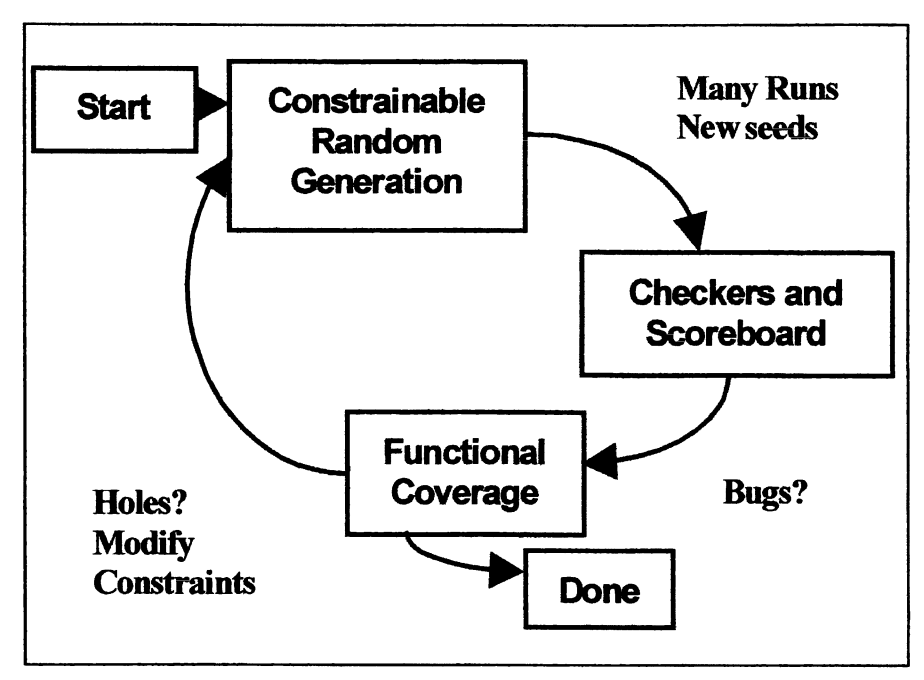

下图是覆盖率反馈到激励,以及表明验证是否完成的一个流程。在这个流程中,我们不断地根据覆盖率调整激励发送的随机机制,直到只剩几个边界场景很难覆盖到,我们再构造定向用例。

这是一个比较高效的现代EDA仿真验证流程,整个流程中激励生成、检查机制和覆盖率量化都需要保证完备性。

完备的激励+完备的检查机制+完备的覆盖率量化才能够获得有信心的验证结果,缺一不可。另外,这三者中的任何一个做到绝对的完备就是非常难的。

如果覆盖率完备了,也可以保证激励的完备。如果发现用例构造过程非常困难,大概率是验证环境架构的不合理。要么趋向于定向用例,你需要维护非常多的sequence,经常一个需求会让你改动多个sequence;要么趋向完全随机,可控性比较差。这两个情况都降低验证效率。

checker是必须要保证完备的,否则就算你激励覆盖到了某个场景,你也识别不出来问题。验证的重点是发现所有的bug,然后才是尽可能地保证激励完备性。如果非要分个优先级,个人觉得checker的完备要高于激励的完备。因为如果你遗漏了某个bug,更上层的验证环境也许可以通过集成你的checker来发现问题。

覆盖率也非常重要。否则就是在黑暗中胡乱开枪射击,你不知道去过哪里,也就不知道后面要往哪里去了。

保证激励、检查和覆盖率的完备,全部都是难点。

审核编辑:刘清

-

eda

+关注

关注

71文章

2785浏览量

173716 -

EDA仿真技术

+关注

关注

0文章

5浏览量

5446 -

DUT

+关注

关注

0文章

189浏览量

12471

原文标题:验证环境中的激励、检查和覆盖率

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Verilog 电路仿真常见问题 Verilog 在芯片设计中的应用

芯华章发布FPGA验证系统新品HuaProP3

EDA与传统设计方法的区别

芯华章生态战略亮相DAC,发布全流程敏捷验证管理器FusionFlex,并联合华大九天推出数模混合仿真解决方案

芯华章推出EDA全流程敏捷验证管理器昭睿FusionFlex

大规模 SoC 原型验证面临哪些技术挑战?

一个高效的现代EDA仿真验证流程

一个高效的现代EDA仿真验证流程

评论