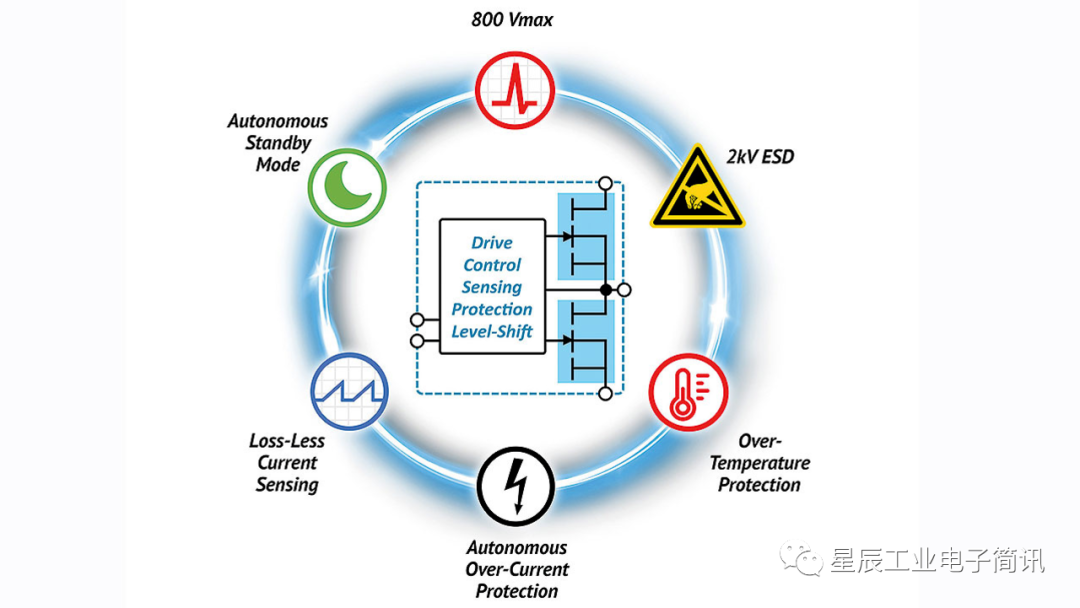

将GaN FET与它们的驱动器集成在一起可以改进开关性能,并且能够简化基于GaN的功率级设计。

氮化镓 (GaN) 晶体管的开关速度比硅MOSFET快很多,从而有可能实现更低的开关损耗。然而,当压摆率很高时,特定的封装类型会限制GaN FET的开关性能。将GaN FET与驱动器集成在一个封装内可以减少寄生电感,并且优化开关性能。集成驱动器还可以实现保护功能

简介

氮化镓 (GaN) 晶体管的开关性能要优于硅MOSFET,因为在同等导通电阻的情况下,氮化镓 (GaN) 晶体管的终端电容较低,并避免了体二极管所导致的反向恢复损耗。正是由于这些特性,GaN FET可以实现更高的开关频率,从而在保持合理开关损耗的同时,提升功率密度和瞬态性能。

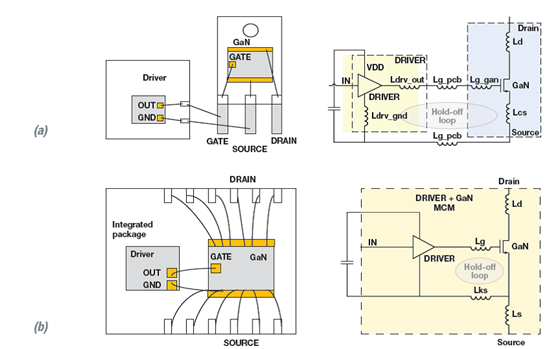

传统上,GaN器件被封装为分立式器件,并由单独的驱动器驱动,这是因为GaN器件和驱动器基于不同的处理技术,并且可能来自不同的厂商。每个封装将会有引入寄生电感的焊线和引线,如图1a所示。当以每纳秒数十到几百伏电压的高压摆率进行切换时,这些寄生电感会导致开关损耗、振铃和可靠性问题。

将GaN晶体管与其驱动器集成在一起(图1b)可以消除共源电感,并且极大降低驱动器输出与GaN栅极之间的电感,以及驱动器接地中的电感。在这篇文章中,我们将研究由封装寄生效应所引发的问题和限制。在一个集成封装内对这些寄生效应进行优化可以减少该问题,并且以高于100V/ns的高压摆率实现出色的开关性能。

图1. 由独立封装内的驱动器驱动的GaN器件 (a);一个集成GaN/驱动器封装 (b)。

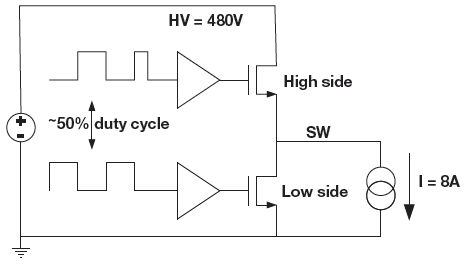

图2. 用于仿真的半桥电路的简化图

仿真设置

为了仿真寄生电感效应,我们使用了一个采用直接驱动配置的空乏型GaN半桥功率级(图2)。我们将半桥设置为一个降压转换器,总线电压480V,死区时间50ns时50%占空比(输出电压 [VOUT] = 240V),以及一个8A的电感器电流。这个GaN栅极在开关电压电平间被直接驱动。一个阻性驱动设定GaN器件的接通压摆率。一个电流源只会仿真一个与连续传导模式降压转换器内开关 (SW) 节点所连接的电感负载。

共源电感

高速开关中最重要的一个寄生要素是共源电感(图1a中的Lcs),它限制了器件汲取电流的压摆率。在传统的TO-220封装中,GaN源由焊线流至引线,而汲取电流与栅极电流都从这里流过。这个共源电感在汲取电流改变时调制栅源电压。共源电感会高于10nH(其中包括焊线和封装引线),从而限制了压摆率 (di/dt),并增加开关损耗。

借助图1b中所示的集成式封装,驱动器接地直接焊接至GaN裸片的源焊垫。这个Kelvin源连接最大限度地缩短了电源环路与栅极环路共用的共源电感路径,从而使得器件能够以高很多的电流压摆率来开关。可以将一个Kelvin源引脚添加到一个分立式封装内;然而,这个额外的引脚会使其成为一个不标准的电源封装。Kelvin源引脚还必须从印刷电路板 (PCB) 引回至驱动器封装,从而增加了栅极环路电感。

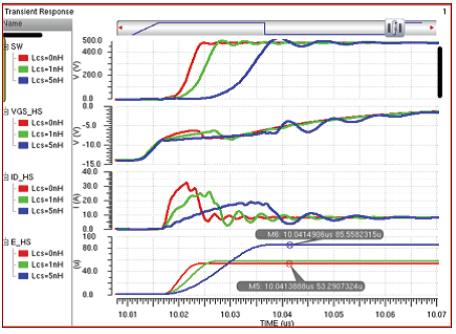

图3.不同共源电感情况下的高管接通:红色 = 0nH,绿色 = 1nH,蓝色 = 5nH。E_HS是高管器件的VDS和IDS在运行时间内的积分值(能耗)。

图3显示的是高管开关接通时的硬开关波形。在共源电感为5nH时,由于源降级效应,压摆率减半。一个更低的压摆率会带来更长的转换时间,导致更高的交叉传导损耗,如能耗曲线图中所示。在共源电感为5nH时,能量损耗从53μJ增加至85μJ,增加了60%。假定开关频率为100kHz,功率损耗则会从从5.3W增加至8.5W。

栅极环路电感

栅极环路电感包括栅极电感和驱动器接地电感。栅极电感是驱动器输出与GaN栅极之间的电感。在使用独立封装时,栅极电感包括驱动器输出焊线 (Ldrv_out)、GaN栅极焊线 (Lg_gan) 和PCB迹线 (Lg_pcb),如图1a中所示。

基于不同的封装尺寸,栅极电感会从紧凑型表面贴装封装(例如,四方扁平无引线封装)的几纳亨到有引线功率封装(例如TO-220)的10nH以上。如果驱动器与GaN FET集成在同一个引线框架内(图1b),GaN栅极直接焊接到驱动器输出上,这样可以将栅极电感减少至1nH以下。封装集成还可以极大地降低驱动器接地电感(从图1a中的Ldrv_gnd + Ls_pcb到图1b中的Lks)。

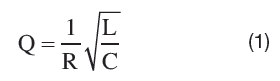

降低栅极环路电感对于开关性能有着巨大影响,特别是在关闭期间,GaN栅极被一个电阻器下拉。这个电阻器的电阻值需要足够低,这样的话,器件才不会在开关期间由于漏极被拉高而又重新接通。这个电阻器与GaN器件的栅源电容和栅极环路电感组成了一个电感器-电阻器-电容器 (L-R-C) 槽路。方程式1中的Q品质因数表示为:

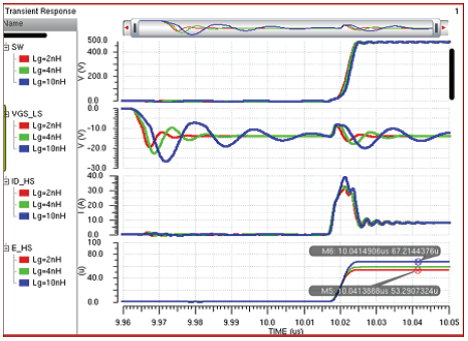

在栅极环路电感值更大时,Q品质因数增加,振铃变得更高。这个效应用一个1Ω下拉电阻关闭低管GaN FET进行仿真,图4中这个效应的出现时间为9.97μs,其中栅极环路电感变化范围介于2nH到10nH之间。在10nH的情况下,低管VGS在负栅极偏置以下产生12V振铃。这就极大地增加了GaN晶体管栅极的应力。需要注意的一点是,任何FET的栅极上的过应力都会对可靠性产生负面影响。

栅极环路电感还会对关断保持能力产生巨大影响。当低管器件的栅极保持在关闭电压时,并且高管器件接通,低管漏极电容将一个大电流传送到栅极的保持环路中。这电流通过栅极环路电感将栅极推上去。图4在大约10.02µs时的曲线变化便是说明了这一点。随着电感增加,低管VGS被推得更高,从而增加了直通电流,这一点在高管漏电流曲线图中可见 (ID_HS)。这个直通电流使得交叉传导能量损耗 (E_HS) 从53µJ增加至67µJ。

图4. 不同栅极环路电感下的低管关闭和高管接通波形:红色 = 2nH,绿色 = 4nH,蓝色 = 10nH。E_HS是高管能耗。

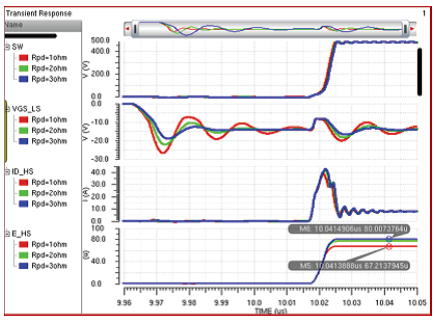

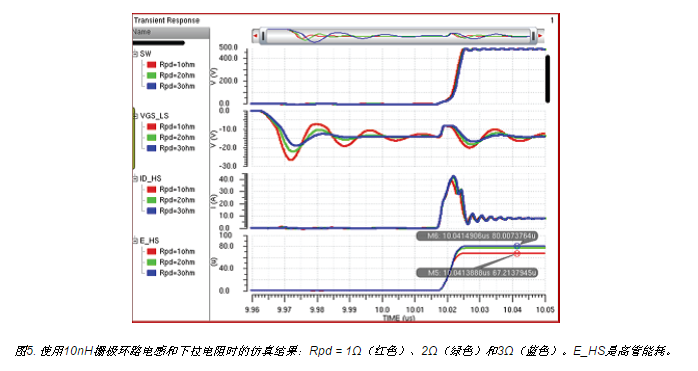

根据方程式 (1),减轻栅极应力的一个方法就是增加下拉电阻值,反过来减少L-R-C槽路的Q品质因数。图5显示的是用一个10nH栅极环路电感和在1Ω到3Ω之间变化的下拉电阻 (Rpd) 进行的仿真结果。虽然栅极下冲被一个3Ω下拉电阻限制在负偏置电压以下的数伏特内,但是关断保持能力恶化,从而导致更大的直通电流。这一点在漏电流曲线图中很明显。

E_HS能量曲线图显示出,在每个开关周期内有额外的13µJ损耗,与2nH的栅极环路电感和1Ω下拉电阻时53µJ相比,差不多增加了60%(图4)。

假定开关频率为100kHz,高管器件上的功率损耗从5.3W增加至8W,其原因是由高栅极环路电感和高下拉电阻值所导致的直通。这个额外的功率损耗会使得功率器件内的散热变得十分难以管理,并且会增加封装和冷却成本。

图5. 使用10nH栅极环路电感和下拉电阻时的仿真结果:Rpd = 1Ω(红色)、2Ω(绿色)和3Ω(蓝色)。E_HS是高管能耗。

为了减轻直通电压,可以将栅极偏置为更大的负电压,不过这样做会增加栅极上的应力,并且会在器件处于第三象限时增大死区时间损耗。因此,在栅极环路电感比较高时,栅极应力与器件关断保持能力之间的均衡和取舍很难管理。你必须增加栅极应力,或者允许半桥直通,这会增加交叉传导损耗和电流环路振铃,并且会导致安全工作区 (SOA) 问题。一个集成式GaN/驱动器封装提供低栅极环路电感,并且最大限度地降低栅极应力和直通风险。

GaN器件保护

将驱动器与GaN晶体管安装在同一个引线框架内可以确保它们的温度比较接近,这是因为引线框架的导热性能极佳。热感测和过热保护可以置于驱动器内部,使得当感测到的温度超过保护限值时,GaN FET将关闭。

一个串联MOSFET或一个并联GaN感测FET可以被用来执行过流保护。它们都需要GaN器件与其驱动器之间具有低电感连接。由于GaN通常以较大的di/dt进行极快的开关,互联线路中的额外电感会导致振铃,并且需要较长的消隐时间来防止电流保护失效。集成驱动器确保了感测电路与GaN FET之间尽可能少的电感连接,这样的话,电流保护电路可以尽可能快的做出反应,以保护器件不受过流应力的影响。

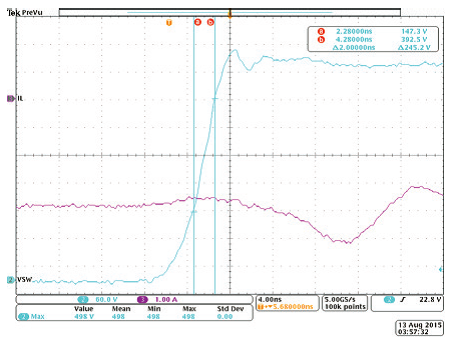

图6. 一个半桥降压转换器(通道2)中的高管接通时的SW节点波形。

开关波形

图6是一个半桥的开关波形;

这个半桥包含2个集成式驱动器的GaN器件,采用8mm x 8mm四方扁平无引线 (QFN) 封装。通道2显示SW节点,此时高管器件在总线电压为480V的情况下,以120V/ns的压摆率被硬开关。这个经优化的驱动器集成式封装和PCB将过冲限制在50V以下。需要说明的一点是,捕捉波形时使用的是1GHz示波器和探头。

结论

GaN晶体管与其驱动器的封装集成消除了共源电感,从而实现了高电流压摆率。它还减少了栅极环路电感,以尽可能地降低关闭过程中的栅极应力,并且提升器件的关断保持能力。集成也使得设计人员能够为GaN FET搭建高效的过热和电流保护电路。

审核编辑:郭婷

-

MOSFET

+关注

关注

147文章

7199浏览量

213618 -

晶体管

+关注

关注

77文章

9705浏览量

138470 -

氮化镓

+关注

关注

59文章

1639浏览量

116432 -

GaN

+关注

关注

19文章

1946浏览量

73675

发布评论请先 登录

相关推荐

如何用集成驱动器优化氮化镓性能?

供应SW1102集成氮化镓直驱的准谐振模式反激控制IC

供应SW1108P集成氮化镓直驱的高频准谐振IC

NV6115氮化镓MOS+NCP1342主控芯片PWM控制器丝印1342AMDCD

如何用集成驱动器优化氮化镓性能

用集成驱动器优化GaN性能

好马配好鞍——镓未来氮化镓和纳芯微隔离驱动器比翼双飞,助力氮化镓先进应用

集成氮化镓电机驱动器分析

用集成驱动器优化氮化镓性能

用集成驱动器优化氮化镓性能

评论