6 回路电感

现实设计中,电流是在一个完整的回路中流动,此完整电流回路的总电感称为回路电感,又称为回路自感。即当回路中流过1安培电流时,从信号源出发,沿着导线行走时,整个回路中所有电流产生的磁力线总匝数。

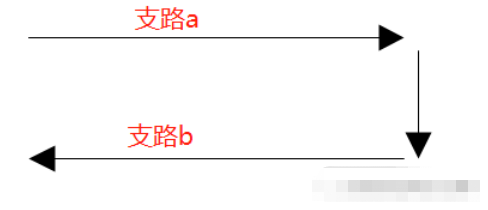

以支路a和支路b组成的回路为例,整个回路的自感

Lloop=La-Lab+Lb-Lab=La+Lb-2Lab

Lloop是整个回路的回路自感。Lab是支路a和支路b之间的局部互感。La和Lb是各自支路的自感。此公式说明,当两支路靠近时,各自的支路自感不变,两支路之间的互感增大,导致回路自感减小。

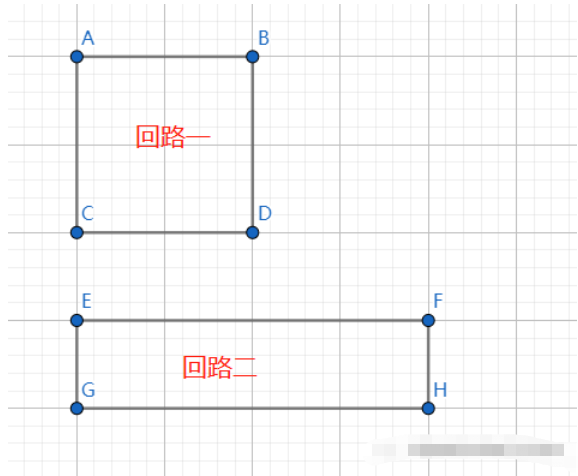

很多时候,我们在做PCB设计时,都要求回路面积尽量小,其实这只是一个笼统的说法。更关键的在于回路中两支路的距离是否近。如下图是2个面积一样,但是回路电感不同的设计。当此回路中两个支路电流方向相反时,回路二的互感更大,整个回路电感更小。

下面有三种特殊结构的回路电感。

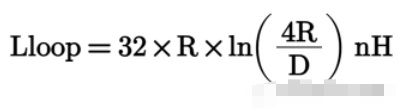

第一种:环形线圈回路的回路电感公式

R是线圈半径,单位是in;D是构成线圈的导线直径,单位是in。Lloop的单位是nH。从以上公式可以看出,此种回路的电感不是与圆环的面积或者周长成正比。而是与圆环的半径乘以半径的对数成正比。因为圆环周长越长,每一段的局部自感就越大。但同时,回路中相反方向的电流距离越远,相互之间的互感越小。

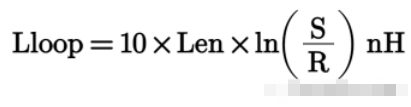

第二种:两根相邻的直圆杆,其中一条为另一条的返回电流路径。它们的回路电感公式

Len是圆杆长度,单位是in;R是圆杆半径,单位是mi;S是两圆杆之间的间距,单位是mil,Lloop的单位是nH。此公式说明两根平行导线的回路电感和导线的长度成正比,与中心距离的自然对数成正比。注:自然对数变换相对缓慢。此种情况和两条扁平PCB走向有点像。

第三种:两个宽平面。在下一篇文章中有说明。

注意:任何阻抗可以控制的互连线,它的单位长度回路电感都是恒定的。

7 电源分布系统(PDS)和它的回路电感

7.1电源分布系统

电源分布系统就是电源和负载、以及它们之间的电源路径和地路径。此系统也会影响到信号完整性。在PDS中,从电源到负载,中间有很多的互连线,还有过孔、电源平面或者地平面、封装引线、键合线等。当进入芯片的电流发生变化时(例如LPDDR4的数据在快速的变化,即逻辑门在快速的开和关),电源和负载之间PDS的这些互连线等因素的阻抗就会引起电压降,称为轨道下降或者轨道塌陷。要使电流变化引起的电压降最小,PDS的阻抗就要小于一定的值。这样即使电流还在变化,引起的电压降也还在负载可以接受的范围之内。

7.2降低PDS阻抗的办法

方法一:使用电源平面和地平面传输电流。电源平面和地平面比电源走线和地走线更好的原因,就在于电源平面和地平面的回路电感非常低,造成的电压降更小。

方法二:在低频段,使用低阻抗的去耦电容。高频段,使去耦电阻和负载焊盘间的回路电感最小,以保持它们之间的阻抗低于一定值。

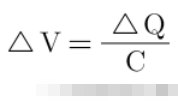

那么使用多大的去耦电容合适呢?原则是依据在时间段△t内,去耦电容必须提供的电荷量来大致估算。因为在△t时间内,会有△Q的电荷从电容上向芯片释放,这个动作会导致电容上电压下降△V。即

而在此时间段内,芯片需要的电流由芯片自身决定,例如对SOC而言,就要看那个时间段,它处于什么状态,运行功耗是多少?运行功耗又和它的供电电压,以及需要消耗的平均电流有关。假设它需要的电流是I、功耗是P、供电电压是V,则

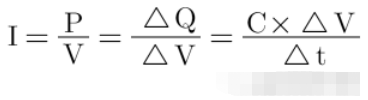

通常大多数芯片要求电压纹波不超过正常值的5%,因此

△t的单位是秒,C的单位是法拉,V的单位是伏,P的单位是瓦特。

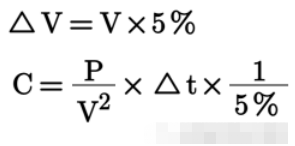

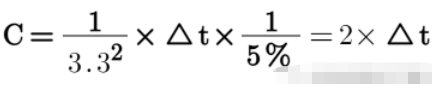

例如一个小的Nor flash,工作电压是3.3V,假设其功耗是1W,则需要的总去耦电容量是

如果给Nor flash供电的LDO没办法在10us之内对Nor flash的耗电做出足够的反应,则需要在LDO和Nor flash之间提供20uF的去耦电容。如果去耦电容量小于这个值,Nor flash的供电电压纹波会大于5%。

7.3去耦电容带来的回路电感

针对上面提到的例子,不建议使用单个20uF的去耦电容。应该将多个电容器并联使用。目的是多个电容并联使用,可以降低回路电感。因为实际电容器管脚和Nor flash的电源pin焊盘之间有PCB走线,这段走线会有相应的回路电感。此回路电感和电容串联,导致电容的阻抗随着频率的上升而增大。

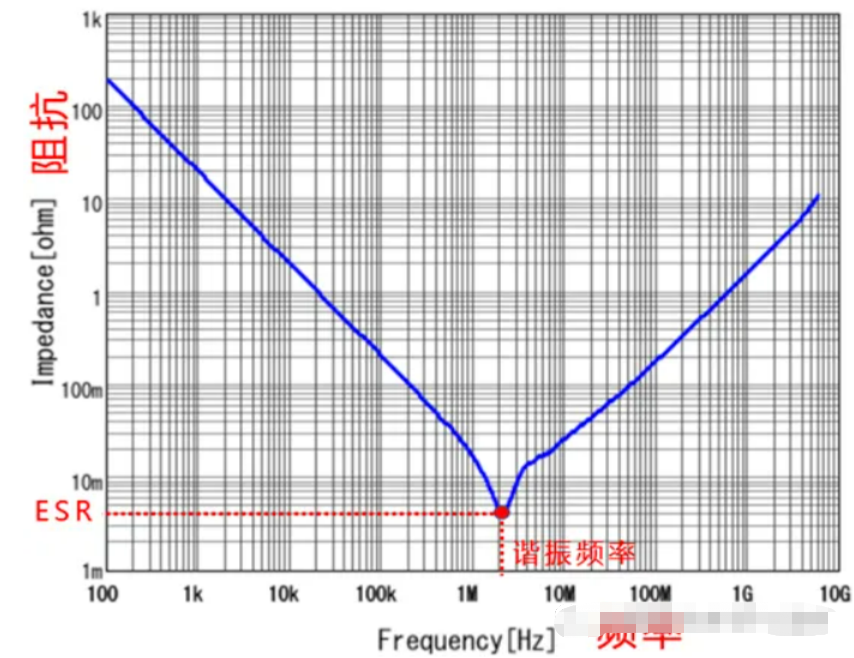

下图是一颗电容的阻抗曲线。在2MHz以下,它就像理想电容一样,阻抗随着频率增大而减小。从2MHz开始,串联的回路电感开始起主导作用。把2MHz称为自谐振频率,从此点开始,阻抗增大。注:当越过自谐振频率点之后,电容的阻抗和电容量没有关系了,只与相关的回路电感有关。因此要想在频率较高点,减小去耦电容的阻抗,就要减小去耦电容相关部分的回路电感(如上面提到的减小去耦电容管脚到负载芯片电源pad之间的距离和回路电感),单纯的增加电容量是没有用的。

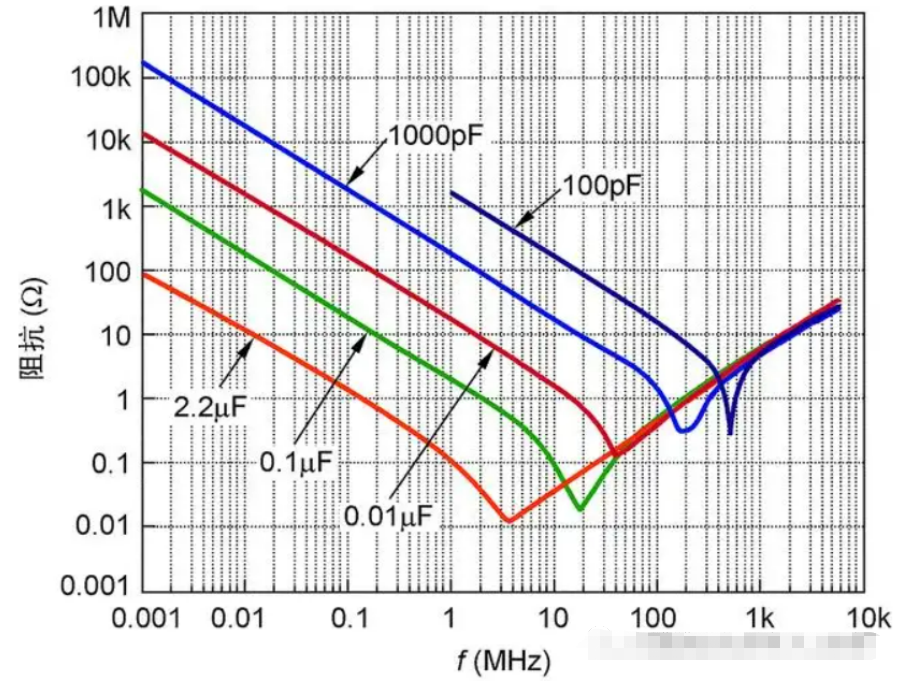

下图是5个电容量不同但都是0603封装的电容阻抗测试结果。可以看出在低频段时,电容量的容值不同,因此阻抗各有差异。在高频段,因为封装结构相同,阻抗也趋于一致。因此高频段曲线和电容容值没关系,和电容的封装、电容到负载电源pad的走线有关系。

7.4总结

总结:减小去耦电容回路电感的几种方法

①电源和地走线都用平面,这是回路电感最小的一种互连线结构。

②尽量减小电源平面和地平面的间距

③使电源平面层和地平面层,尽量靠近电路板的表层,以缩短过孔距离

④使用封装小的电容

⑤电容焊盘到过孔距离、电容焊盘到负载管脚的距离尽量短。同时此段走线要远离PCB的IO端口,降低对外的EMI辐射。

⑥多个电容器并联使用

⑦电容焊盘到负载管脚的走线和返回路径,设计成回路电感最小的方式

-

电源

+关注

关注

185文章

17953浏览量

252755 -

pcb

+关注

关注

4333文章

23223浏览量

401854 -

信号源

+关注

关注

5文章

483浏览量

44758 -

电感

+关注

关注

54文章

6161浏览量

102962 -

信号完整性

+关注

关注

68文章

1418浏览量

95845

发布评论请先 登录

相关推荐

信号完整性之电感的知识(二)

信号完整性之电感的知识(二)

评论