一、I2C总线的介绍

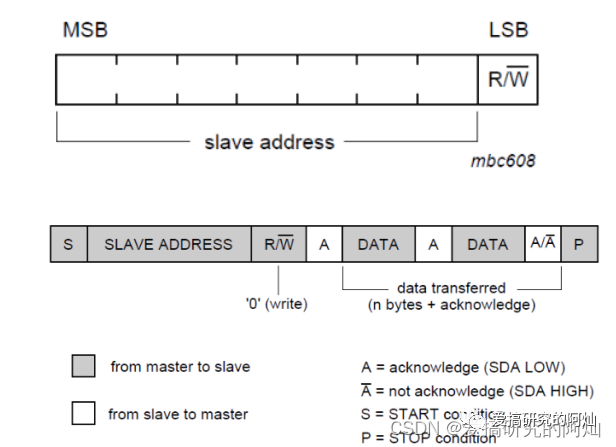

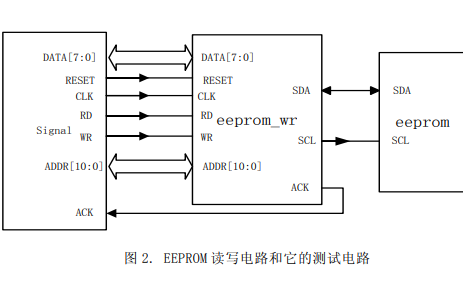

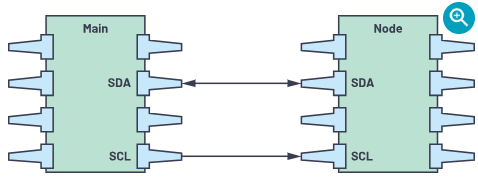

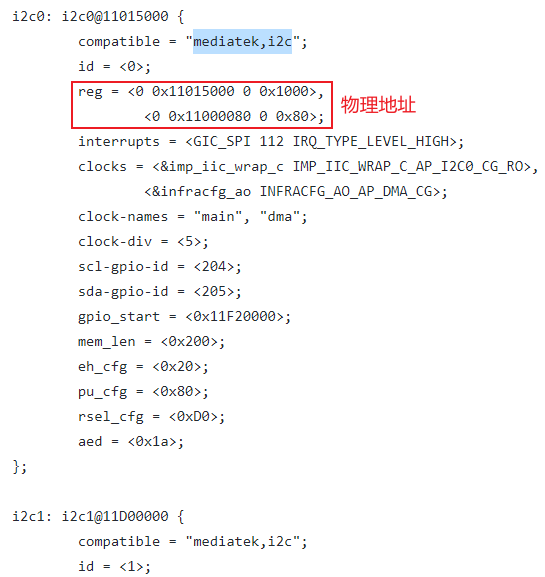

I2C是一种非常常见的通信协议,是philips公司提出的,由数据线SDA和时钟线SCL两条双向信号线组成,CPU利用串行时钟线发出时钟信号,利用串行数据线发送或者接受数据。SDA线传输数据是大端传输(字节高位先传),每次传输8bit,即1字节。支持多主控,任何时间点只能有一个主控。每个连接到总线的设备都有一个独立的地址addr,共7个bit,主机正是利用该地址对设备进行访问(这是I2C和SPI最大的不同点之一,I2C对从设备进行操作需要知道从设备地址,然后进行寻址;而SPI则不需要通过设备地址寻址)。

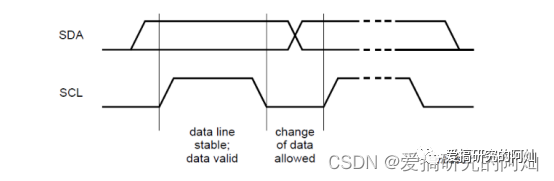

当总线空闲的时候,SDA和SCL都是高电平。在数据传输过程中,SCL为高电平的时候,SDA线必须保持稳定,SDA上传输1个bit数据;当SCL为低电平的时候,SDA线才可以改变电平。简言之,只有当SCL为高电平时,SDA的数据才有意义。

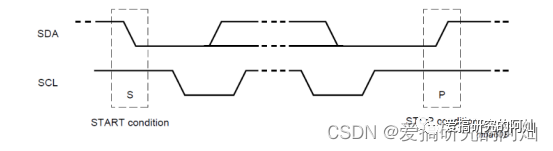

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。起始信号由主控制器产生。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。结束信号也只能由主控制器产生。

(记忆窍门:因为总线空闲时两根线都是高电平,所以开始信号是由高电平变为低电平;而结束信号是要回到总线空闲的状态,所以是从低电平变为高电平)

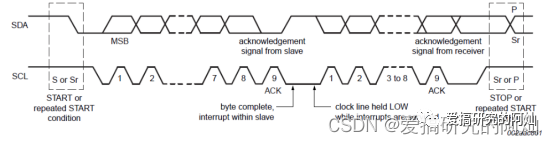

发送到SDA线上的每个字节必须是8位,每次传输可以发送的字节数量不受限制,每个字节后必须跟一个ACK应答位,数据从最高有效位(MSB)开始传输。

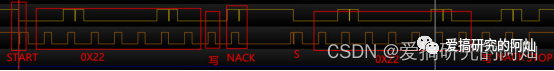

主机每发送完8bit数据后等待从机ACK。即在第9个clock,若从机发回ACK,SDA会被拉低。若没有ACK,SDA会被置高,这会引起主控发生RESTART或STOP流程。根据近期实际开发经验,主机在第一次寻址失败后,会再次寻址,如果两次都失败,那么SDA就会把电平拉高(同时SCL处于高电平状态),结束通信。

I2C总线上的所有数据都是以8位字节传送的,发送器每发送一个字节,就在时钟脉冲9期间释放数据线,由接收器反馈一个应答信号。应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节;应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。(无论是发送地址还是数据,其后都紧跟着一个ACK/NACK。ACK和NACK由slave提供。)

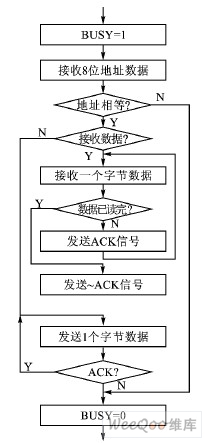

如果从机要在完成一些其他功能之后才能接收或发送下一个完整的数据字节,则可以使时钟线SCL 保持低电平,从而迫使主机进入等待状态。当从机准备好接收下一个数据字节,并且释放时钟线SCL 后,数据传输继续。

当主控器接收数据时,在最后一个数据字节,必须发送一个非应答信号(NACK),使受控器释放数据线,以便主控器产生一个停止信号来终止总线的数据传送。

在起始信号结束后,发送一个7bit的从设备地址,然后紧跟着读写标志位(“0”表示写,“1”表示读)。如果从设备有回应,就可以继续读写数据,具体读写哪个寄存器也要有所说明。

二、逻辑分析仪抓取总线波形

在实际工作中可以使用逻辑分析仪抓取I2C总线的波形进行排故。

由于我手上只有杜邦线,缺少逻辑分析仪专用的数据线(一头带夹子,如下图所示),没有办法在连接外设的同时抓取波形,所以此处只能简单抓取主设寻址外设的波形。

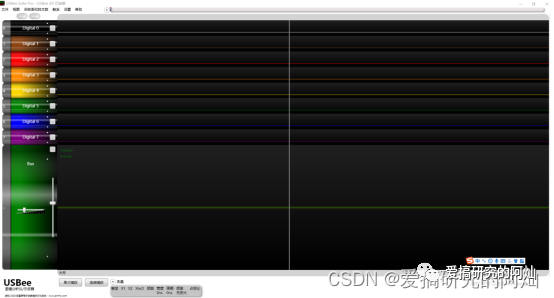

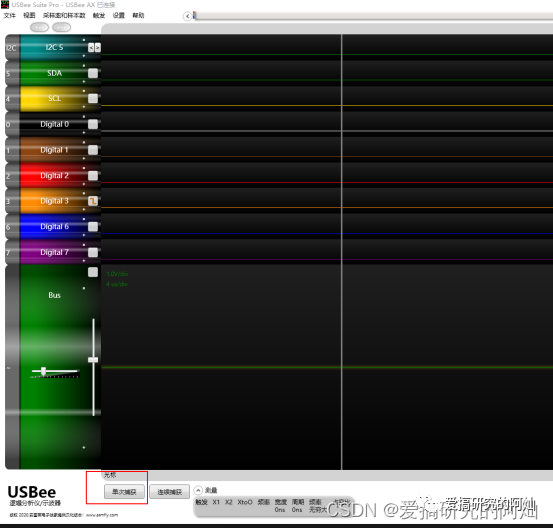

抓取波形使用的软件是USBee Suite,如下图所示:

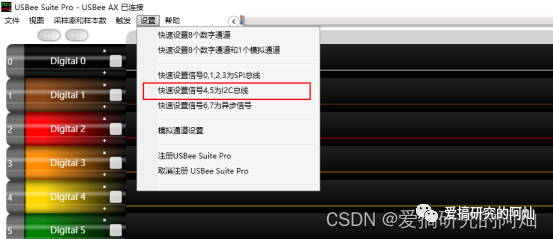

快速设置信号4,5为I2C总线,这种设置方法也决定了硬件上的连接。

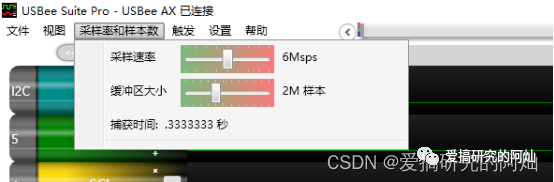

设置采样率和样本数如图所示:

设置下降沿触发(倒数第3个信号通道,软件上标注的SDA和SCL并不是实际上的SDA和SCL,这是一个软件BUG,根据波形来判断,有规律的进行跳变的就是SCL, 另外一个是SDA.):

使用单次触发方式捕获波形:

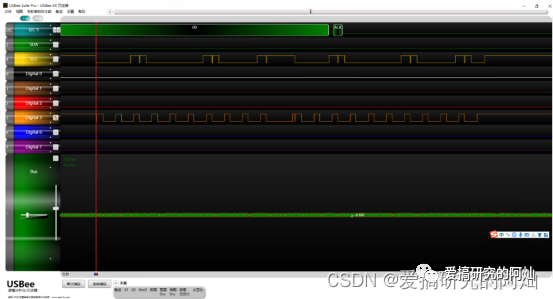

实际捕获到的波形如下图所示:

根据波形可以看出,GM5主设两次寻址地址为0X22的从设备,但是没有收到从设备的回应(NACK),最终主设停止了本次通信。

原文标题:二、逻辑分析仪抓取总线波形

文章出处:【微信公众号:爱搞研究的阿灿】欢迎添加关注!文章转载请注明出处。

-

网络通信

+关注

关注

4文章

815浏览量

30106 -

I2C总线

+关注

关注

8文章

406浏览量

61225 -

逻辑分析仪

+关注

关注

3文章

214浏览量

23310 -

I2C通信

+关注

关注

0文章

22浏览量

8937

发布评论请先 登录

相关推荐

HT45R37使用I2C进行数据传输的方法 (C语言)

HT56R678使用I2C进行数据传输的方法

HT56R678使用I2C进行数据传输的方法

模拟I2C总线多主节点通信原理及实现方法

I2C总线的结构介绍

I2C通信协议应该如何学习

硬件I2C与模拟I2C

I2C通信协议:了解I2C Primer、 PMBus和SMBus

UART、SPI、I2C比较 串口通信介绍

I2C通信介绍及软测方法

I2C通信介绍及软测方法

评论