11 分支走线对信号反射的影响

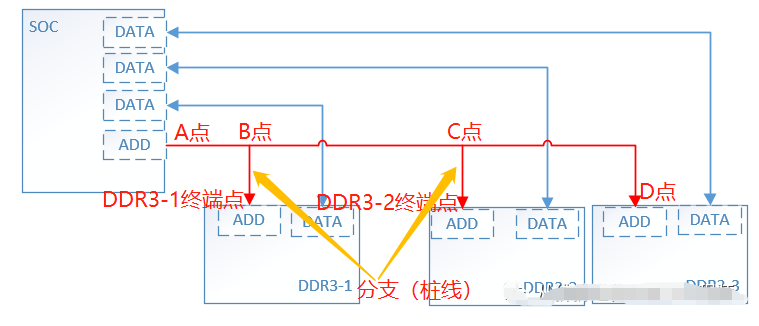

有些设计中可能是三个或者更多芯片在同一个信号链路上,按照flyby拓扑结构布局。如下图是一颗SOC和3颗DDR3的PCB布局设计。因为三颗DDR3的ADD是共用一组来自SOC的信号线,因此只有ADD信号线有分支一说,黄色箭头所示即为分支,也称为桩线。除了PCB板上的走线,芯片封装中的走线也是桩线的组成部分。这些分支是影响信号反射波形的因素之一。DATA线是SOC和DDR点对点传输的,没有分支。(注:此处仅仅是举例,现实设计中,通常SOC的一组DDR端口驱动2颗DDR3芯片,SOC的另一组DDR端口驱动另外1颗或者2颗DDR3芯片)。

信号从SOC端(A点)输出后,当传输到第一个分支时(B点),遇到的阻抗是两端传输线的并联阻抗,即在此分支遇到的阻抗会下降,因此在此阻抗变化点,会有负反射发生,有负反射波形返回SOC。同时另一部分的信号将沿着两个分支继续传播(一个向DDR3-2方向传播下去,另一个向DDR3-1方向传输)。当信号到达DDR3-1终端时,可能会有反射发生,从DDR3-1终端反射回分支点(B点),再从A点反射回DDR3-1终端,即在DDR3-1的这一段分支上来回反射。类似的情况也会在分支C点、D点发生。因此A点、B点、C点、D点、DDR3-1终端点、DDR3-2终端点的波形,是这些分支的反射波形的组合。它们的计算是极其复杂的,通过仿真电路得到仿真波形是比较高效的办法。

针对分支走线对信号的影响,做仿真如下:

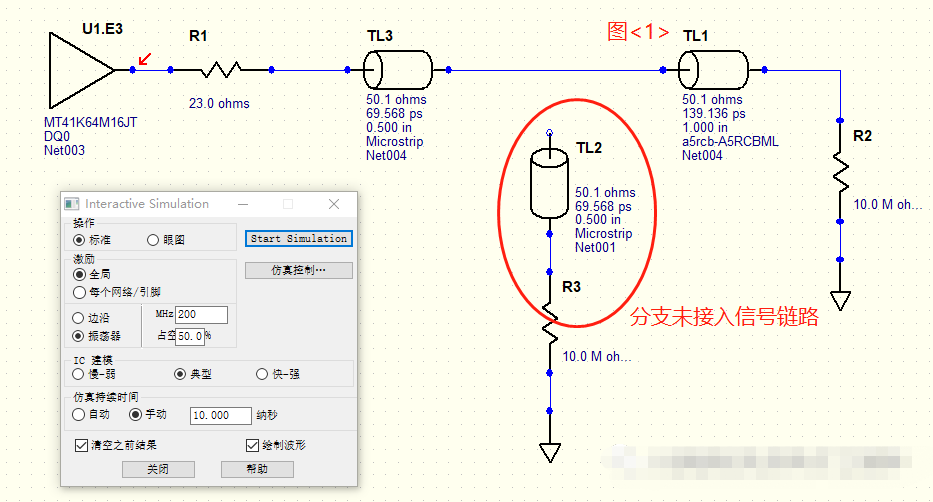

(一)没有分支时的仿真

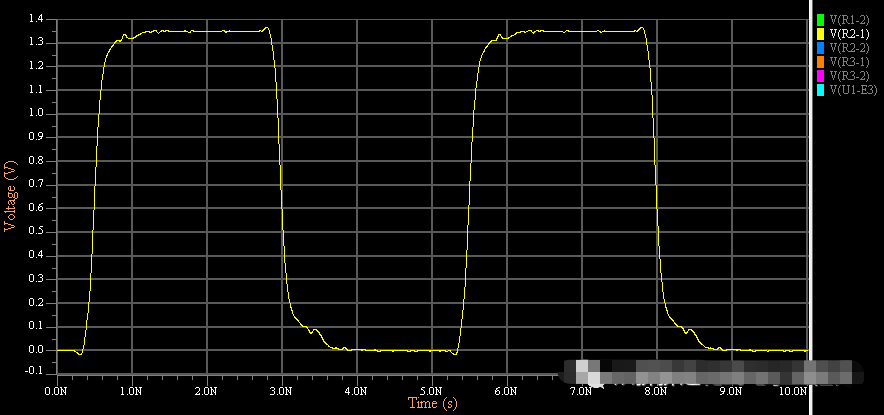

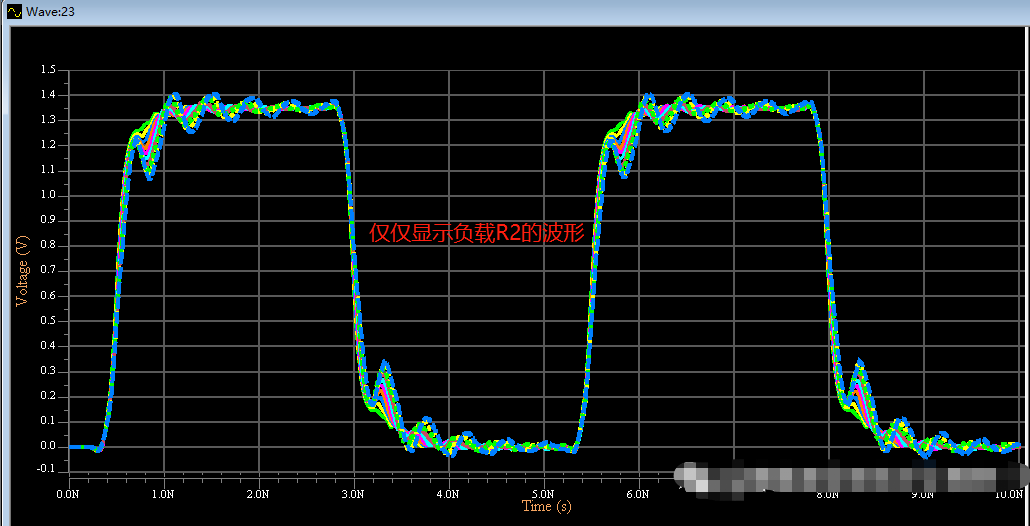

仿真结果如下:负载端R2的波形看起来还不错,没有反射振铃,过冲和下冲也很小。

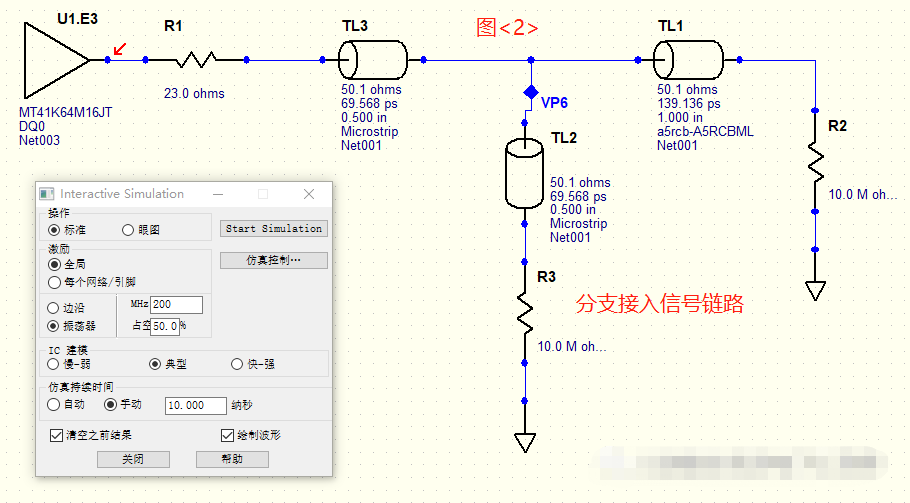

(二)有分支走线存在时的仿真

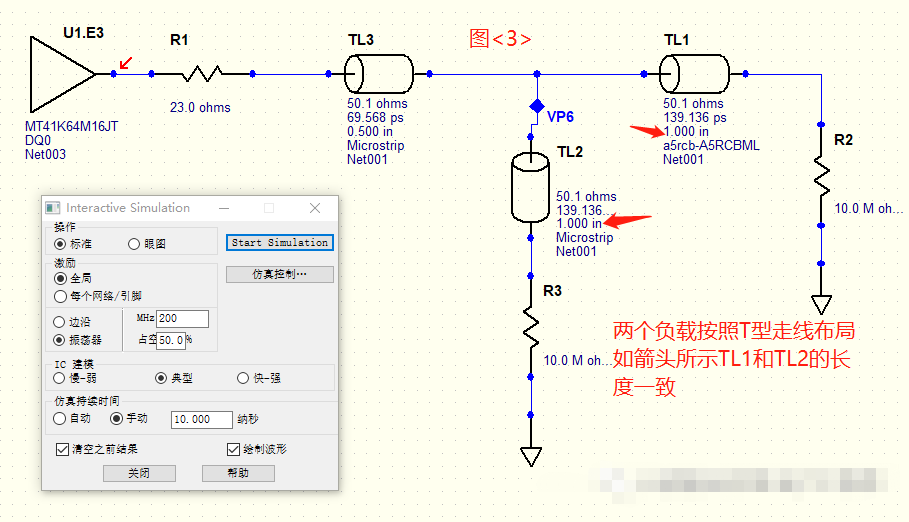

仿真电路如下:分支TL2和R3已经接入信号路径。

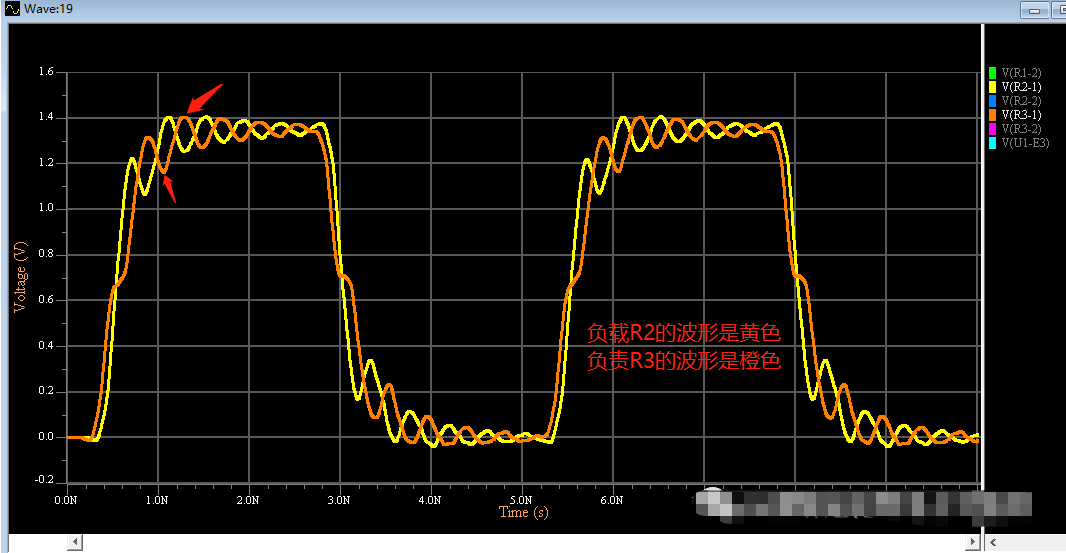

如下是有分支存在时的波形。可以看到负载R2和负载R3上的波形非常的差。明显的多次振铃,幅度也超过信号电压幅度的±5%。

针对这种设计,怎么修改才能是信号满足负载端的需求呢?

(三)如果仿真电路只有2个负载,可以考虑T型拓扑

在上图<2>中,TL1长度为1in,TL2长度为0.5in。即负载R3距离源端近,负载R2距离源端远。因为只有两个负载,可以修改设计如下图<3>所示,TL1=TL2=1in,即两负载距离源端一样,按照T型结构布局和走线。

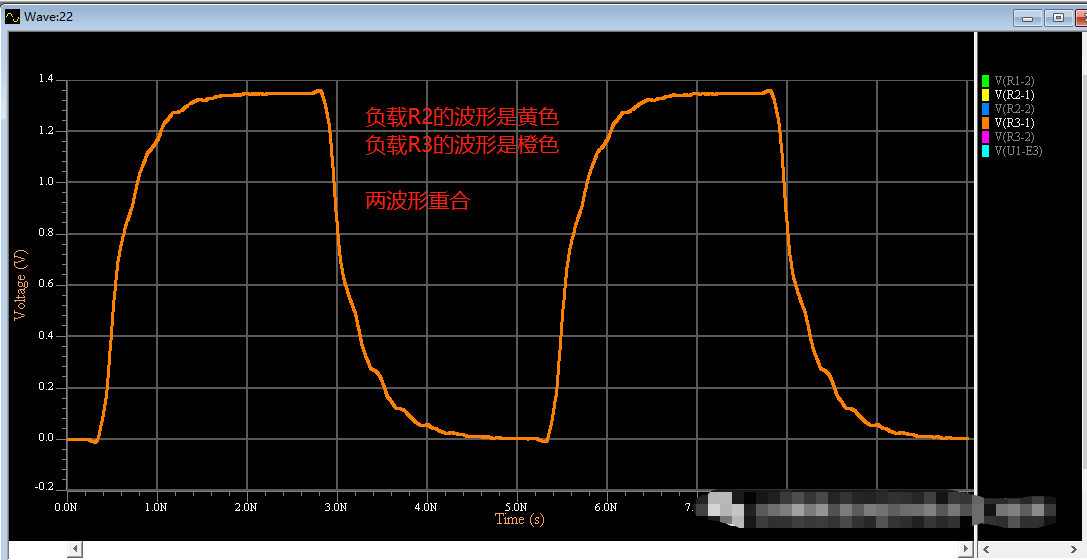

仿真结果如下:两负载的波形完全重合,也没有过冲、振铃之类的失真。

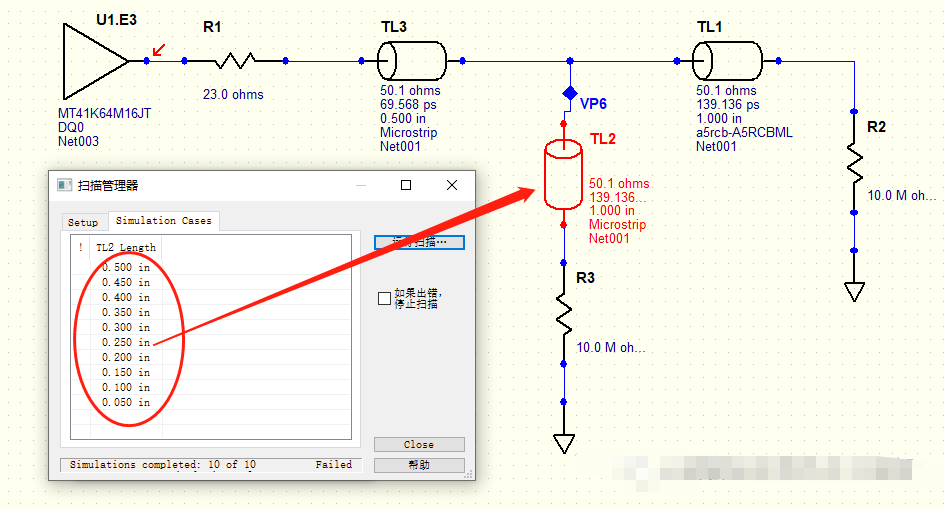

(四)如果多于2个负载的拓扑结构,尽量缩短TL2等的距离

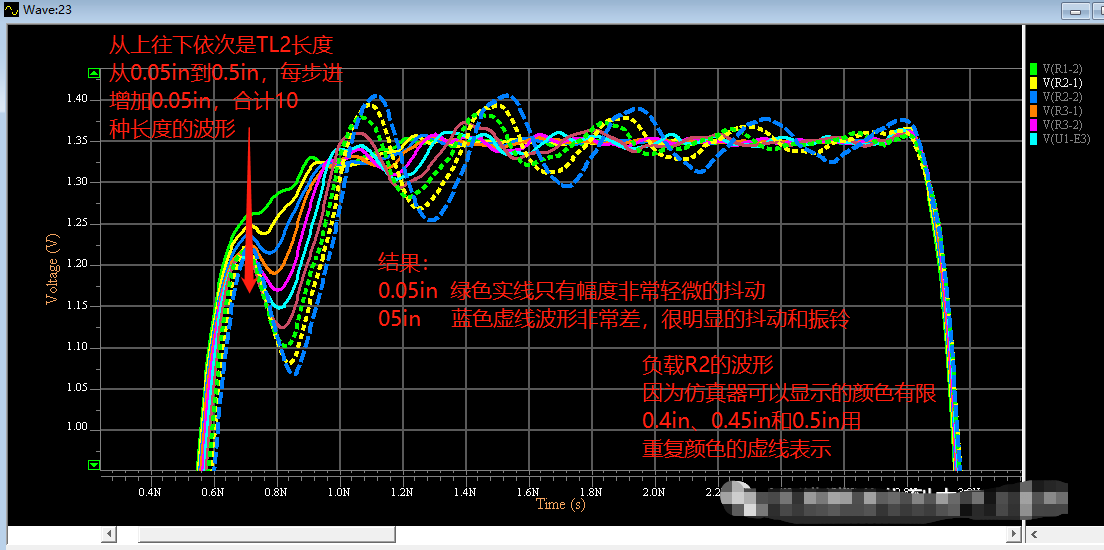

如下图,针对TL2的不同长度做信号仿真。

如下是TL2在不同长度下的负载R2的波形

局部放大后,可以看到。TL2=0.05in的是绿色实线波形,只有幅度很轻微的抖动。最严重的是TL2=0.5in蓝色虚线波形,抖动和振铃非常明显。其他波形随着TL2长度的缩短,质量越来越好。

结论:多负载设计时,如果是两个负载,考虑按照T型拓扑设计。如果大于两个负载,按照Flyby拓扑结构设计时,每个分支的走线都尽量短。在PCB出图前,最好结合实际PCB叠层参数、PCB走线参数进行仿真,调整到比较优化的阶段。

-

芯片

+关注

关注

455文章

50812浏览量

423581 -

pcb

+关注

关注

4319文章

23099浏览量

397850 -

DDR3

+关注

关注

2文章

276浏览量

42269 -

信号完整性

+关注

关注

68文章

1408浏览量

95488 -

信号反射

+关注

关注

0文章

16浏览量

10463

发布评论请先 登录

相关推荐

信号完整性(五):信号反射

信号完整性简介及protel信号完整性设计指南

信号完整性之反射(五)

信号完整性之反射(五)

评论