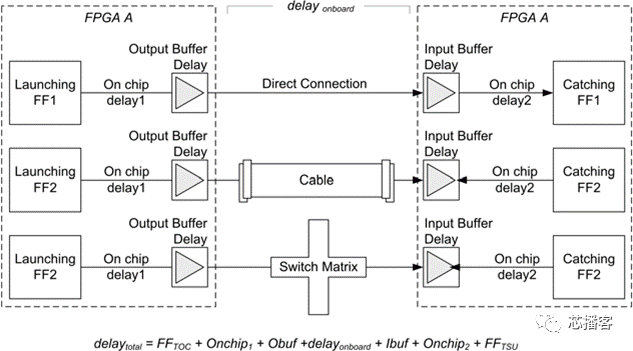

FPGA与FPGA之间互连对信号延迟的影响,两片FPGA的IO之间每一个额外的过渡,例如连接器、焊点甚至板内通孔,都会增加一些阻抗,从而降低信号质量,并增加信号之间串扰的概率。然而,经过仔细分析,发现这并不是一个想象中的大问题。主要矛盾是FPGA互连线的影响。比如,我们可以以如下图所示的三种连接模型方式表示:

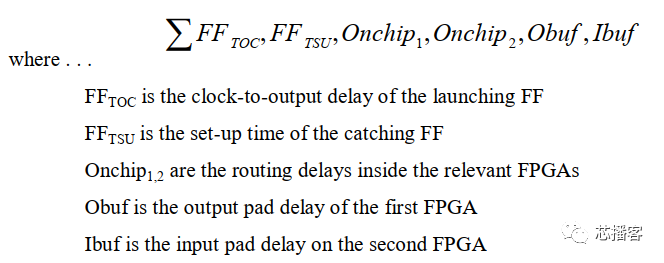

路径延迟由上图所示的表达式给出。每个互连方法的共同点是延迟分量,它是所有片内延迟和片内/片外延迟的总和,每个变量的意义如下表示为:

三种连接方式,除了Delay onborad这个时间不尽相同,其他时间是一样的,都是板间的各种连线以及器件的延迟之和,所以决定性因素还在于Delay onbaord时间,Direct Connection是最快的,Cable线互连和Switch连接方式的延迟会更长一些。当然,取决于FPGA原型验证供应商的PCB能力如何。因为Cable线的延迟大家基本都会选择专业的做线缆的公司提供的线缆。这么看来,站在不同的角度来看,这个速率的影响因素就各不相同了,如果你是FPGA供应商,那么提升自身PCB设计能力是基础,选择Cable是另一个方面。如果你是SoC供应商,那么,不同厂商的不同连接方式都需要考虑。

除了以上因素,还有其他RTL设计相关相关因素:

1. SoC设计中RTL的风格以及如何有效地将其映射到FPGA中

2. 设计中互连的复杂性,尤其是总线

3. 使用没有FPGA等效的IP块

4. 每个FPGA的资源利用率(50%左右是合理的)

5. FPGA之间互连的信号复用比(TDM比)

6. 将快速IO数据导入FPGA核心的速度

在典型的设计中,FPGA交换互连的IO之间信号的传播延迟时间不太容易预测,因为为了路由整个设计,一些信号必须通过多个转换元件。平均来说,有两次转换的遍历,但在非常大的设计的极端情况下,这可能高达八次,可能该设计被划分为多达20个FPGA设备。为了确保关键路径穿过尽可能少的转换电路,FPGA原型验证系统供应商必须开发并支持布线优化工具。此外,如果此布线任务可以在相关工程师的控制下进行,则工具的选项将变得非常广泛。这种并发分区和布线工具将在基于交换互连的系统上提供最佳结果,因此我们再次看到了为板提供复杂支持工具的好处。

PCB电路板设计和布局的质量也是关键

整个FPGA原型验证工作中,让设计以非常高的速度运行是一项重要的任务,因为要最接近真实的模拟未来芯片的工作场景。因此必须能够依靠FPGA的硬件电路板每次都能达到最高速率规格。如果FPGA原型验证供应商交付的产品在硬件性能上有明显差异或批次之间或同一批次中的电路板之间存在延迟,则表明硬件电路板设计质量不高。

例如,对于以100MHz以上的速度运行的接口(如PCIe或DDR3等接口的本地操作所需),该接口必须在其FPGA上具有快速引脚以及PCB本身的稳健设计和布局。要做到这一点,特别是使用最新的高引脚数FPGA,需要具有非常多层的复杂电路板设计。例如,很少有电路板供应商能够设计和建造40层电路板。本身必须做到长度和阻抗匹配,以允许远程同步点之间的差分信号和延迟匹配。当在多个FPGA之间划分任何给定设计时,这将允许更大的自由度。

对高质量可再现板性能的需求尤其适用于时钟和重置网络,其不仅必须足够灵活以允许各种时钟源和速率,而且还必须在分布式时钟网络的每个点提供良好的时钟信号。

电源也是设计的关键部分,初级FPGA核心和IO电压轨引脚的低阻抗、高电流路径是特别是在每个时钟周期在FPGA之间切换许多信号的设计上。

第一次检查时,使用相同FPGA的两个电路板似乎提供了大致相同的速度和质量,但利用原始FPGA性能以及可靠的硬件电路板。例如,甚至必须监测和控制设备温度,以保持可靠性并在电路板允许的范围内实现可能的最高性能。

信号复用的支持

时分复用(TDM)的概念及其在FPGA之间增加有效IO的能力是很好理解的,不难看出两个或多个信号如何在FPGA引脚之间共享相同的互连路径。TDM方法需要FPGA内部的多路复用器和解多路复用器逻辑,并且需要一种保持两端同步的方法。还需要以比FPGA内部逻辑更高的速率运行TDM路径,并确保到达多路复用器或离开多路复用器的信号都满足必要的时序约束。这将是一项手动执行的复杂任务,因此会开发EDA工具,可以自动插入TDM逻辑,分析时序,甚至选择用哪些信号填充多路复用器。

无论使用哪种工具,问题仍然存在,即使用多路复用,基于FPGA的原型必须以较低的速度运行,或者板载路径必须能够以较高的速度运行。TDM比为8:1或更高的情况并不罕见,在这种情况下,FPGA内部以16MHz运行的设计必须缩小到2MHz,或者外部信号必须以128MHz或更高频率在FPGA之间传播,或者在这两个极端之间进行某种妥协。由于某些基于FPGA的原型需要高复用率,TDM路径的运行速度可能会限制总体性能。因此,板之间的良好区别在于它们能够以高速和良好的可靠性运行外部信号;有噪声的板将可能在TDM流中引入毛刺,并扰乱其两端之间的同步。

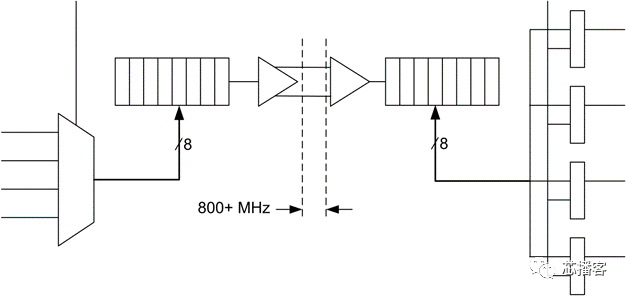

除了简单的TDM之外,还可以使用现代FPGA引脚的LVDS(低压差分信号)功能,以便以高达1GHz的速度运行板载路径。这种全速要求FPGA之间具有非常好的板级传播特性。下图给出了一个串行TDM配置的非详细示例,该配置允许八个信号通过一对差分信号进行传输。

在800MHz的高传输速度和8:1的复用率下,前面说的128MHz速度可以很容易地得到支持,甚至可以提高到64:1的比率,只要电路板足够好。运行高得多的多路复用器比率的可能性大大提高了FPGA之间的可用连接性。例如,TDM比为64:2(2而不是1,因为需要差分管脚)可以在运行于30MHz或更高的速率。

因此,FPGA板之间的一个很好的区别是,它们能够支持高质量的LVDS信号以实现更高的整体性能,并为FPGA提供必要的电压和IO电源以支持LVDS。同样重要的是,设计者以及他们用于划分的工具必须了解哪些板迹线的长度将匹配,并且能够承载高质量的差分信号。一个好的电路板将提供尽可能多的此类对,并将提供工具或实用程序支持,以将这些对分配给最合适的信号。

-

FPGA

+关注

关注

1664文章

22508浏览量

639431 -

lvds

+关注

关注

2文章

1244浏览量

70250 -

TDM

+关注

关注

0文章

59浏览量

16305

原文标题:【芯知识】FPGA原型平台速度的影响因素

文章出处:【微信号:于博士Jacky,微信公众号:于博士Jacky】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

什么是FPGA原型验证?如何用FPGA对ASIC进行原型验证?

FPGA原型平台速度的影响因素

FPGA原型平台速度的影响因素

评论