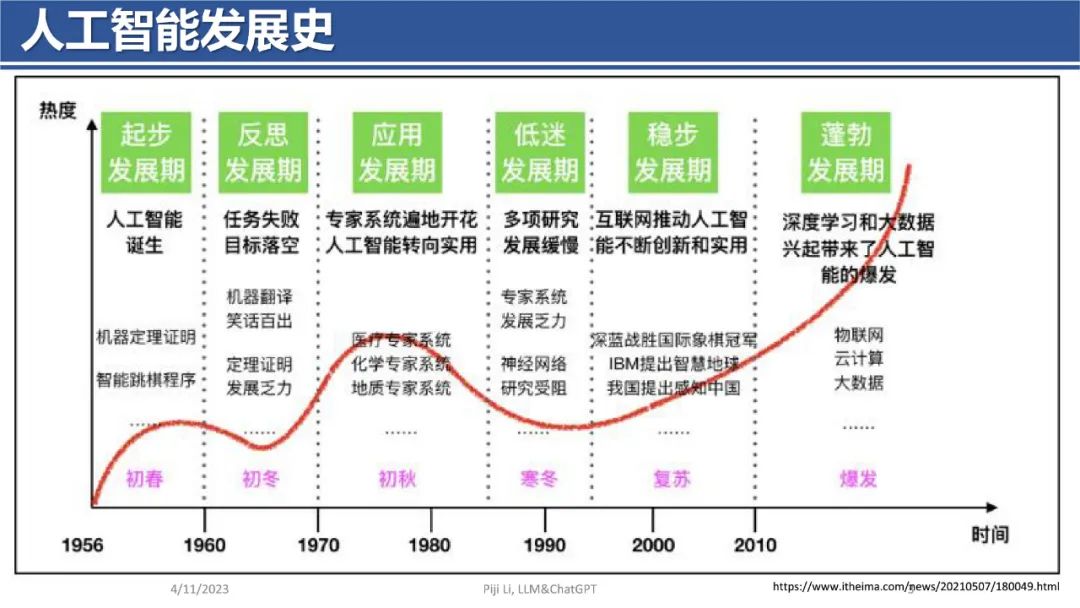

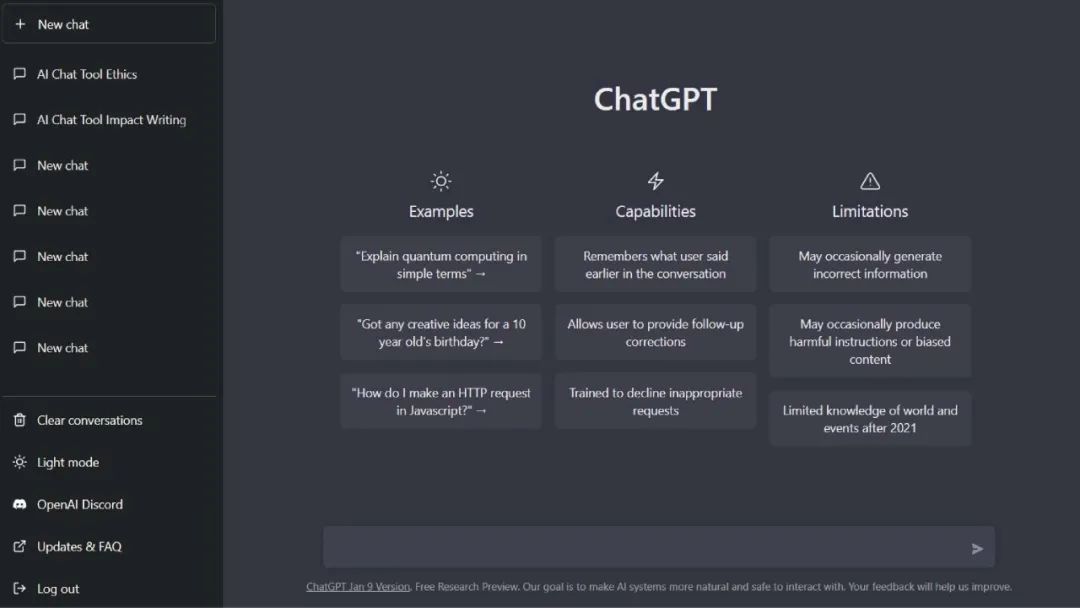

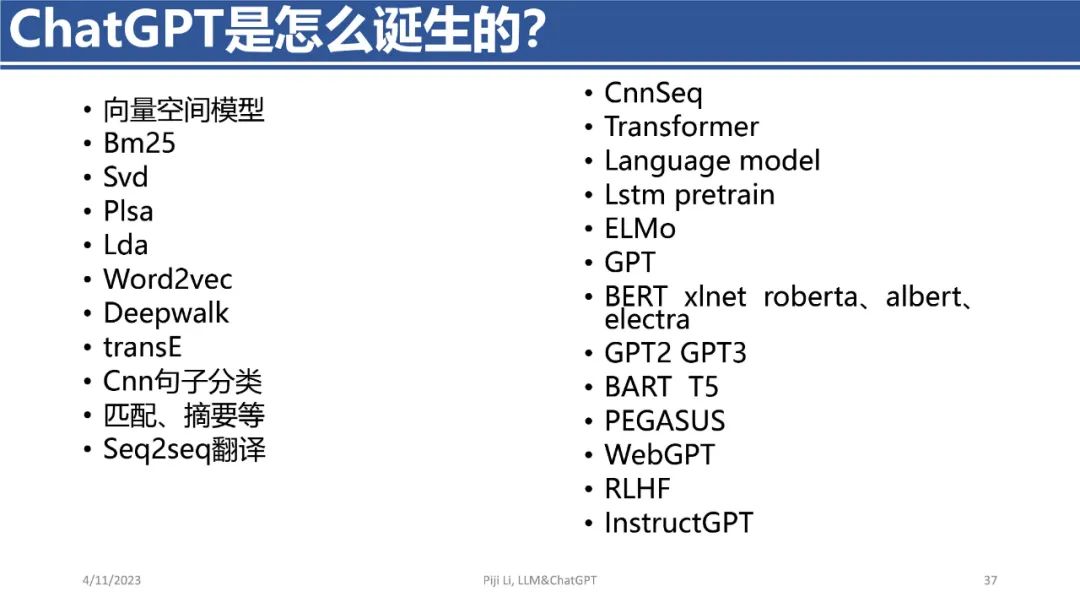

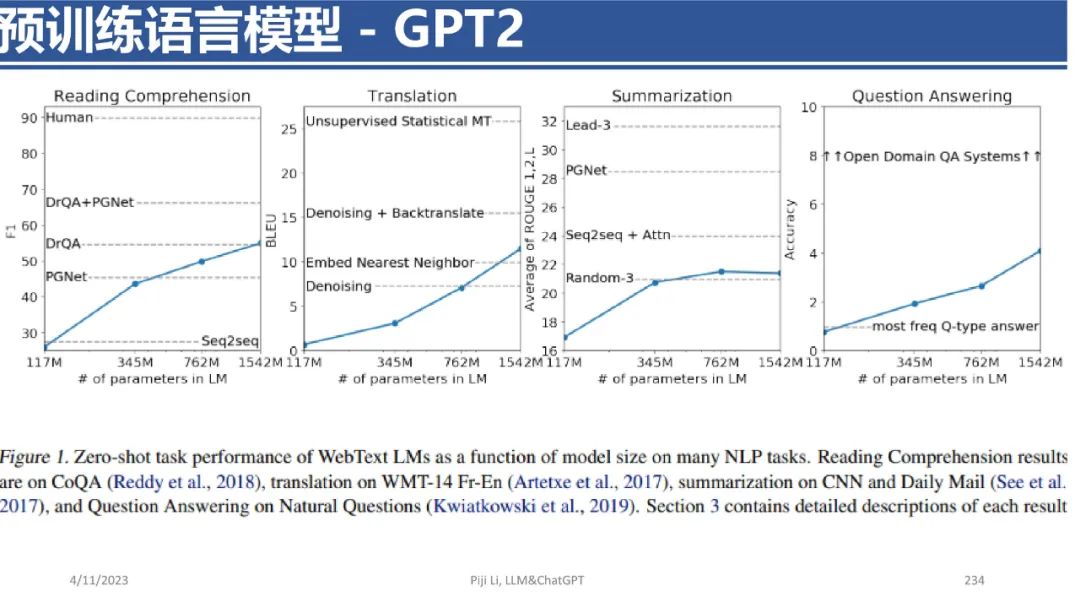

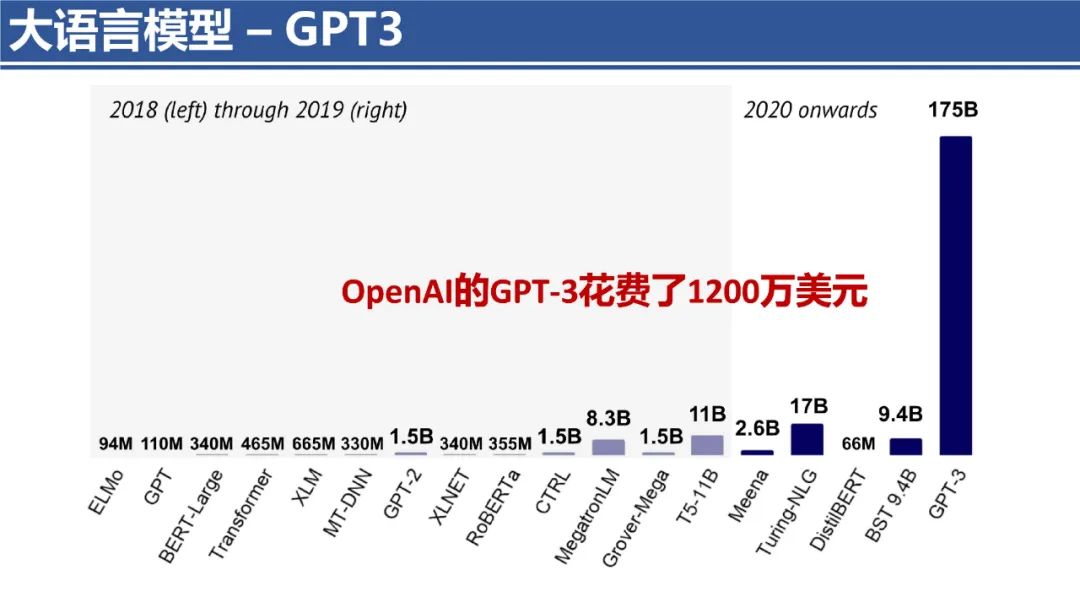

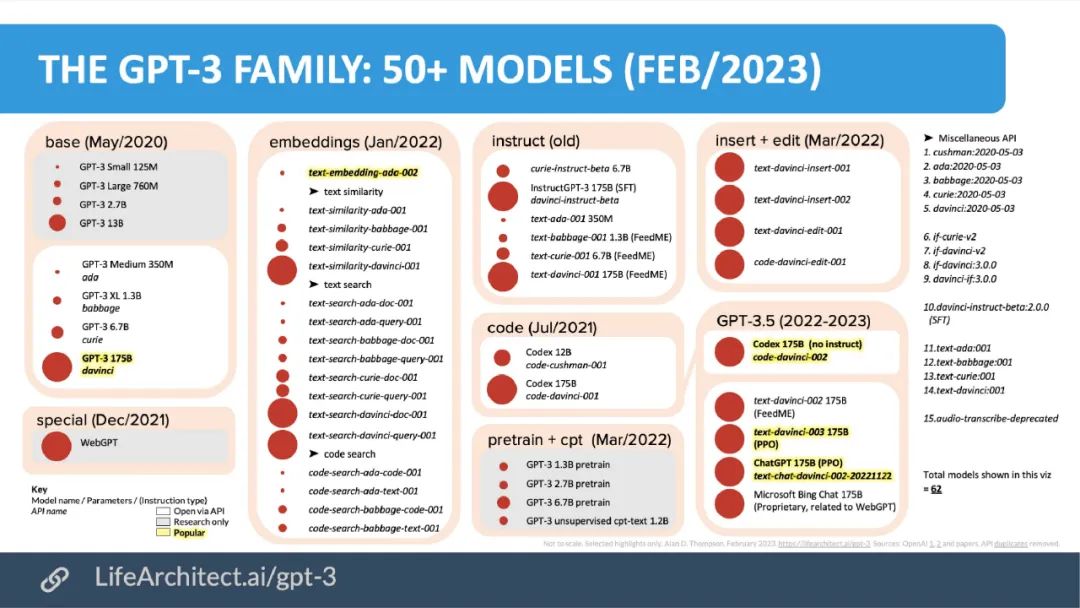

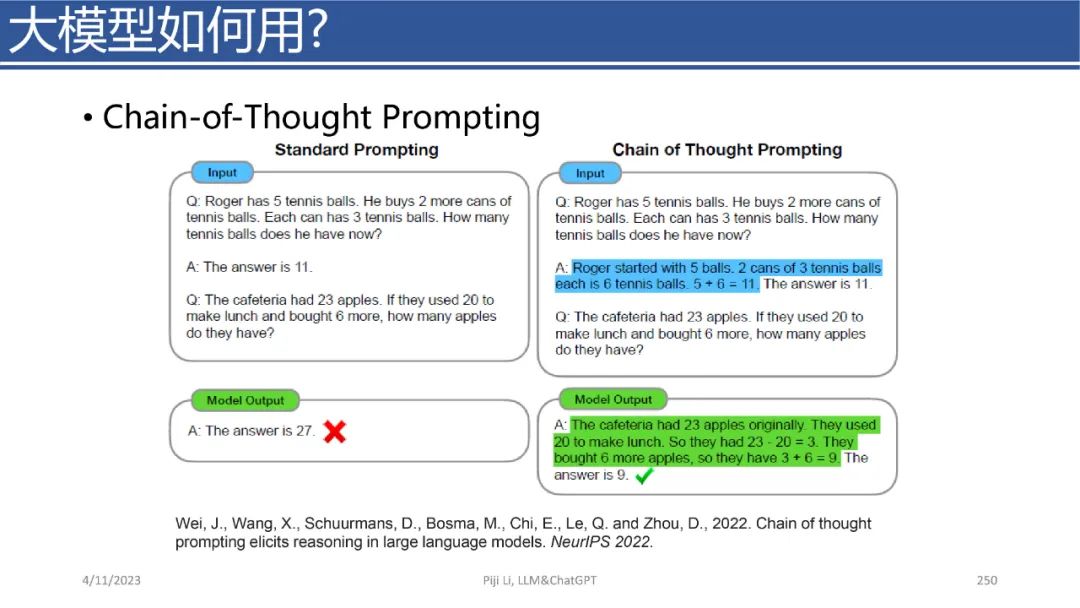

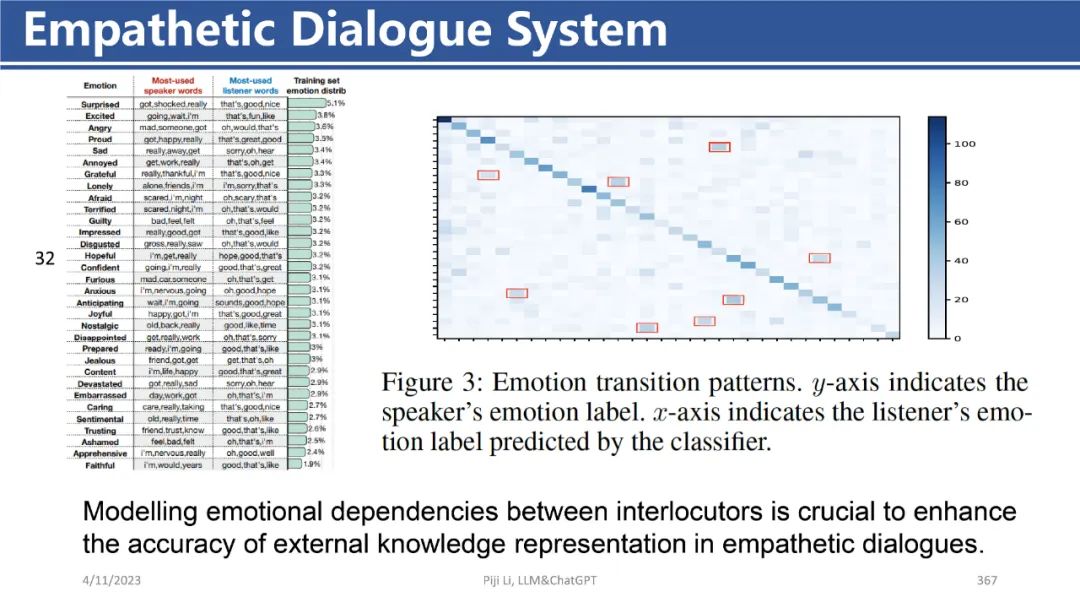

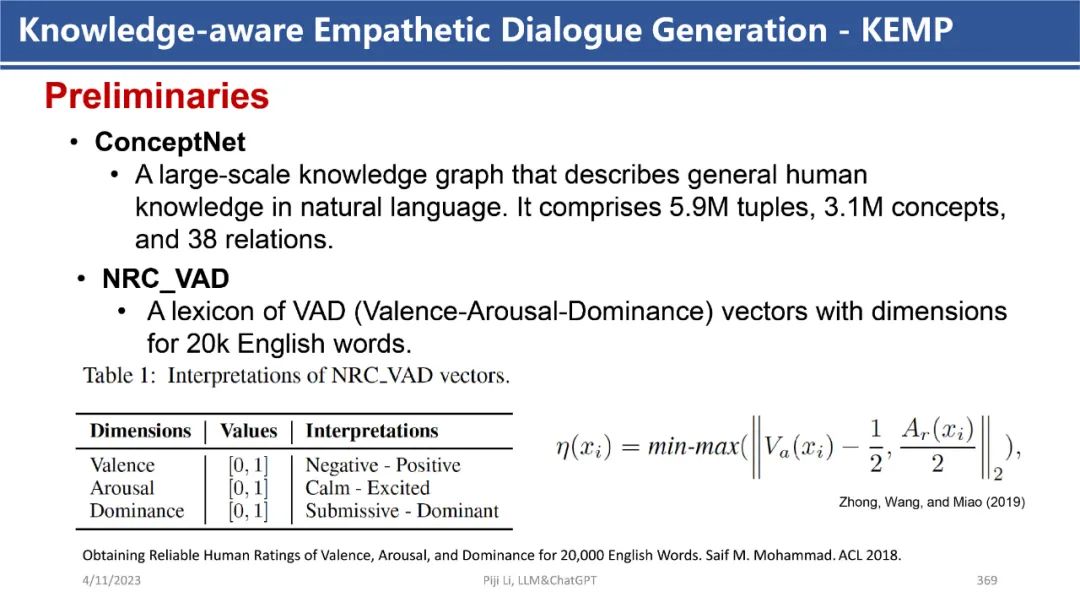

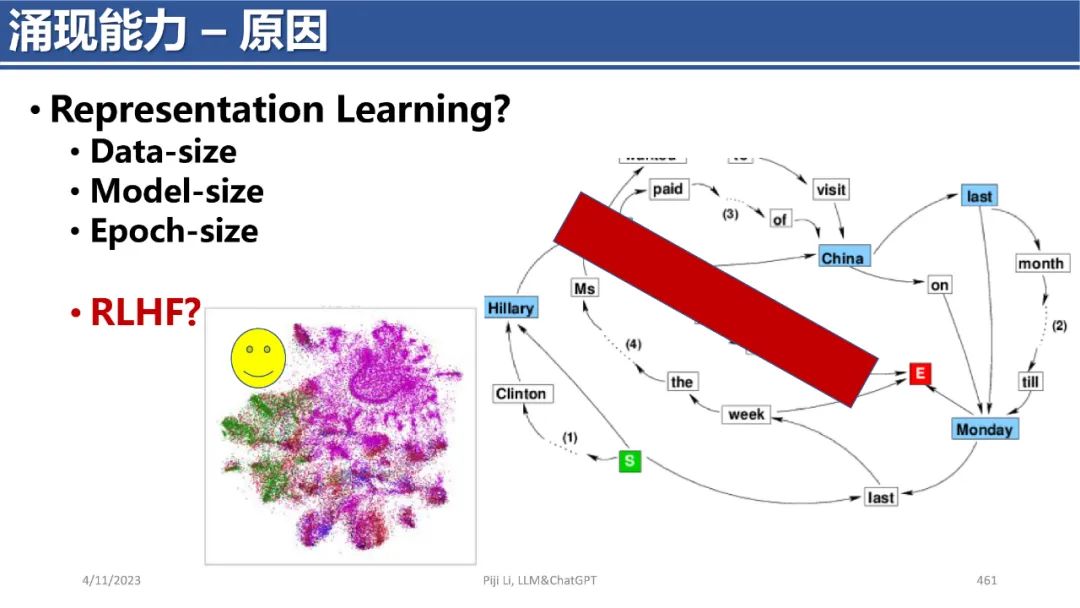

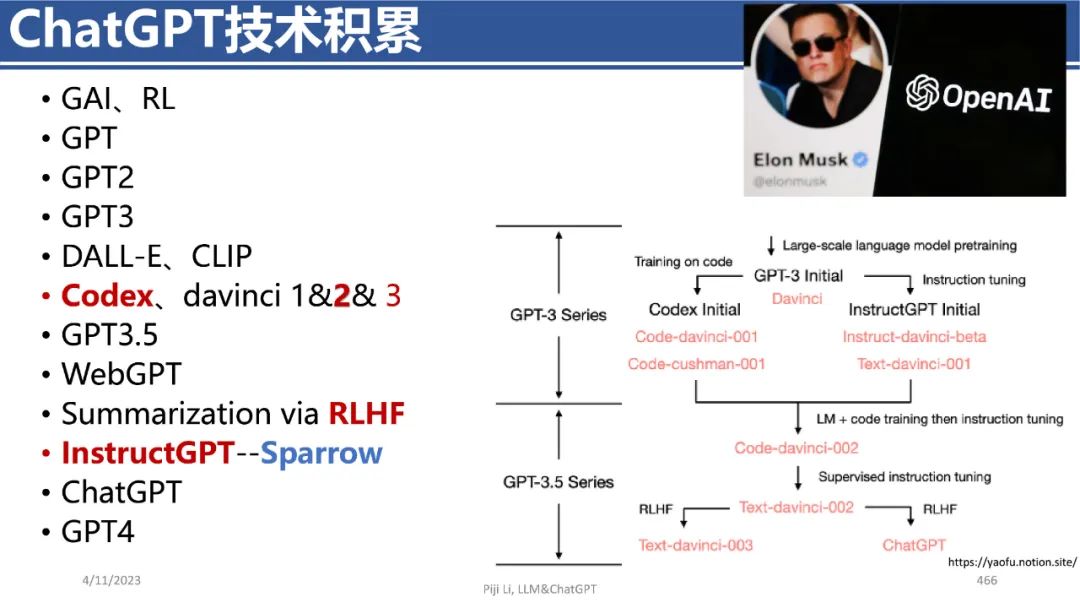

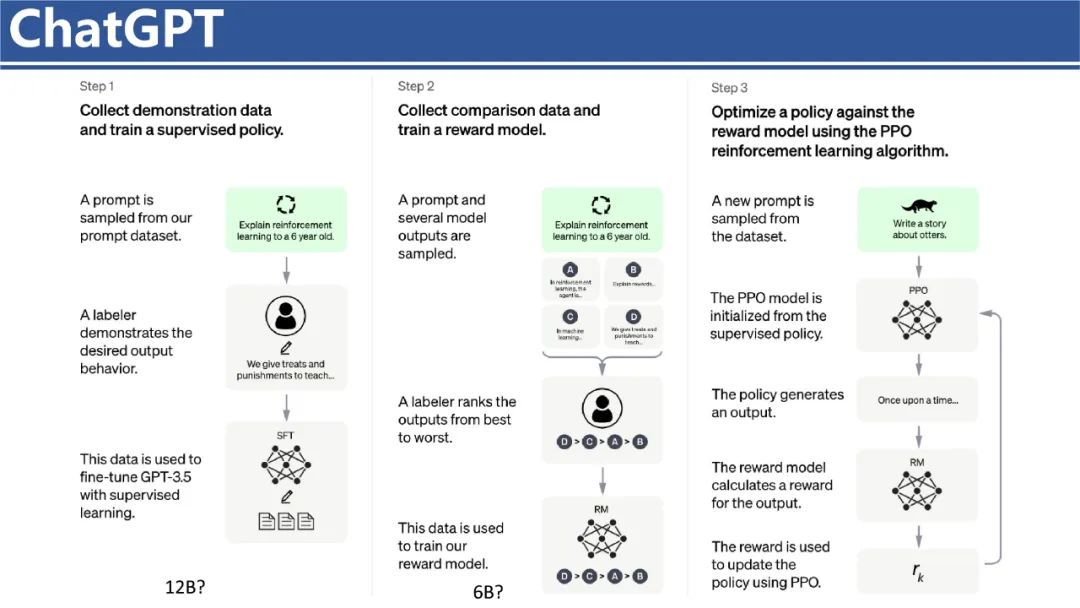

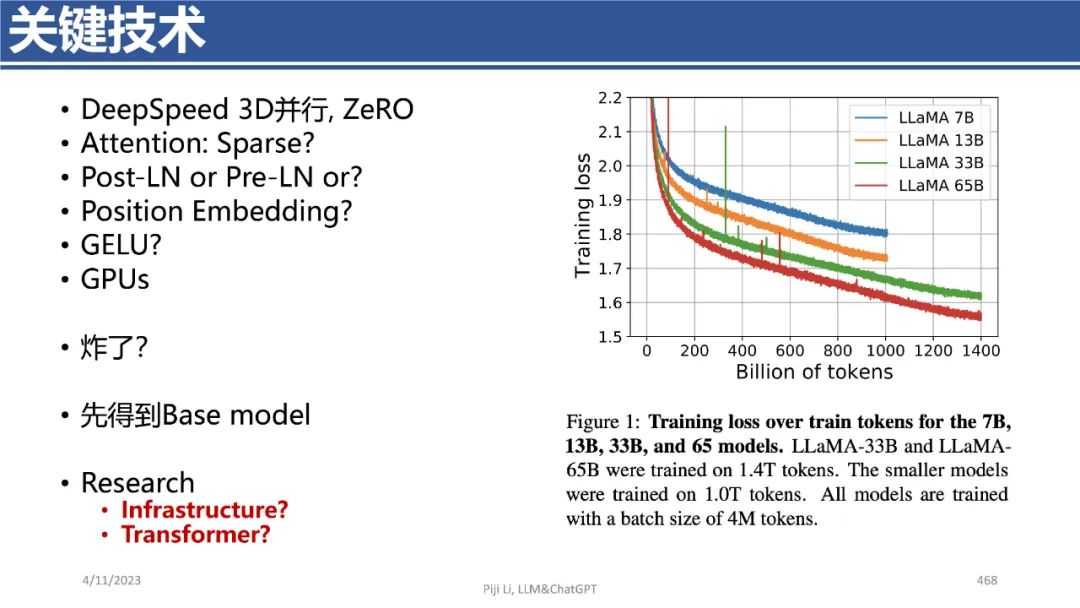

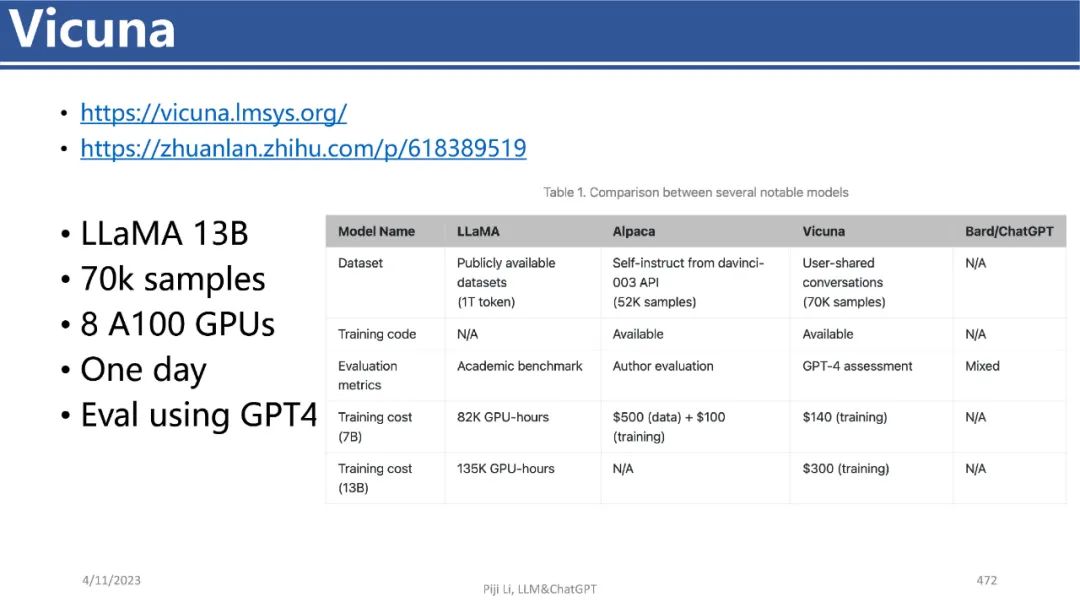

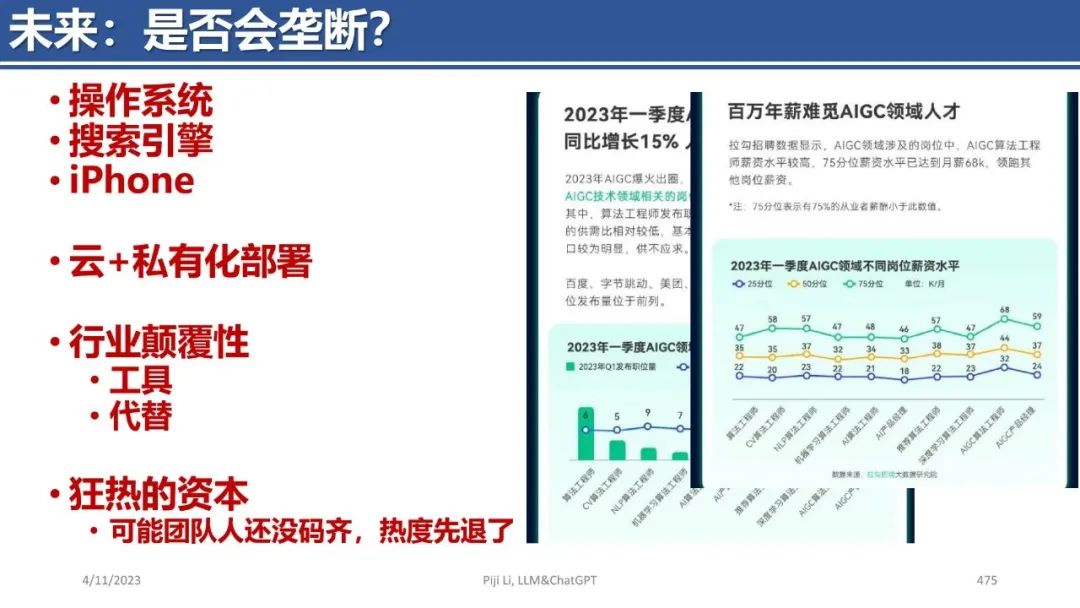

今天分享南京航空航天大学——李丕绩教授做的464页PPT《ChatGPT的前世今生》。从人工智能发展史,AI十年回顾,自然语言处理,ChatGPT诞生,模型分析,大模型应用,ChatGPT 可以做什么,以及未来发展等等干货内容,都在PPT中做了系统介绍。如果需要对ChatGPT补课,是很好的一份材料。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

AI

+关注

关注

91文章

41101浏览量

302579 -

ChatGPT

+关注

关注

31文章

1600浏览量

10392

原文标题:464页PPT!南航李丕绩教授的《ChatGPT的前世今生》

文章出处:【微信号:Imgtec,微信公众号:Imagination Tech】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

OpenAI正式发布ChatGPT Images 2.0版本

在人工智能技术迅猛发展的浪潮中,OpenAI始终是引领行业变革的先锋力量。近日,OpenAI正式发布ChatGPT Images 2.0版本,这一消息如同一颗重磅炸弹,在科技圈引发了强烈反响,在

数字隔离器的前世今生:从光耦替代到全场景赋能的演进之路

。从早期光耦的局限,到CMOS工艺革新,再到多元技术路线成熟,它逐步替代传统方案,成为工业控制、新能源、汽车电子等领域核心器件,以下循着技术脉络解析其完整历程。

ChatGPT突然无法登录是什么情况?如何解决?

很多人在使用 ChatGPT 时,都会遇到一个很头疼的问题: 突然无法登录 / 登录失败 / 一直转圈 / 验证不通过 ,尤其是做运营、跨境电商和经常需要使用AI工具的编程人员,这种问题一旦出现,会

金航标李建辉:多维度解析金铜涨价

SlkorKinghelm作者简介姓名:李建辉职务:金航标电子仓储部主管籍贯:湖南奋斗愿景:不上长城非好汉,不破楼兰终不还,朝自己坚定的人生目标努力!简介金航标电子仓储部主管李建辉浅谈“金”“铜

百度正式发布并开源新一代文档解析模型PaddleOCR-VL-1.5

1 月 29 日,百度正式发布并开源新一代文档解析模型 PaddleOCR-VL-1.5。该模型以仅 0.9B 参数的轻量架构,在全球权威文档解析评测榜单 OmniDocBench V1.5 中取得

低温无压烧结银的前世今生:从发明到未来趋势

低温无压烧结银的前世今生:从发明到未来趋势 低温无压烧结银(Low-Temperature Pressureless Sintered Silver, LT-PSS)作为第三代半导体封装与高端电子

巨头竞逐AI医疗健康:OpenAI推出ChatGPT Health,蚂蚁阿福国内领跑

健康已成为AI技术的高频应用场景。OpenAI在其一篇博客文章中透露,通过分析匿名化的ChatGPT对话数据,发现全球每周有超过2.3亿人在ChatGPT上咨询健康相关问题,医疗健康的需求极为旺盛。

为什么偏偏是周二?一文了解微软“补丁星期二”的前世今生

某个寻常的周二。办公室的IT同事面色凝重,咖啡杯见底的速度异于往常,甚至对着闪烁的屏幕低声自语……如果你看到类似的场景,请别轻易打扰。他们很可能正在应对微软每月一次的“补丁星期二”(PatchTuesday)。对于普通人来说,这只是一次平平无奇的“正在进行更新,请不要关机”;但对于IT团队来说,这却是每隔30天就要面对的一次“大考”——全球计算机与网络设备的

芯片装甲的前世今生

一前言众所周知,晶圆的特性如同玻璃一样容易破碎,但为什么做成成品的IC又能通过高震动与跌落可靠性测试,并且能在高温环境下非常稳定运行?这其实是一个关键的半导体技术——封装的功劳。它像一道“防护城墙”,既要屏蔽灰尘、水汽、冲击,也要兼顾散热、电性能和成本。在如今人人都知道先进半导体工艺已经先进到2nm的今天,对于不起眼的封装技术,却鲜有人熟知。接下来,让我们从

源网荷储:从概念到实践的全面解析

能源生产、传输、消费、存储全链条的系统工程。本文将从概念内核、核心价值、实践场景到发展路径,带你全面读懂源网荷储的“前世今生”与现实意义。

智汇虹科 | 中山大学原副校长李善民教授一行莅临虹科考察指导

10月22日,中山大学原副校长、经管学部主任兼企业研究院理事长、博导李善民教授,教务部主任、高级金融研究院副院长、博导王彩萍教授,马克思主义学院助理教授王思霓一行莅临虹科,与虹科CEO

ChatGPT 智能体发布的观点解析及对科义相关系统的现实意义

7月18日凌晨,OpenAI 发布通用人工智能代理 ChatGPT 智能体。这一事件蕴含着多层面的深刻意义,同时也为科义巡检机器人和科义视频行为分析系统带来了诸多现实影响。 从技术层面来看,这标志着

《ChatGPT的前世今生》南航李丕绩教授的解析

《ChatGPT的前世今生》南航李丕绩教授的解析

评论