1.前言

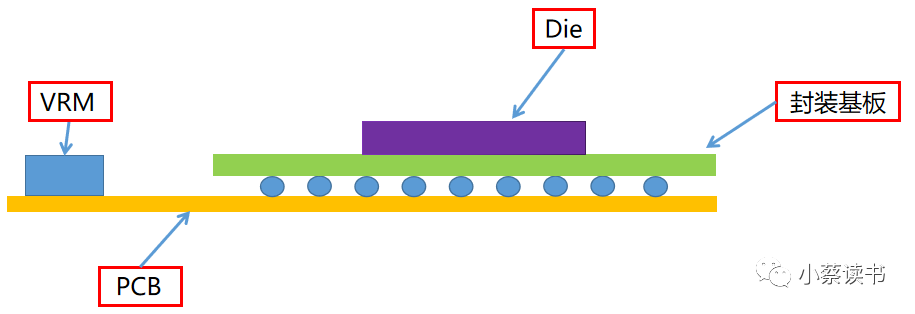

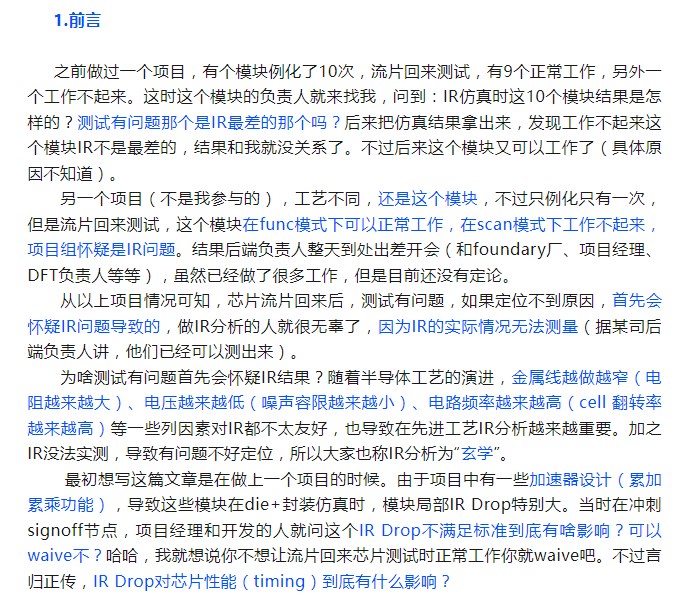

大部分从事后端设计的同行应该没有接触过带封装的IR Drop分析(模块级别的IR分析不需要考虑封装),一般只有PA工程师、后端项目经理、封装同事等才会接触这一部分内容。为啥要聊这一块呢?首先看下完整的供电路径(如下图):板级电源模块(VRM:Voltage Regulator Module)的电流经过PCB上的引线到达PCB的电源平面,通过Bump到达封装的管脚,再通过封装基板到芯片的PAD,再通过芯片内的电源网络到达晶体管电源的端口,地的回路和电源类似,电源和地的电流路径形成了完整的供电路径。

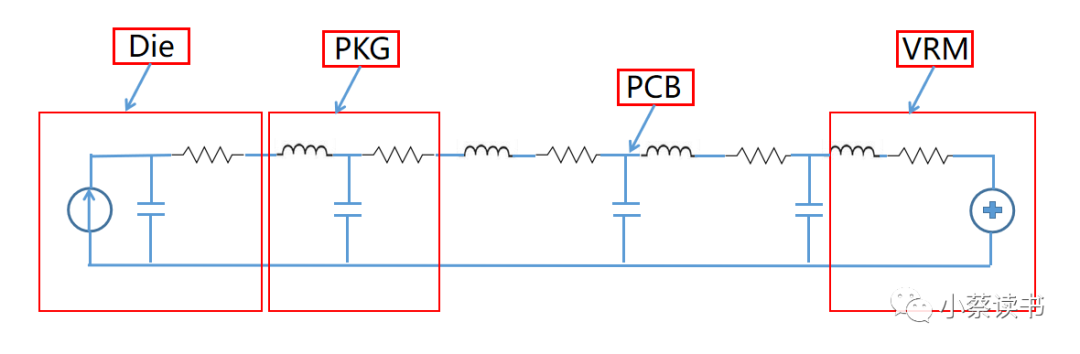

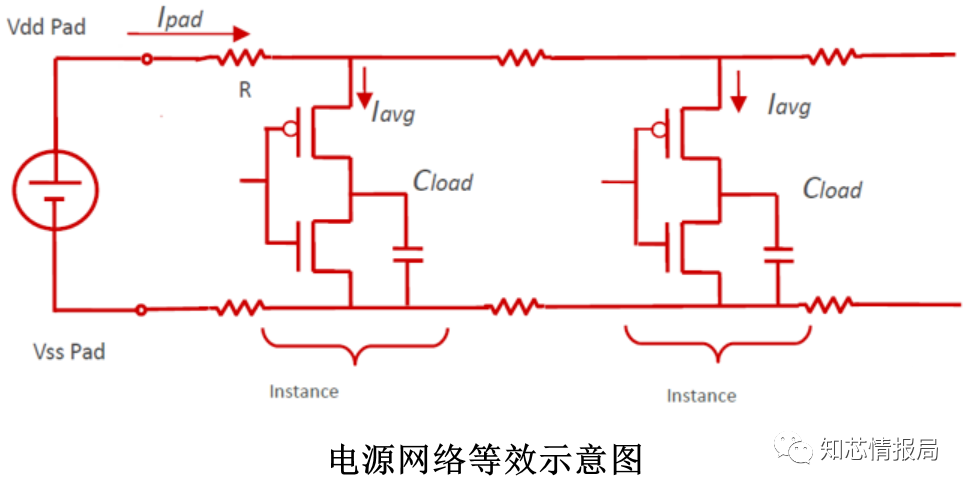

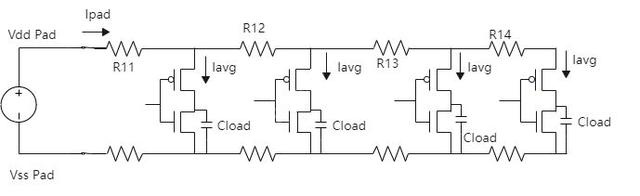

上图的供电路径等效电路图如下图所示,可见在VRM对晶体管供电的过程中,由于每一段供电路径都有等效的电阻、电感、电容,所以每一段也都有相应的电压降。

当整体考虑电源分布时,实际上涉及芯片上和芯片外的问题,这些问题从直流到直流转换器开始,包括PCB,电源分布(power plane),封装、插槽、电源管脚或焊接块等,最后是与门的连接。正确的电源网格设计需要系统设计工程师、热学设计师、系统架构设计师、电路板设计师和芯片设计者的共同工作。

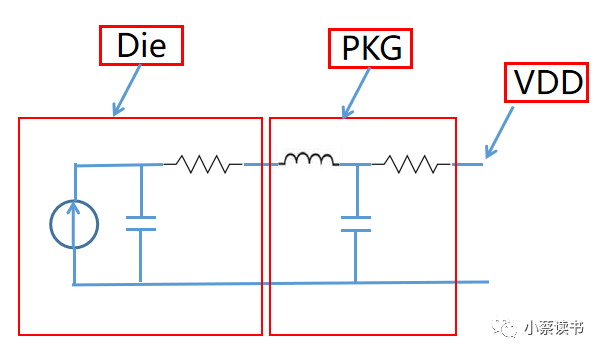

这个问题需要整体优化而不仅是局部的芯片级优化。 后端工程师只需要分析Die+PKG部分(但是应该记住这仅是整个设计问题的一部分),整体电源网络仿真分析应由封装或者系统的同事完成,因此本文讨论的范围限于Die+PKG部分,如下图:

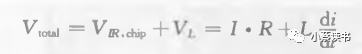

2.封装上的电压降

在纳米尺寸设计中,除了计算芯片的电压降外,还要考虑与封装相关的电压降。总电压降的大小Vtotal 由电源凸点到逻辑门单元之间等效电阻R及封装导线的电感值L决定,并由欧姆定律决定Vir,chip = I*R,I为通路电流,Vl = L*di/dt,则Vtotal值如下所示。

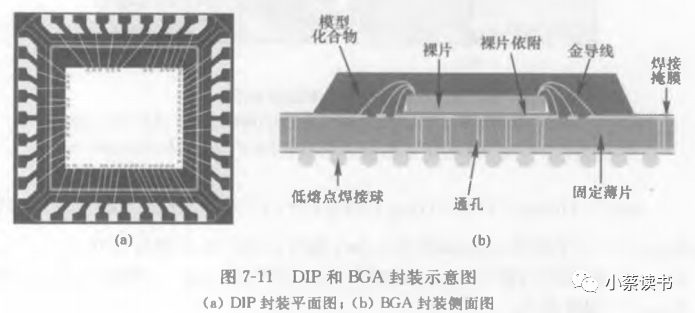

封装电感对电压降的影响,如下图所示的两种封装形式,其中图(a)为DIP(dual in-line)封装,图(b)为BGA(ball grid array)封装,前者的封装电感为1-2nH,而后者的封装电感为0.1-0.2nH.

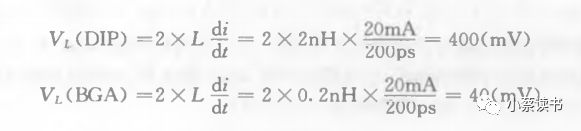

假设20mA的电流在200ps内通过电源网络给内部节点供电时,其消耗在DIP和BGA封装导线上的电压降和地弹的总值(作用于两条线路)分别计算得400mV和40mV:

由此可见,随着工艺的发展,core供电电压在下降,从0.9V(65nm) 0.8V(16nm)0.75V(7nm),封装导线所产生的电压降变得尤其突出,需要通过封装形式的改进减小电压降的值。在数模混合芯片中尤其要注意,数字core逻辑部分不管是die内电源走线还是PKG上的走线,都要保证足够强壮,不能认为数字逻辑部分instance比较少只要连起来就可以了。

3. CPA(Chip Package Analysis)

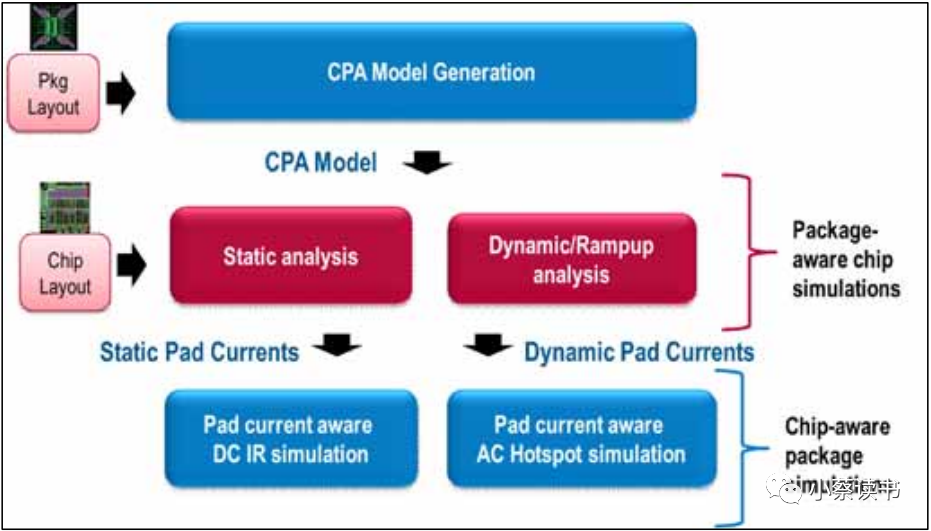

如下图所示,CPA model是Pkg Layout(封装基板设计)通过工具提取出来的一个模型,主要包括封装基板中的RLC参数。CPA可以提供每个bump的寄生参数,可以用来做chip+package的协同仿真。

chip+package可以做static分析,仿真可以得到每个pad的电流,可以为pad的过流能力是否超标做参考,这种方式属于直流仿真;当做dynamic仿真时,属于交流仿真。

4.问题

1.在抽取CPA model时,根据pin group不同,可以分为Lumped Grouping/Group by Each Pin/Group by X-Y Grid三种方式,这三种方式IR结果相差比较大,每个公司根据自己的经验选取方式不统一。Lumped Grouping所有pin一起抽,IR最小;GroupbyEachPin每个pin单独抽,IR最大,但是工具计算量大,run time长;Group by X-Y Grid 介于两者之间。

2.带CPA和不带CPA仿真,结果相差大吗?Static IR相差不大,Dynamic IR相差较大(尤其翻转率高的地方),为啥呢?自己思考下.

3.封装上的走线不均匀,连接弱的地方IR会比较大。另外GUI界面可以看到每个bump的电阻和电感。

审核编辑:刘清

-

PCB板

+关注

关注

27文章

1453浏览量

52186 -

直流转换器

+关注

关注

0文章

256浏览量

21251 -

PAD

+关注

关注

1文章

101浏览量

30808 -

晶体管

+关注

关注

77文章

9822浏览量

139267 -

VRM

+关注

关注

0文章

31浏览量

12747

原文标题:IR Drop与封装

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IR推出IR3588 ChiL数字控制IC及IR3552、IR3546

谈谈芯片设计中的IR-drop

什么是DC IR Drop?DC IR Drop仿真有何意义?

mos管漏极出现drop现象

什么是ADM (Add/Drop Multiplexer)

IR推出采用PQFN封装技术的MOSFET硅器件

IR推出新款PQFN封装功率MOSFET PQFN2x2

IR Drop对芯片性能及功能的影响

Sigrity PowerDC是如何计算IR Drop Margin?

IR Drop对芯片性能及功能的影响

IR Drop与封装(二)

IR Drop与封装分析

IR Drop与封装分析

评论