当采用buffer 驱动容性负载或者整个回路中存在较多的RC 延时环节,当输入信号为瞬变信号,容易导致输出震荡。接下来我们了解输出震荡的原因以及防止震荡的方法。

一、为什么输出会震荡?

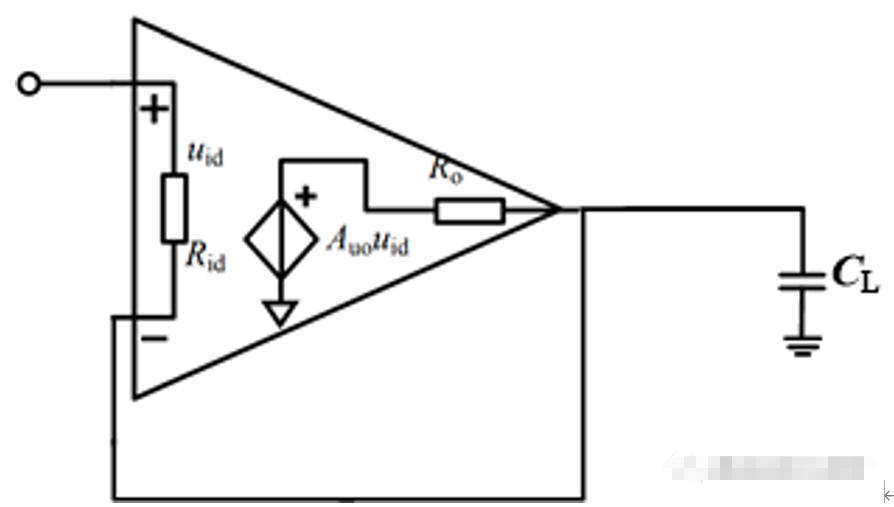

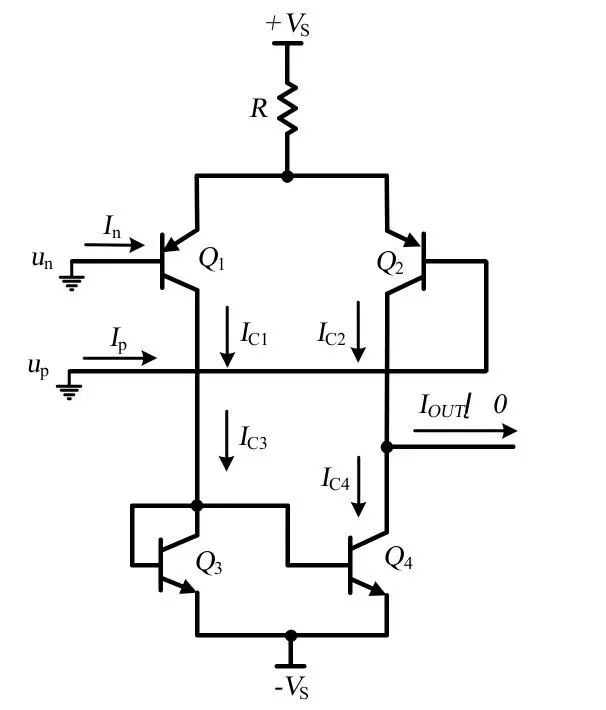

实际运算放大器芯片的输出端会存在输出阻抗,如下图中Ro,当运放带容性负载,如驱动线圈;驱动MOS管等。运放芯片内部Ro会与输出电容CL形成极点:fp =1/2pi*CL*Ro极点造成系统相位裕度下降 (当相位裕度为20°时,输出的超调量高达55%)从而造成输出震荡。

时域上当CL较大(nF~uF级别)时,时域上运放输出到反馈之间由RoCL造成的延迟过大导致输出震荡。(只有输入信号为瞬变信号时才会由于其包含的高频分量信号无法及时被反馈而震荡)

二、防震方法 1 ——输出加电阻:

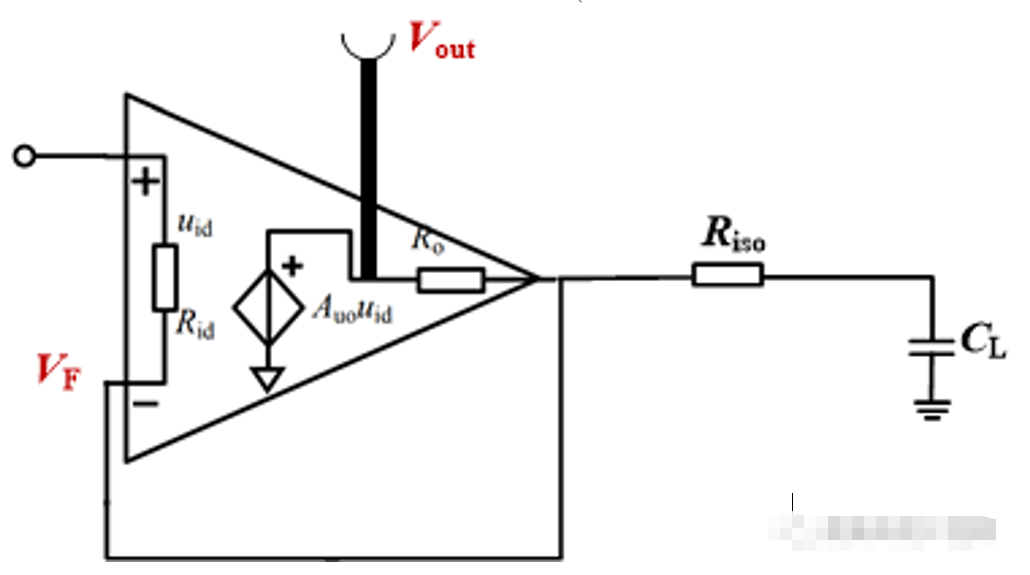

在输出加电阻是借由Riso引入新的零极点fz1、发fp1,当Riso>>Ro时,fp1 ≈ fz1 零极点近似相互抵消,达到补偿系统相位裕度的目的。

fz1 =1/2pi*CL*Riso,fp1=1/2pi* CL* ( Ro +Riso)

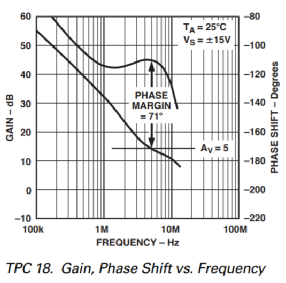

fz1零点补偿在穿越频率10倍频,开环增益等于20dB处(可从datasheet的幅值相位曲线中得到对应频率),即可得到 。

此办法虽然解决了稳定性的问题,但会在Riso上产生压降,使输出直流精度下降。不在意精度的时候可以采用此办法。

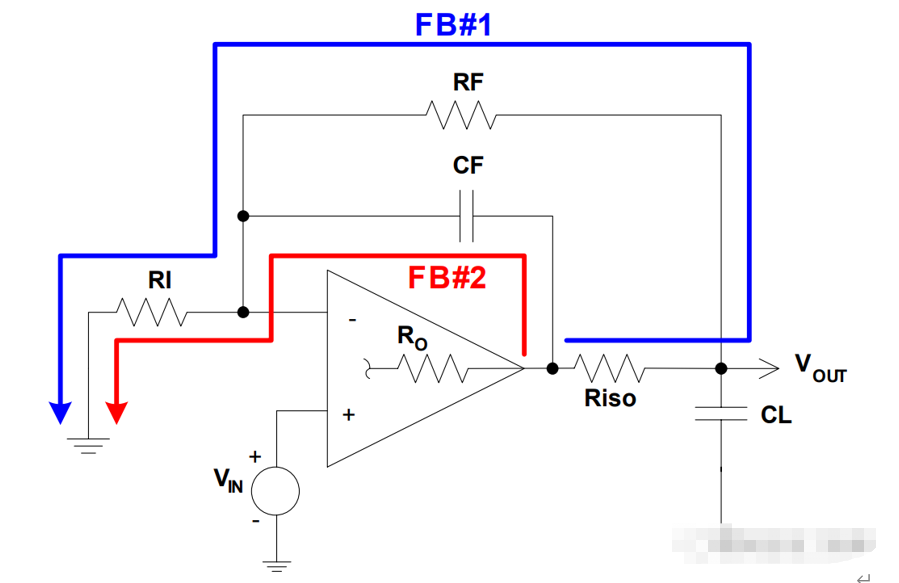

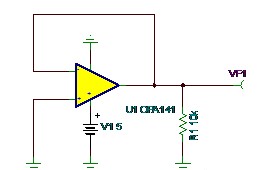

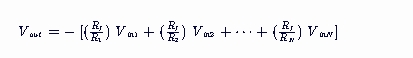

三、解决直流精度问题的防震方法2 ——双反馈回路

从上图看到在原有方法1 的基础上新增加CF,RF,从输出到反馈端引入了两条路径。RF 把信号的低频分量(CF: Open,RF: Closes the feedback around Riso)由正向输入端跟随到输出端; CF则把回路通过的高频分量(CF: Short, RF is effectively open)经Riso引入整个回路,实现相位补偿的目的。

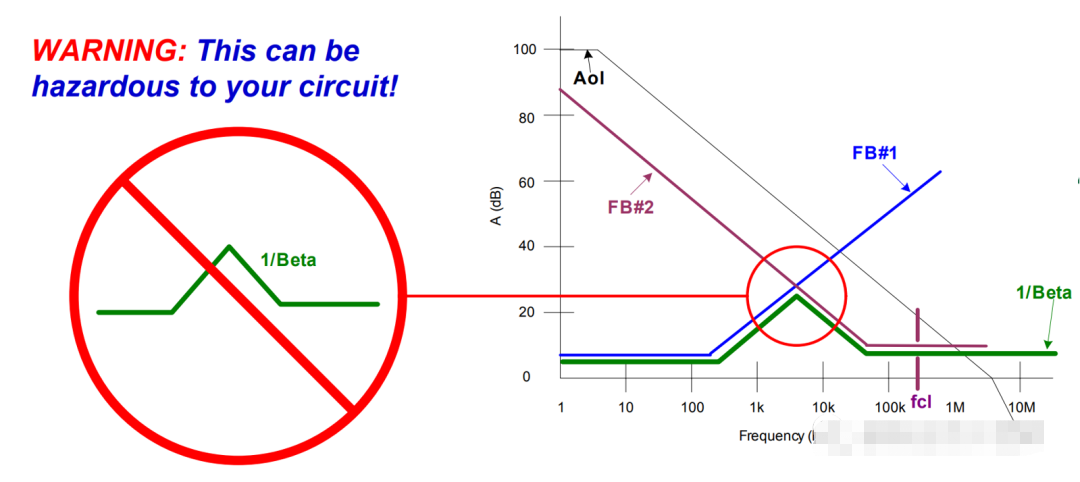

上图为两个反馈路径以及两者叠加的幅值裕度随频率变化曲线。当围绕一个运放使用双反馈路径时,两个反馈路径交叠处叠加出来的反馈效果会使1/β 斜率从+20db/decade 突然 变成了-20dB/decade。这意味着1/β曲线存在一个复共轭极点,这样相应地在环路增益曲线上即有 一个复共轭零点。复零点与极点在其对应的频率上引起一个 +/-90 度的相移。此外,复零点/复极点的相位斜率, 在其出现频率位置附近的一个狭窄频带内可从+/-90 度变化至+/-180 度。复零点/复极点的产生在闭环运放响应中可能会引起严重的增益尖峰,这是很不希望看到的情况,尤其在功率运放电路中。因此,对于CF的取值我们不希望太小,导致相位裕度变化频带过窄,同时也不能太大,使整体带宽变小。

对于的具体取值:

1. Riso>> Ro

2. RF ≥100×Riso

3.6*Riso*CL≤RF*CF≤18*Riso*CL ,CF在此范围内取值可保证两个路径相对稳定。

分享具体案例:

实验验证:以一颗常用运放器件(phase margin 75°)为例。

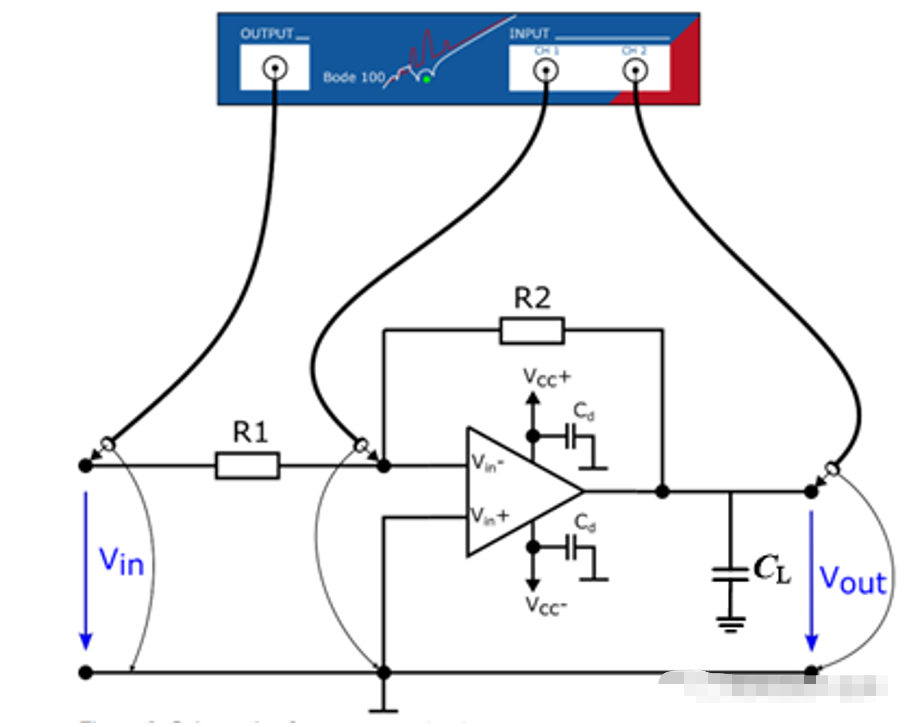

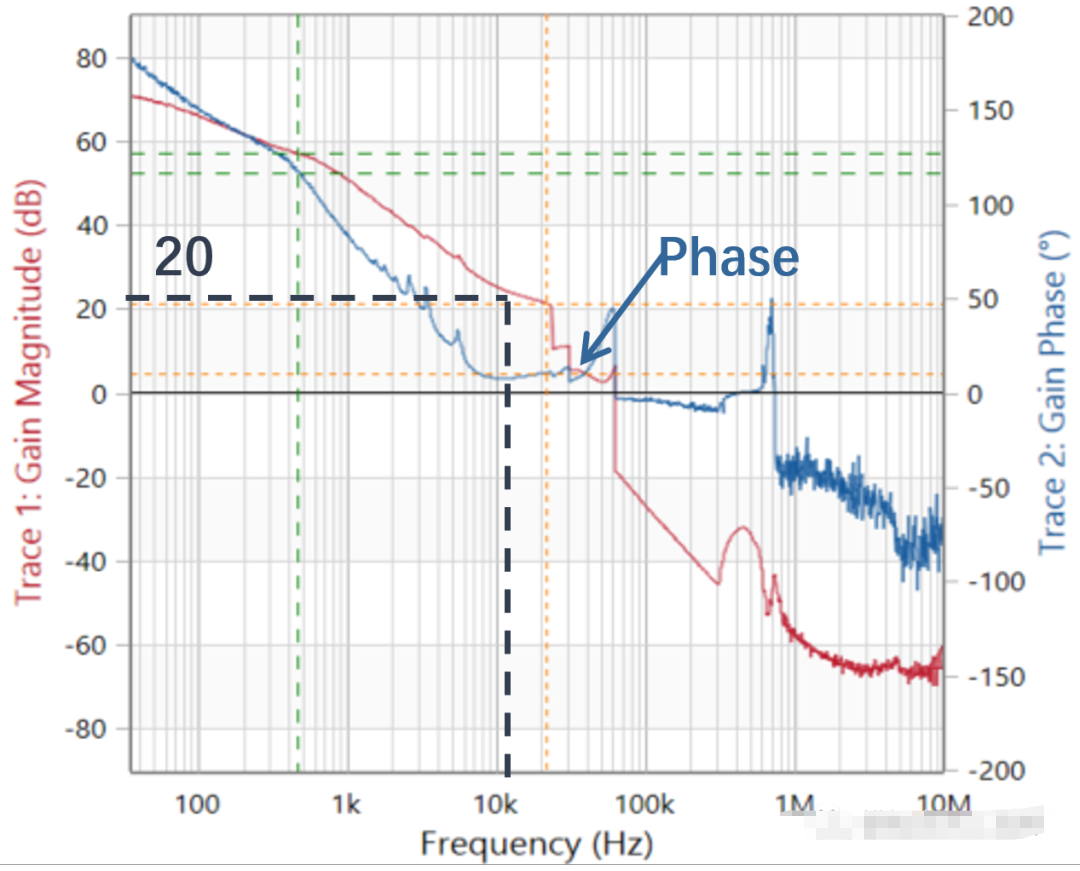

当其带容性负载为1uF时,通过Bode 100对以下电路进行扫频得到其开环特性的幅频和相频曲线。

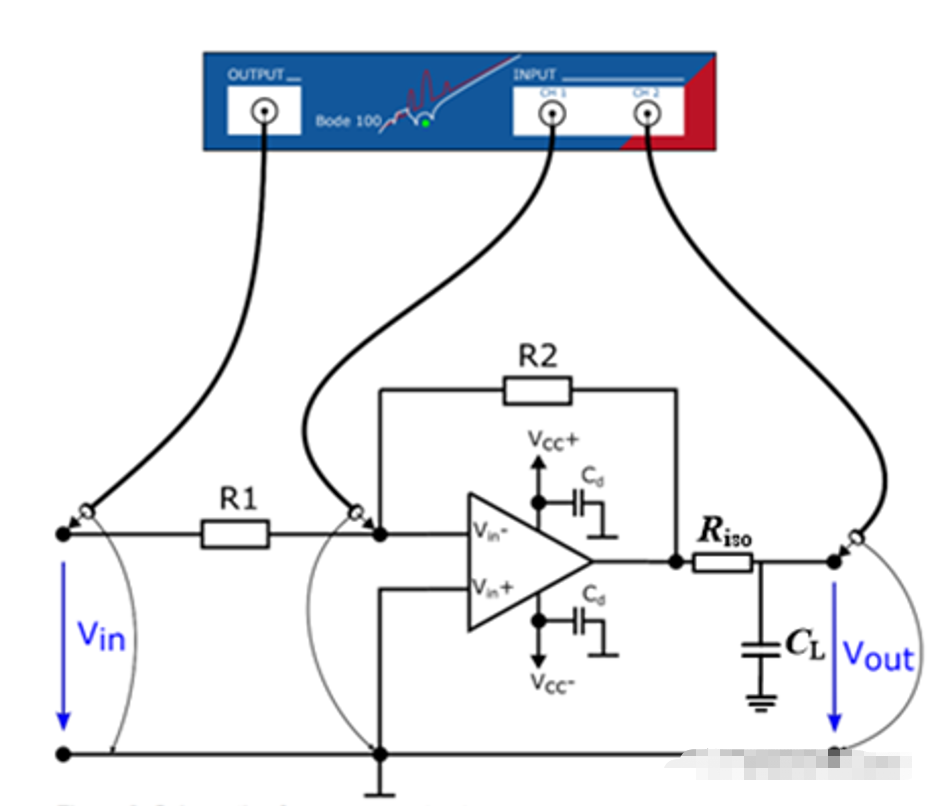

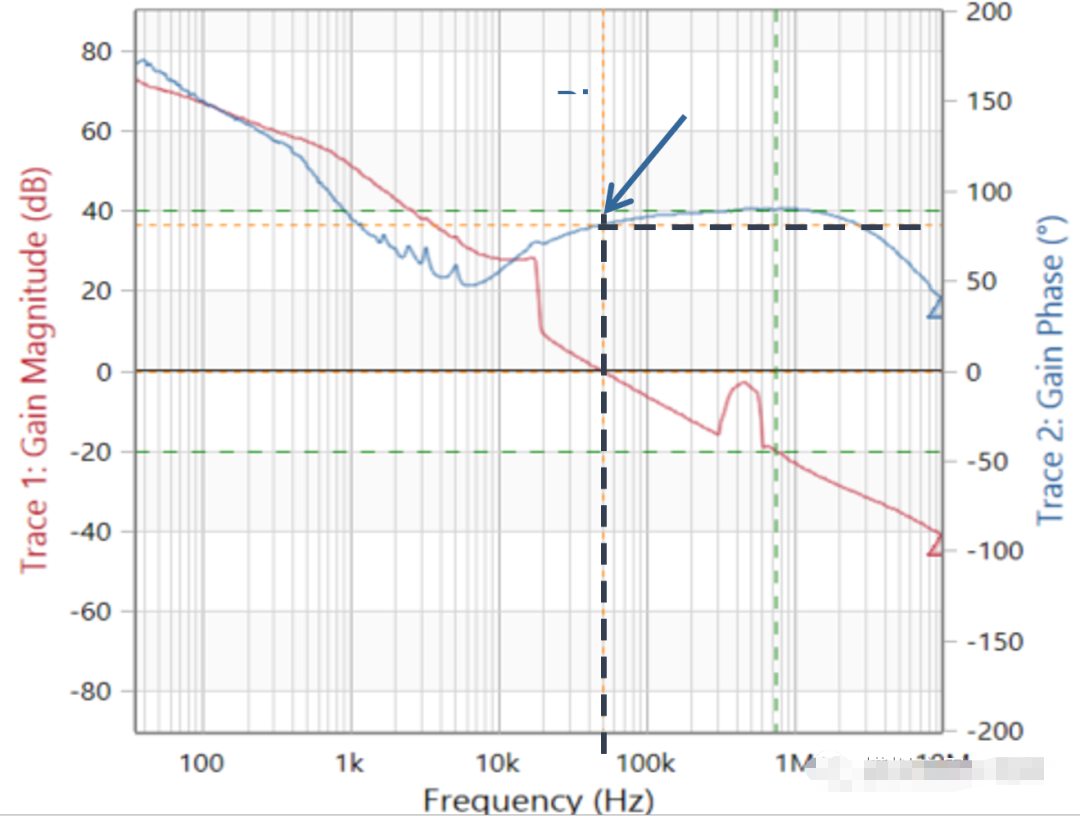

取Riso=18Ω进行相位补偿,再对增加Riso的电路进行扫频,得到的开环特性的幅频和相频曲线如下所示。

如上图,加入Riso后系统相位裕度变成81°,添加Rf=22kΩ,

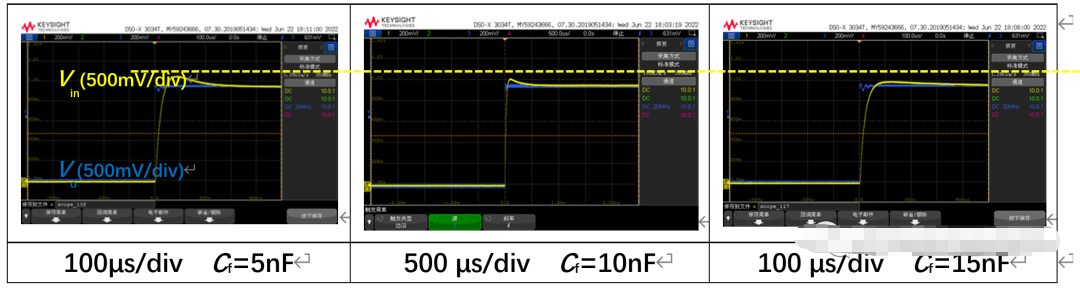

取Rf>1000Riso,Cf分别取5/10/15nF,输入1V阶跃信号(黄色),输出电压波形(蓝色)如下图所示,Cf越大阻尼越大, 超调量越小。实际Rf>100Riso即可,这样Cf更大系统响应速度更快,超调量会减小。

通过以上实验,我们知道当运放跟随电路带容性负载输出震荡时,可以通过添加Riso与双反馈回路进行相位与精度补偿,在用户端我们也推荐工程师预留Riso、Rf、Cf的位置。如若已经设计好电路来不及修改,也可尝试选用相位裕度较大的运放进行替代。

-

线圈

+关注

关注

14文章

1820浏览量

44432 -

运算放大器

+关注

关注

215文章

4931浏览量

172860 -

MOS管

+关注

关注

108文章

2411浏览量

66772 -

运放

+关注

关注

47文章

1163浏览量

53062 -

RC

+关注

关注

0文章

227浏览量

48801

发布评论请先 登录

相关推荐

运算放大器的自激震荡

什么是运算放大器

高精度运算放大器,高精度运算放大器是什么意思

运算放大器的应用及种类介绍

运算放大器的输出限制

运算放大器输出震荡的原因和防震方法

运算放大器输出震荡的原因和防震方法

评论