电子发烧友网报道(文/黄晶晶) SK海力士近日发布全球首次实现垂直堆叠12个单品DRAM芯片,成功开发出最高容量24GB的HBM3 DRAM新产品。

图源:SK海力士

目前已向数多全球客户公司提供了24GB HBM3 DRAM样品正在进行性能验证,预计从今年下半年起将其推向市场。而现有HBM3 DRAM的最大容量是垂直堆叠8个单品DRAM芯片的16GB。无论是堆叠数量还是容量上,此次发布的新品都有显著提升。

HBM(高带宽存储器)是高价值、高性能存储器,垂直互连多个DRAM芯片。目前SK海力士在HBM市场处于领先地位,约有60%-70%的份额。

图源:SK海力士

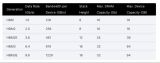

SK海力士于2013年首次开发HBM DRAM(第一代)产品,随后以HBM2(第二代)、HBM2E(第三代)、HBM3(第四代)的顺序开发。早在去年6月,SK海力士宣布其HBM3将与NVIDIA H100Tensor CoreGPU结合用于加速计算,SK hynix于2022年第三季度开始发货。今年年初随着ChatGPT的火爆,HBM订单激增。那么SK海力士有哪些技术来提升HBM的性能呢,以下结合SK海力士多位技术专家的分享进行一些解读。

训练计算需匹配高性能存储

训练GPT-3、Megatron-Turing NLG 530B等超大语言模型所要求的算力提升速度呈数倍到数百倍的增长。尤其是ChatGPT的训练,ChatGPT人工智能语言模型的背后就是Transformer架构。这个架构突破了传统的循环神经网络(RNN)和长短时记忆网络(LSTM)的局限性,能够在大规模数据集上进行高效训练。为了实现高效训练计算,就需要有与之匹配的高性能存储。

图源:SK海力士

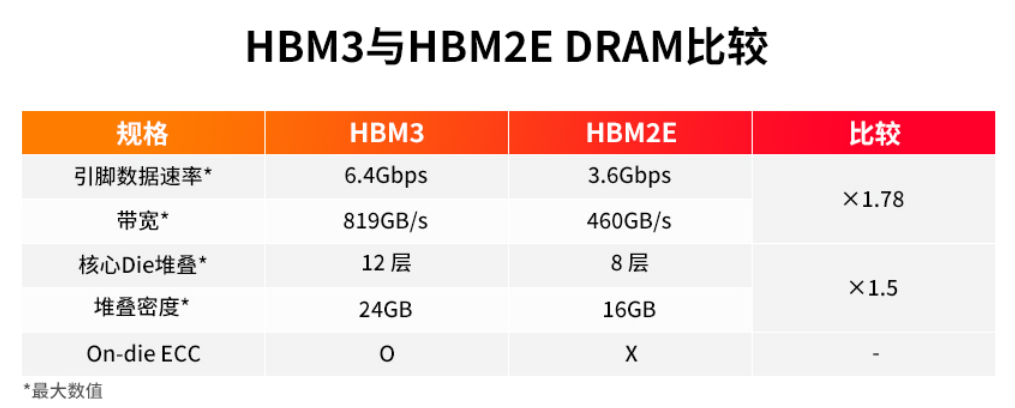

SK海力士于2021年10月推出全球首款HBM3,并在2022年6月实现量产。据介绍,该款HBM3每个引脚传输速率达6.4Gbps,1024位宽接口,最高带宽可达819GB/s,较HBM2E(460GB/s)高约78%。16Gb内核密度、尖端的TSV垂直堆叠技术,满足了系统对更高密度的要求,该技术可实现12层堆叠内存立方体,从而实现最大24GB封装密度。HBM3配备On-die ECC(纠错码)可靠性功能,可自我检测和纠正数据错误,从而在SoC和DRAM之间实时传输海量数据。

图源:SK海力士

先进的封装技术

此次新产品采用了先进(Advanced)MR-MUF和TSV技术。SK海力士表示,通过先进MR-MUF技术加强了工艺效率和产品性能的稳定性,又利用TSV技术将12个比现有芯片薄40%的单品DRAM芯片垂直堆叠,实现了与16GB产品相同的高度。这两项技术也是SK海力士先进封装技术的重要组成。

首先来看先进MR-MUF技术。根据SK海力士的官方资料,MR-MUF(Mass Reflow Molded Underfill, 批量回流模制底部填充)将半导体芯片贴附在电路上,并在堆叠芯片时使用“EMC (Epoxy Molding Compound, 液态环氧树脂模塑料”填充芯片之间或芯片与凸块之间间隙的工艺。这种新的工艺主要是比之前的NCF技术工艺有了很大提升。此前的NCF技术是在芯片之间使用薄膜进行堆叠。与NCF相比,MR-MUF导热率高出两倍左右,工艺速度和良率都有提升。

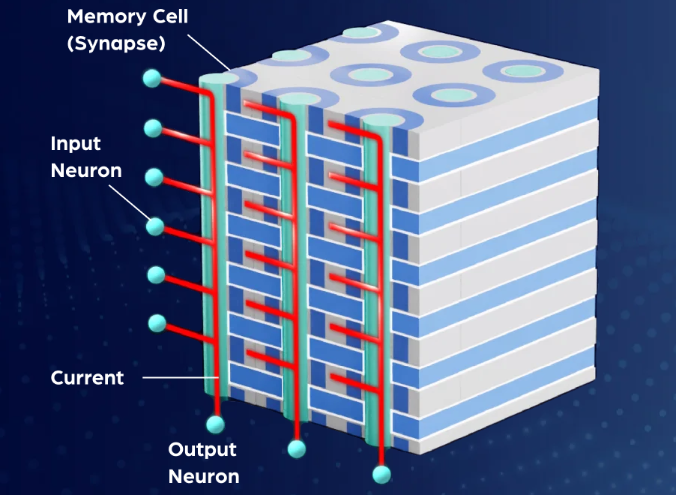

另一个是TSV(Through Silicon Via, 硅通孔技术)。TSV技术是在DRAM芯片打上数千个细微的孔,并通过垂直贯通的电极连接上下芯片的先进封装技术。这种技术已经成为一种提升DRAM性能和密度的重要手段,可以应用于3D-TSV DRAM和HBM。

图源:SK海力士

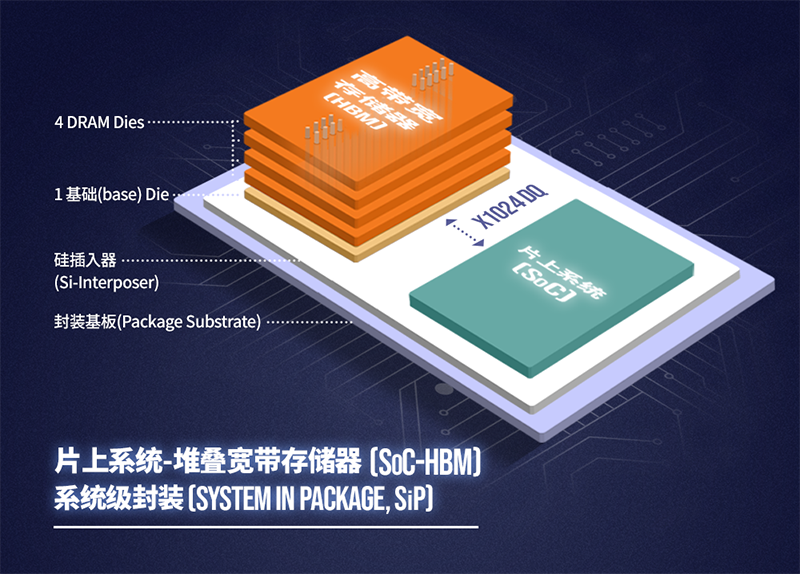

HBM主要用于弥补SoC高带宽需求与主存储器最大带宽供应能力之间的带宽缺口。SK海力士专家表示,特别是在AI应用中,每个SoC的带宽需求可能都会超过几TB/s,这是常规主存储器无法满足的。例如具有3200Mbps DDR4 DIMM的单个主存储器通道只能提供25.6GB/s的带宽。即使是具有8个存储器通道的CPU平台,其速度也只能达到204.8GB/s。而围绕单个SoC的4个HBM2堆叠可提供大于1TB/s的带宽。根据不同的应用程序,HBM既可以单独用作缓存,也可以用作两层存储中的第一层。

图源:SK海力士

实际上除了GPU搭载了HBM之外,CPU也实现了封装HBM。去年底,英特尔就正式推出了全球首款配备 HBM 内存的 x86 CPU——Intel Xeon Max 系列。根据下图介绍,它具有64 GB的HBM2e 内存,分为4个16 GB的集群,总内存带宽为1 TB / s,每个内核的HBM都超过1 GB。

图源:Intel

当前HBM的技术方向主要是在速度、密度、功耗、占板空间等方面的提升。SK海力士通过提高引脚数据速率、I/O总线位宽等方式提升速率;通过扩展Die堆叠层数和物理堆叠高度,以及增加核心Die密度以优化堆叠密度。通过评估内存结构和操作方案,最大限度地降低每带宽扩展的绝对功耗;为了实现总内存Die尺寸最小化,则是通过在不扩大现有物理尺寸的情况下增加存储单元数量和功能。

小结

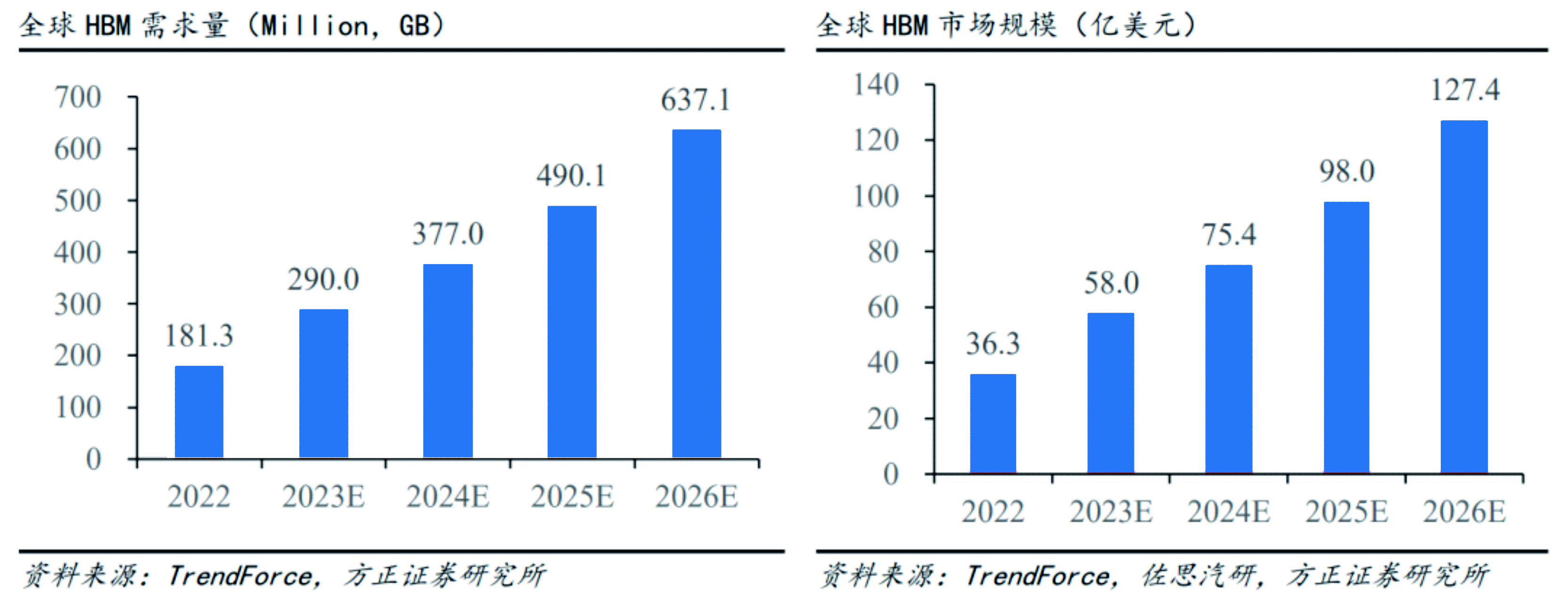

显然,人工智能、数据中心的应用还将拉动HBM的需求,但从成本来看,HBM的平均售价至少是DRAM的三倍,前不久受ChatGPT的拉动,HBM的价格更是水涨船高,消息人士称,与性能最高的DRAM相比HBM3的价格上涨了五倍。不过,这一市场前景也正是DRAM存储厂商投入技术和产品的动力。

-

块存储

+关注

关注

0文章

6浏览量

2310 -

HBM3

+关注

关注

0文章

74浏览量

154

发布评论请先 登录

相关推荐

HBM格局生变!传三星HBM3量产供货英伟达,国内厂商积极布局

DRAM存储器的基本单元

3D DRAM内嵌AI芯片,AI计算性能暴增

三星电子与SK海力士加大DRAM与HBM产能,应对AI热潮下的存储需求

中国AI芯片和HBM市场的未来

剑指HBM及AI芯片,普莱信重磅发布Loong系列TCB先进封装设备

HBM3E起飞,冲锋战鼓已然擂响

SK海力士成功量产超高性能AI存储器HBM3E

SK海力士HBM3E正式量产,巩固AI存储领域的领先地位

HBM、HBM2、HBM3和HBM3e技术对比

AI训练不可或缺的存储,HBM3 DRAM再升级

AI训练不可或缺的存储,HBM3 DRAM再升级

评论