高级电机控制应用简介

当今的电机控制应用需要具有有限结果的多轴、多功能解决方案。考虑大型自动化工业制造单元中的机器人(循环执行任务)甚至是机器人辅助医疗手术 - 这些机器人需要具有确定性输出的所有方向的精确控制。同样,高端工业无人机需要稳定的陀螺仪和更高的机械可靠性,以及DSP的高速计算能力。在更关键的情况下,例如心室辅助装置等医疗植入物(以帮助心脏泵血更好),除了精度和确定性之外,鲁棒性和可靠性也是必不可少的,因为不能容忍故障。电动机还执行关键功能,例如航天器中的姿态控制,部署机构,运动和节气门控制。机翼致动器在较低速度下保持飞机的燃油效率,通常在起飞后或准备着陆时。这些应用需要在高真空、辐射和各种操作环境下实现长使用寿命、高可靠性和安全性。

始终需要降低系统成本 - 拥有将数字外设与处理器内核集成的单个网络、多协议硬件。

FPGA 在电机控制设计中的优势

与ASIC相比,FPGA具有许多优势,最明显的是确定性、具有现场可重新配置性的并行计算。它们可以实现复杂的逻辑功能,支持多个系统实现和修订。

我们的FPGA的独特之处在于它们由基于闪存的非易失性存储器制成。这种即时启动技术使其功耗比竞争FPGA低30%至50%。它们提供抗辐射性和独特的安全功能,例如防止过度构建和克隆、设计 IP 保护、信任根、安全数据通信和防篡改功能。具体而言,在电机控制环境中,我们的FPGA通过提供低功耗、低抖动、低延迟、高精度、确定性和可扩展性,在解决现代电机控制应用面临的复杂挑战方面发挥着重要作用。

智能HLS提高生产力

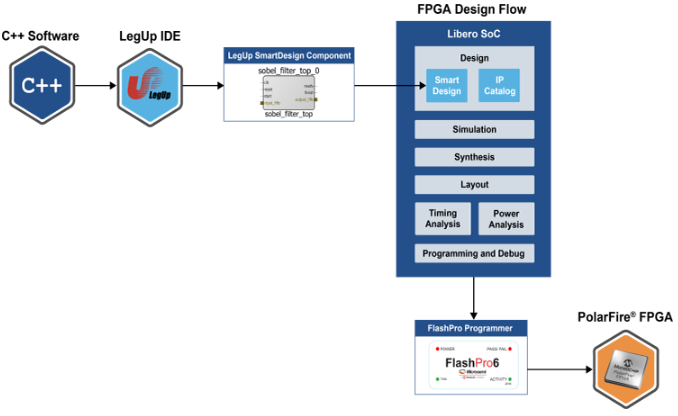

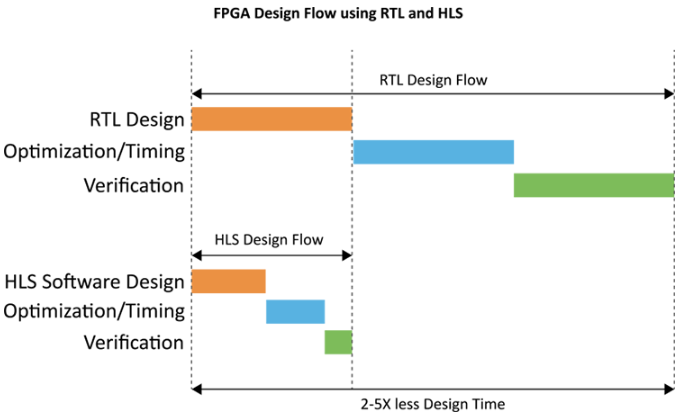

使用 Verilog/VHDL 从头开始为 FPGA 设计新的基于硬件的电机控制器可能非常耗时。通常,工程师已经有一个用 C/C++ 设计的正常工作电机控制器。在这种情况下,理想的解决方案是自动将现有的C++软件代码转换为等效的硬件实现,针对Microchip PolarFire FPGA。智能高级综合(SmartHLS™)工具和集成开发环境使这变得容易,它可以将C++软件编译成针对Microchip FPGA的硬件块。高级综合允许您将C++作为输入并生成 Verilog 作为输出。通常,您将 HLS 将生成的顶级C++函数标记为等效的硬件 IP 核。您可以在顶级C++函数中描述您的算法。然后,使用 HLS 编译指示和 HLS 库C++描述标准硬件接口,如 AXI、AXI 流或内存接口。HLS 的一个引人注目的好处是,它为您提供了比 RTL 设计C++的显著抽象级别,并提高了硬件设计和验证时间的生产力。使用 HLS 进行架构探索,因为该工具可以轻松添加或删除流水线寄存器,以实现用户指定的目标频率。

我们曾有一位客户使用 SmartHLS 将他们具有严格限制的高级电机控制设计迁移到我们的 FPGA。他们的主要目标是实现小于 3 us 的确定性延迟。此延迟是接收八个电机的编码器传感器和FPGA电机控制内核更新所有电机的电流输出之间的反馈时间。由于 DDR 和 PCIe 等外部 I/O 要求,客户还希望该设计以高于 200MHz 的时钟频率运行。他们还希望将设计安装在具有空闲空间的 PolarFire MPF500 设备上。

他们报告了他们的结果质量,并能够超越他们的设计目标。他们观察到周期延迟减少了50%,同时频率提高了以满足200 MHz的目标时钟频率。电机控制器的最终确定性延迟也减半至约2 μs。电机控制器的面积也缩小到适合300K LE PolarFire FPGA内部。

将原始C++电机控制器与改进的FPGA版本进行比较的实验表明,与Arm微控制器相比,基于FPGA的电机控制器在延迟方面具有2.5-6倍的加速,具体取决于微控制器和实时操作系统的抖动。

审核编辑:郭婷

-

FPGA

+关注

关注

1629文章

21748浏览量

603791 -

控制器

+关注

关注

112文章

16380浏览量

178289 -

电机

+关注

关注

142文章

9027浏览量

145613

发布评论请先 登录

相关推荐

阻碍PCB设计流程的生产率

【正点原子FPGA连载】第一章HLS简介-领航者ZYNQ之HLS 开发指南

优化上料组合、提高生产率

Vivado HLS深入技术助于降低整体系统功耗,提高系统性能

制造商可以使用自动机器视觉系统提高生产率

PADS高速布线提高设计生产率

使用PCB公差提高生产率

使用Infinity和InfinityXT探针提高生产率

使用网络实例比较FPGA RTL与HLS C/C++的区别

Microchip FPGA如何使用HLS C++提高电机控制应用的生产率

Microchip FPGA如何使用HLS C++提高电机控制应用的生产率

评论