介绍

计算高速链路™ (CXL™) 可满足处理器不断增长的内存带宽和容量需求,以加速高速计算应用,例如人工智能、云计算和机器学习。该行业正在迅速过渡,以利用这种新协议支持的功能,而采用的快速途径在很大程度上基于利用现有的PCI Express®(PCIe®)5.0物理层,电气和基础设施。

设计利用这一新兴标准在特定区域限制内优化容量、性能和功耗的大型系统需要仔细选择内存模块外形尺寸,同时考虑:

支持高带宽的接口

支持最佳容量的尺寸

通过允许适当的气流来支持功耗

针对多源进行标准化

模块化,可根据应用需求进行扩展

本文探讨了其中的一些设计方面。

内存技术

基于 CXL 的应用程序具有多个优点,包括更高的性能,因为它允许共享内存资源、CPU 内存空间与连接设备上的内存之间的内存一致性以及降低软件堆栈复杂性。以前,业界将无缓冲 DIMM (UDIMM) 和寄存器 DIMM (RDIMM) 用于内存应用。

UDIMM 通常用于低端服务器,并且最具成本效益,但由于命令/地址信号的高负载,它们不适合更高的速度。此外,它们每个通道最多只能支持两个 DIMM (DPC)。RDIMM 在 DIMM 上有一个寄存器,用于缓冲 DIMM 上的每个 DRAM 和内存控制器之间的地址和命令信号。这不仅可以在 DIMM 上安装更多的 DRAM,还可以提高模块的信号完整性,使其适合 CXL 运行的速度。所有这些因素使 RDIMM 外形尺寸的内存模块非常适合 CXL 应用。例如,标准 RDIMM 可以连接到主板上基于 CXL 的内存控制器,也可以插入 CXL 转接卡。

尽管RDIMM模块具有优势,但随着DRAM速度的不断提高(DDR5 *最大6400 MT/s),每个通道的引脚数量仍然相当大(DDR380为5引脚)。差分 DIMM (DDIMM) 是一种较新的内存模块外形,引脚数明显减少(84 个引脚),可实现 25.6GB/s 的数据吞吐率,延迟为 40ns,密度高达 256GB,允许 CPU 点对点连接到加速器和 I/O 设备。在减少引脚数的同时提高支持的数据速率,对于标准服务器环境中基于 CXL 的应用程序非常有益。

CXL 外形规格

随着接口速度的提高,设计背板面临一些挑战,例如:为驱动器和连接器选择合适的外形尺寸,以支持带宽要求、满足信号完整性需求、利用现有设计、满足功率预算并有助于改善气流。

企业和数据中心 SSD 外形 (EDSSF) 是 NVM Express™ (NVMe™) SSD 的另一种现有外形,支持嵌入式机箱更换,需要更小的连接器,允许从 PCIe 将背板设计用于 1U 和 2U 服务器,并显着减少 2U 气流需求,从而降低冷却成本。

EDSSF 针对特定类型的终端应用提供了几个选项:

E1.S 外形小巧,支持 5.9 毫米至 25 毫米之间的厚度,是超大规模和企业级计算节点和存储的理想选择,与传统 SSD 外形相比,可容纳更多 NAND 封装,以增加每个驱动器的容量。

E1.L 是一种外形规格,旨在最大限度地提高存储阵列(JBOD、JBOF)中每个驱动器和每个机架单元的容量,与传统外形规格(如专为旋转介质设计的 U.2)相比,具有卓越的可管理性、可维护性和散热特性。它支持 x4 或 x8 通道的 PCIe,最大厚度为 18 毫米。

E3 外形规格以 E3 的形式提供多种长度和高度选项。S 和 E3。L 表示 2U 垂直方向或 1U 水平方向。它们支持热插拔,热插拔的厚度从 7.5 毫米到 18 毫米不等,以最大限度地提高每个系统的驱动器,并支持 x4、x8 或 x16 PCIe 主机接口。

在背板上选择合适的连接器以支持 CXL 的速度也非常重要。Mini Cool Edge IO 连接器 (MCIO) 是下一代连接器类型,支持 0.60mm 间距连接器,采用纤薄外形设计,能够传输高达 56Gb/s 的高速信号。它被广泛采用为服务器中 PCIe Gen 5 内部布线的首选连接器,因为与传统的 PCB 布线方法相比,它允许更大的信号路径长度,同时保持 SI 性能。它具有成本效益、高度模块化、可扩展且极易维修,使其成为 CXL 应用的不错选择。

结论

为了设计需要内存池和扩展的 CXL 系统,可以使用几种现有的内存模块外形规格,其中包括满足带宽和容量需求的 RDIMM 和 DDIMM。使用的内存模块外形类型应基于最终应用的性能需求、延迟、负载和空间限制。

最后,为驱动器选择 EDSSF 外形尺寸以及用于背板的 MCIO 连接器将有助于利用现有的 PCIe 基础设施,并利用 CXL 的性能增强

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19537浏览量

231863 -

人工智能

+关注

关注

1800文章

48089浏览量

242202 -

机器学习

+关注

关注

66文章

8460浏览量

133420

发布评论请先 登录

相关推荐

FPGA的高速接口应用注意事项

高速电路中过孔设计注意事项

超声系统信号链的设计注意事项

胆机使用的注意事项

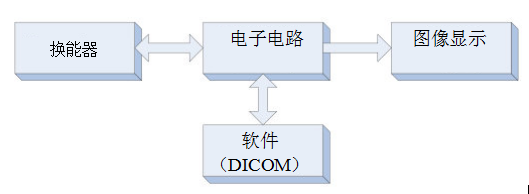

超声系统的信号链设计注意事项

计算高速链路的系统注意事项

计算高速链路的系统注意事项

评论