14 传输线拐角对信号的影响

高速信号沿着传输线传播时,如果传输线中出现90度的拐角,此处就会有阻抗突变发生,导致信号反射及失真。将90度拐角改为45度拐角,可以降低阻抗突变的影响。而使用线宽固定的弧形拐角,效果会更好。

为什么90度的拐角,会影响阻抗突变,进而导致信号反射和失真呢?这是因为直角弯曲处的额外线宽带来了阻抗变化。如下图左边是直角走线,右边是45度拐角走线。右边走线比左边走线少了一块(黑色缺角部分)。在实际PCB上,绿色是铜层,左边走线比右边走线多了一些铜层,走线宽度变宽了。它就像一个容性突变。

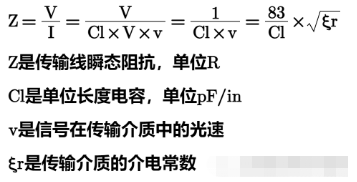

不过这个突变对于信号影响比较有限。在上一篇文章中,我们提到芯片内部管脚处的寄生电容大约在1pf左右。和芯片管脚寄生电容相比,这种直角走线带来的容性阻抗更小。例如一条宽度是1.65mm的传输线,它的直角走线造成的容性阻抗大约在100fF(0.1pf)量级。计算过程如下:

如上图左边红色框是一个宽度为W的正方形铜面,左边红色框中的铜面积(绿色)要比右边红色框中的铜面积多一些,这多出的部分就是容性阻抗变化的部分。我们取极端一点的值,假设左边铜面积比右边铜面积多一半。

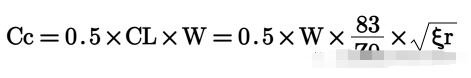

设左边正方形铜面的电容为Cs,则多出的电容Cc为

Cc=0.5xCs

之前的文章《信号完整性之关于电容的知识》提到单位长度电容为CL

因此Cc=0.5xCLxW

在另一篇文章《信号完整性之传输线二》中提到单位长度电容CL和传输线阻抗Z0之间的关系是

取ξr=4(常见FR4板材的这个参数大约在3.8~4.5之间),Z0=50R

Cc=0.5 x0.065 x2 x(83/50)=0.107pf=107fF。即一条1.65mm宽的传输线,直角走线比45度角走线多出107fF的寄生电容。

通常6层或者8层PCB设计中,DDR走线宽度大约在0.1mm,因此由它的直角走线带来的容性阻抗差值会更小。

除了这一点点容性阻抗的影响,不建议直角走线的另一个原因是拐角尖端处 的电场很高,它是由传输线外边缘的尖锐程度(直角)引起的。很高的直流电场会使拐角处的细丝变长,并且带来长久的可靠性问题。

总之,从信号完整性的角度看,之前提到的PCB叠层设计、传输线宽度变化、信号换层、返回路径间隙、源端和负载端的布局拓扑、距离等因素都比拐角走线重要的多。

15 感性突变对信号的影响

传输线上除了容性阻抗,也有感性阻抗存在。例如传输线上串联电阻的寄生电感、各种接插件的寄生电感、返回路径上的间隙等,都会带来感性阻抗。感性阻抗存在于信号路径,也会存在于返回路径。虽然信号路径和返回路径之间有局部互感存在,但是更多影响信号质量的还是这些存在于信号路径、返回路径的局部自感。

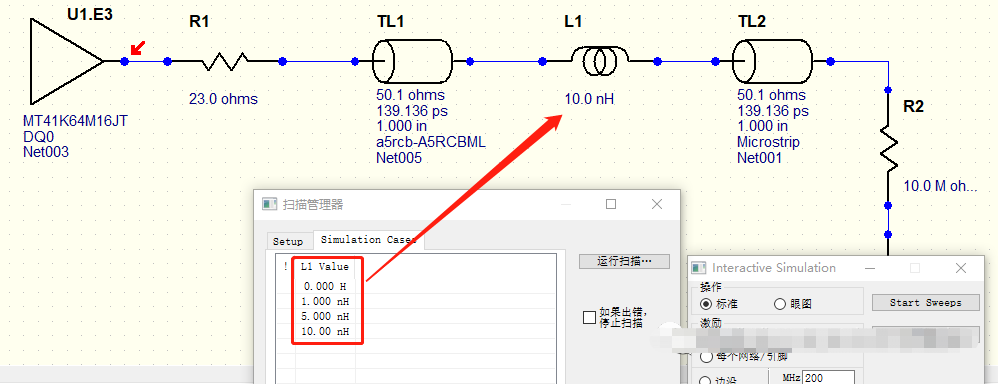

(一)串联寄生电感值对信号的影响

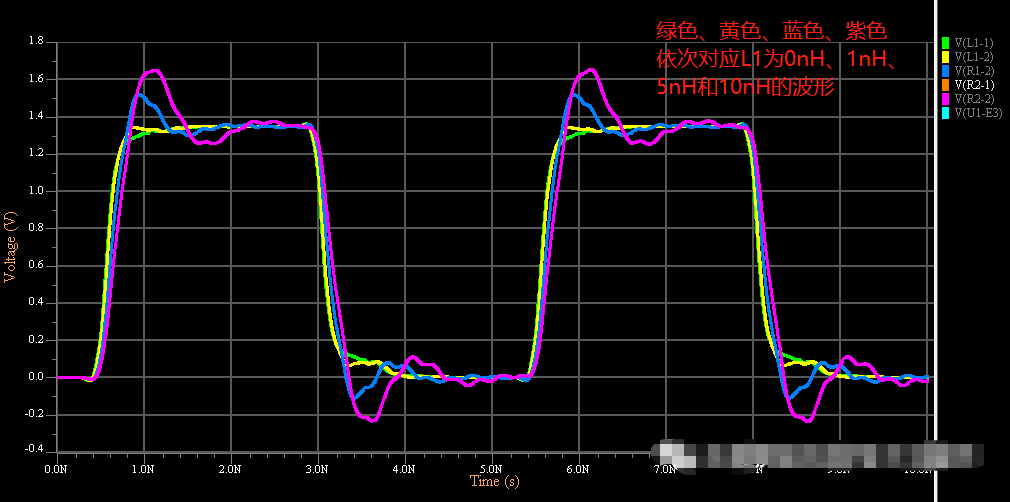

对于高速信号中快速上升的信号边沿,串联回路电感最初就像一个高阻抗元件,会产生返回源端的正反射,同时在负载端信号产生过冲。(结合上一篇的容性负载仿真波形,和本篇的感性负载仿真波形,可以看到容性负载带来负反射电压、感性负载带来正反射电压)。如下是一个仿真电路,L1分别取值为0nH、1nH、5nH和10nH。

仿真结果如下:感性负载在负载终端带来过冲,电感值越大过冲越明显。

(二)串联寄生电感最大值和信号上升时间的约束关系

这些电感是串联在传输线上,换句话说它是和Z0串联在一起,组成传输线。通常我们要求传输线阻抗的最大偏差是Z0±10%。让我们以此来算算看,按照这个阻抗偏差要求,能得到什么?

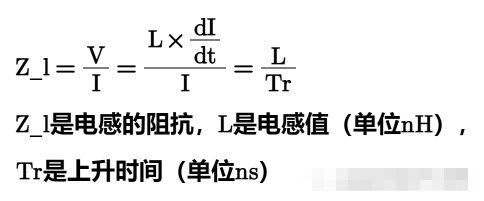

电感属于通直流隔交流的元件。高速信号的上升沿和下降沿,对于电感而言算是交流。高速信号的高电平和低电平,对于电感而言算是直流。下面是电感阻抗的公式:dI是高速信号上升沿电流,dt是高速信号上升沿时间.

为了确保电感阻抗小于传输线阻抗的10%,可以允许的最大电感值是:

例如传输线阻抗为50R,线上传输的高速信号上升时间为1ns,则可以允许的最大串联电感值为:Lmax=0.1x50x1ns=5nH。

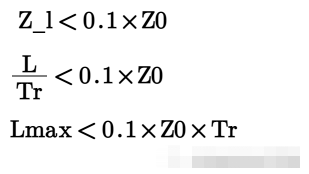

我们仿真电路中的信号源上升时间是Tr=0.195ns,则理论上可以接受的:传输线上串入的最大寄生电感是Lmax≈1nH。针对上图仿真电路,分别取值L1为0nH、0.5nH、1nH、2nH。仿真结果如下:可以看出在L1为1nH时,波形开始有一点过冲了。在2nH时已经比较明显了。

高速信号设计中,传输线上常见串接的是电阻或者连接器。来看看它们的寄生电感有多大。

针对SMT电阻,查了Yageo和Rohm的电阻参数,没有找到关于寄生电感的描述。只是在一本书中看到SMT电阻的串联回路电感大约在2nH左右。早期的DDR2还可以看到在地址线上串联源端电阻。后来的DDR3和DDR4就看不到源端串联电阻了。这可能是一个原因。

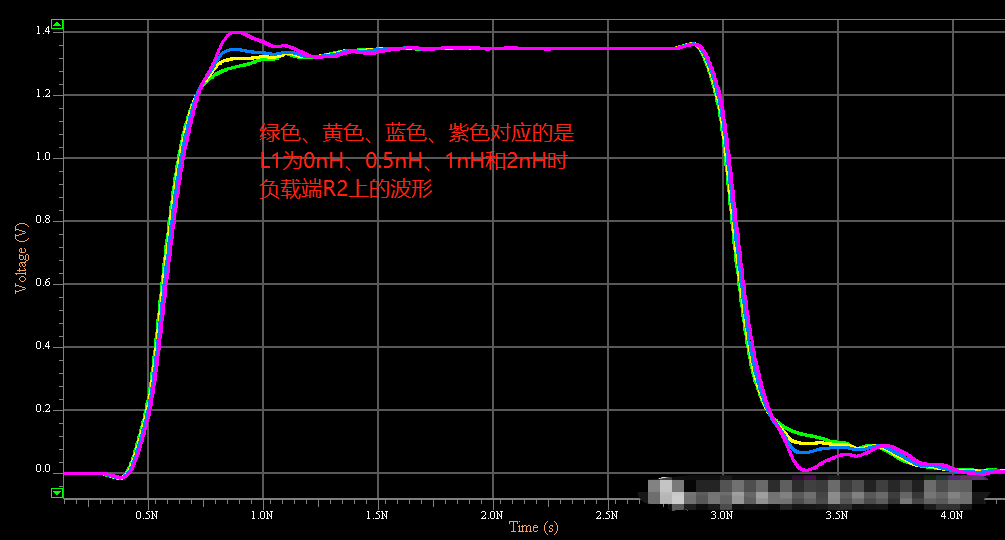

针对连接器,找了罗森博格、安费诺连接器的规格书,其中都没有提到寄生电感的参数。只是给出了可以支持的高速信号传输最大频率。如下是罗森博格一款连接器规格书中关于电气参数的描述。顺带说一句,它是一组差分信号连接器,因此阻抗是100R。

-

串联

+关注

关注

6文章

424浏览量

37577 -

pcb

+关注

关注

4319文章

23099浏览量

397938 -

信号完整性

+关注

关注

68文章

1408浏览量

95488 -

传输线

+关注

关注

0文章

376浏览量

24034 -

高速信号

+关注

关注

1文章

226浏览量

17700

发布评论请先 登录

相关推荐

信号完整性(五):信号反射

信号完整性简介及protel信号完整性设计指南

信号完整性之反射(七)

信号完整性之反射(七)

评论