常用电路模块的布局布线原则

常用存储器设计

*FLASH

*DDR

*DDR2

*DDR3

*QDR

1、SDRAM

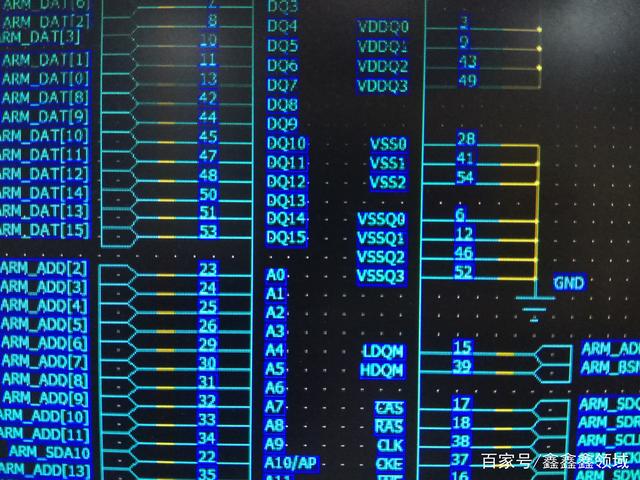

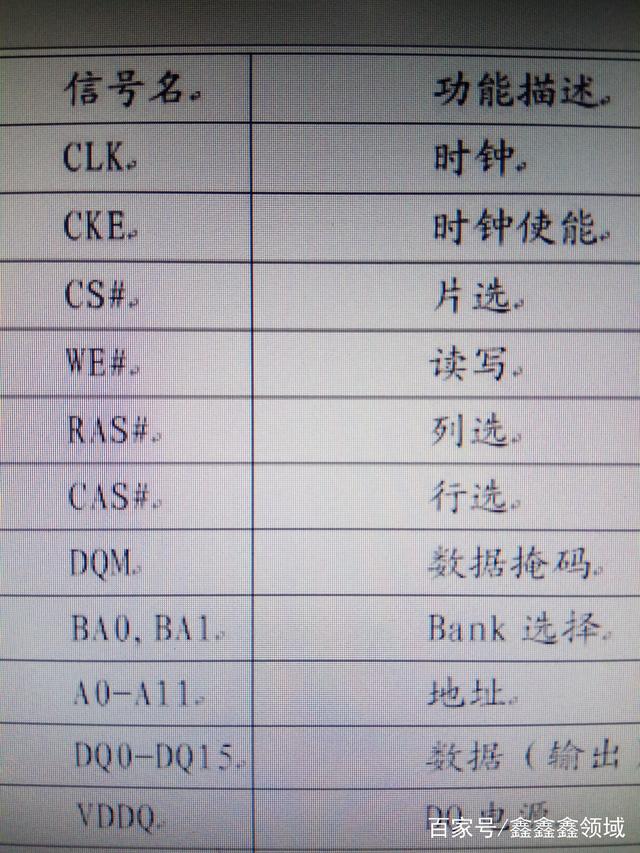

*管脚的定义解释

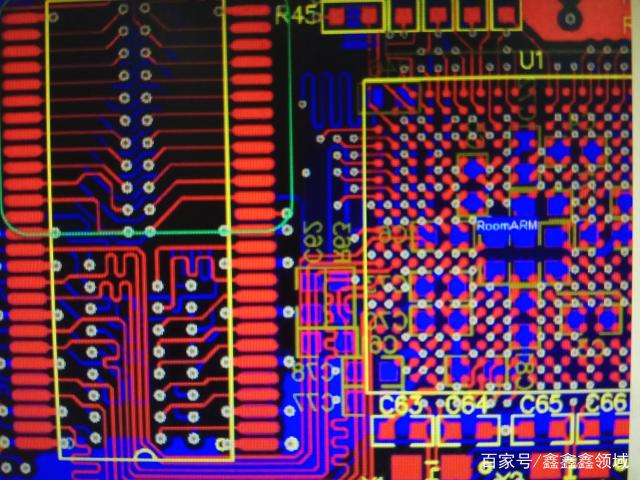

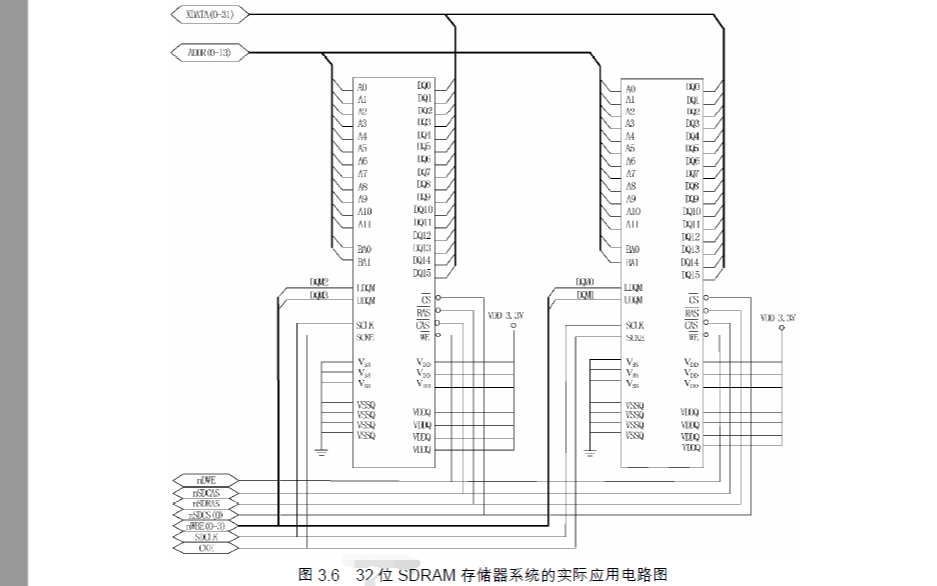

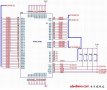

SDRAM(同步动态随机存储器)如下图:

SDRAM的布局

*SDRAM的布局原则是:靠近CPU摆放

*SDRAMx1片的时候,一般采取点对点的布局方式,如下图:

*当中间无排阻时:9000-1000密尔

*当中间有排阻时:1000-1300密尔

*SDRAMx2片时,相对于CPU严格对称

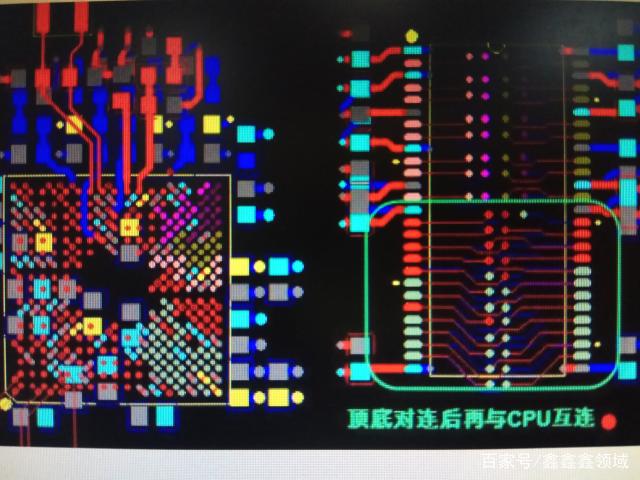

方案一:空间做的时候,与CPU放在同一面,如下图:

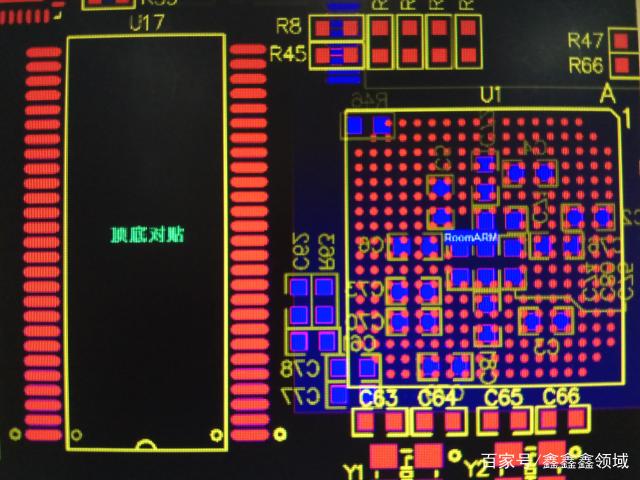

方案二:SDRAM顶底对贴,如下图:

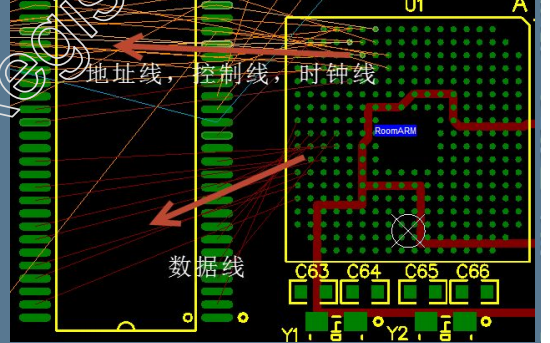

SDRAM的布线

*特性阻抗:50欧

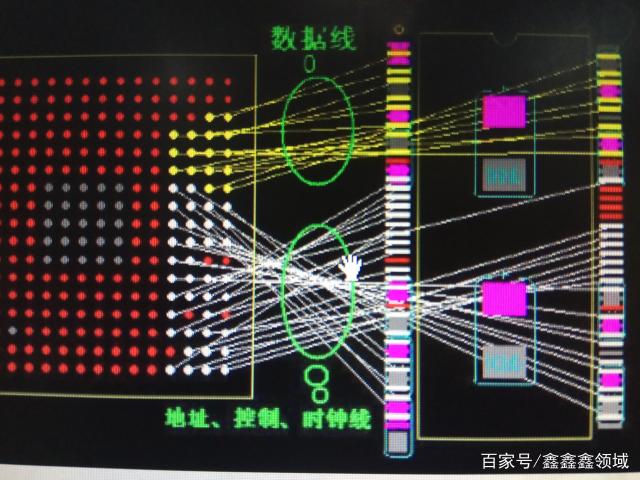

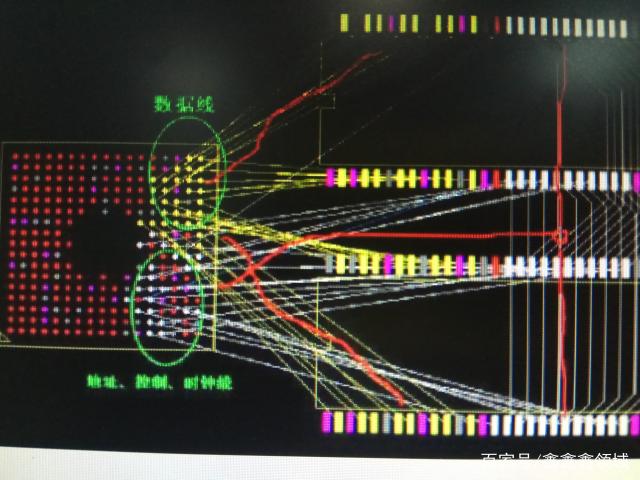

*数据线每9根尽量走在同一层(D0D7,LDQM;D8D15,HDQM)

*信号线的间距须满足3W原则

*数据线、地址(控制线)线、时钟线之间的距离保持20密尔以上或者3W

*空间允许的情况下,应该在它们走线之间加一根地线进行隔离。地线宽度推荐为15~30密尔

*保证完整的参考平面

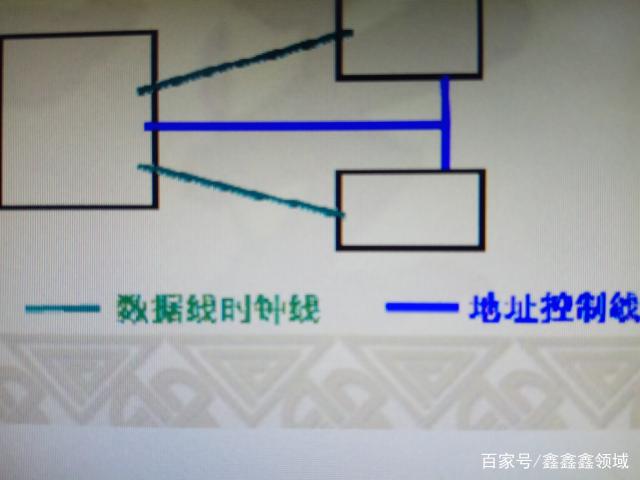

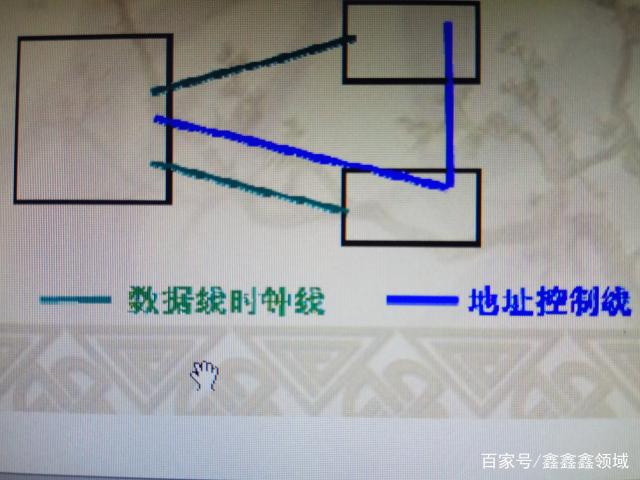

*布线拓扑结构(默认采用远端分支)-T点(过孔)打在两片SDRAM中间

远端分支(星形或者T形)

菊花链

*SDRAM的等长布线

*CLASS的规则

将所有数据线设为SDRAM_DATA_BUS;

地址线、控制线,时钟线设为SDRAM_ADDR_BUS

*等长规则

所有信号线参照时钟线的长度等长

*误差范围

数据线误差范围控制在+/-50MIL

地址线误差范围控制在+/-100MIL

*SDRAM的等长布线

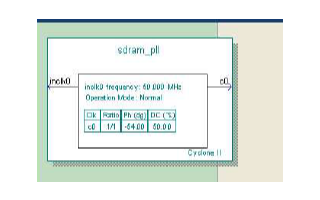

*远端分支布线情况,如下图:

-

SDRAM

+关注

关注

7文章

423浏览量

55241 -

FlaSh

+关注

关注

10文章

1635浏览量

148078 -

存储器

+关注

关注

38文章

7493浏览量

163873 -

DDR

+关注

关注

11文章

712浏览量

65360 -

时钟线

+关注

关注

0文章

6浏览量

3625

发布评论请先 登录

相关推荐

高速SDRAM存储器接口电路设计

基于FPGA的DDR2 SDRAM存储器用户接口设计

PCB的常用存储器设计的详细资料说明

SDRAM存储器模块的简介

如何使用Verilog设计Altera的DE2板上SDRAM存储器

常用存储器SDRAM的设计

常用存储器SDRAM的设计

评论