锁相环(Phase Locking Loop)作为无线通信系统的关键电路模块,有着广泛的应用。本栏将从简单锁相环入手,帮您理解锁相环的基本工作原理。

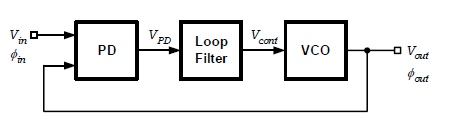

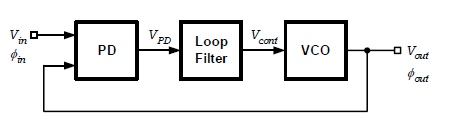

如图为简单锁相环的基本框图包含了三个模块:鉴相器(PD)、环路滤波器(Loop Filter)、压控振荡器(VCO)。只由这三个模块构成的锁相环并没有很好的实用性,但是能很好地帮助读者理解锁相这个概念,对于实际应用中的锁相环,还需要引入电荷泵、分频器等模块,小编将在之后的推送中详细介绍。本文只针对简单锁相环的分析。

1、压控振荡器(VCO)的数学模型

压控振荡器一般是由下式规定,为输入控制电压、输出对应频率的模块。

这样的一个系统 的改变会立刻导致

的改变会立刻导致 的改变。但这样的关系式并不能直观表达振荡器输出与时间的关系。

的改变。但这样的关系式并不能直观表达振荡器输出与时间的关系。

对于正弦波 ,正弦的自变量称为信号的“总相位”,相位随时间线性变化,其斜率为

,正弦的自变量称为信号的“总相位”,相位随时间线性变化,其斜率为 。这里,频率可被定义为

。这里,频率可被定义为 ,相位对时间的微分。因此可以写出已知频率的正弦波的相位关于时间的表达式:

,相位对时间的微分。因此可以写出已知频率的正弦波的相位关于时间的表达式:

现在考虑到输出频率为 的VCO,我们可以得到VCO输出波形为

的VCO,我们可以得到VCO输出波形为

上式中的总相位包含三项,第一项为线性变化的, 作为一个常数并不重要,因此只有第二项是重要的,这一项

作为一个常数并不重要,因此只有第二项是重要的,这一项 ,被称为“剩余相位”,用

,被称为“剩余相位”,用 表示。因此可以把VCO看作输入和输出分别为控制电压和剩余相位的系统:

表示。因此可以把VCO看作输入和输出分别为控制电压和剩余相位的系统:

而VCO的工作就像一个理想的积分器,其传输函数为

2、鉴相器(PD)

鉴相器是这样一种电路,其平均输出 V~out ~ 与两个输入间的相位差 成线关系,理想情况如下图,这条直线的斜率 K~PD ~ 就是鉴相器的“增益”,其单位为V/rad。

成线关系,理想情况如下图,这条直线的斜率 K~PD ~ 就是鉴相器的“增益”,其单位为V/rad。

鉴相器一个熟悉的例子就是异或门(XOR)。当两输入的相位差变化时,输出端的脉冲宽度也相应的变化,从而可以得到一个与相位差成正比的直流电平。

3、基本锁相环结构

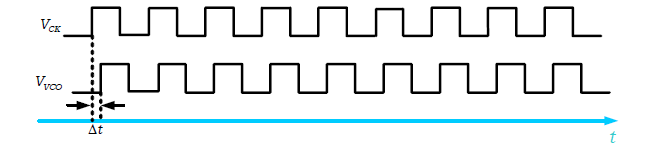

首先我们考虑个VCO输出相位与参考时钟对齐的问题。如下图, V~VCO ~ 的上升沿与 V~CK ~ 的上升沿“偏差” ,我们可以通过短时间内提升VCO频率,使VCO更快地积累相位,逐渐减小相位误差。

,我们可以通过短时间内提升VCO频率,使VCO更快地积累相位,逐渐减小相位误差。

可知当符合两个条件(1)VCO振荡频率可调(2)有比较两个相位的电路,就可以使VCO输出相位与参考信号相位对齐,对齐的操作被称为“相位锁定”。

但是鉴相器的输出并不是我们希望的直流信号,应此需要在鉴相器和VCO之间引入一个环路滤波器(低通滤波器),抑制鉴相器输出的高频分量。这样就构成了基本的锁相环。

为了后续分析,必须仔细定义相位锁定的条件。书中对相位锁定的定义是:如果VCO相位与参考相位差值不随时间变化,环路就锁定了。将这个定义转换为表达式,就可以得到如下公式。

之后我们观察锁定条件下环路各节点的电压波形。在锁定状态下,VCO 输出信号与参考信号频率一致,相位差恒定;而鉴相器输出脉冲宽度恒定;VCO控制电压有较小的脉动,这种脉动被称为“波纹”(ripple),波纹大小受环路滤波器设置影响。

而对于输入输出相位差,我们可以通过下式计算。从关系式中我们可以得到两个要点(1)如果锁相环输入频率变化,那么相位误差也同时变化;(2)增大鉴相器和VCO的增益 可以减小相位误差。

可以减小相位误差。

4、锁定状态下的瞬态过程

1.假定起始时,锁相环处于锁定状态,在某一时刻 ,输入信号获得一个相位阶跃

,输入信号获得一个相位阶跃 ,也就是

,也就是 。相位阶跃显示出 * * V

。相位阶跃显示出 * * V * in ** *的上升沿早于周期性规定的时间。

参考相位阶跃导致鉴相器产生的脉冲宽度增大,迫使 V~cont ~ 逐渐升高,VCO输出频率改变,减小相位误差。在这个过程中,VCO频率变化使VCO输出提供增加的相位 :

:

增加的相位体现在图中阴影面积。

观察这个过程我们可以归纳两点:1)锁相环回到锁定状态后,所有参数都回到了初始值。2)分析锁相环时,我们很难观察相位和频率随时间的变化,但是振荡器的控制电压确是各很好观测的点。

2.假定起始时,锁相环处于锁定状态,在某一时刻 ,输入信号获得一个频率阶跃

,输入信号获得一个频率阶跃 。这样鉴相器输入两个信号频率不同,产生逐渐增宽的脉冲,

。这样鉴相器输入两个信号频率不同,产生逐渐增宽的脉冲, 随时间增大。当

随时间增大。当 达到

达到 时,鉴相器输出脉冲宽度减小,最终稳定到一个值使其直流分量为

时,鉴相器输出脉冲宽度减小,最终稳定到一个值使其直流分量为 。

。

在这个过程中,锁相环的控制电压和相位误差有一个永久的改变, 只是跟踪

只是跟踪 。

。

-

锁相环

+关注

关注

36文章

637浏览量

91360 -

振荡器

+关注

关注

28文章

4196浏览量

143261 -

pll

+关注

关注

6文章

991浏览量

138459 -

鉴相器

+关注

关注

1文章

63浏览量

23939 -

无线通信系统

+关注

关注

0文章

75浏览量

12010

发布评论请先 登录

LabVIEW锁相环(PLL)

锁相环(PLL)电路设计与应用

PLL锁相环的基本结构及工作原理

PLL锁相环的特性、应用与其基本工作过程

锁相环PLL的基本工作原理简析

锁相环PLL的基本工作原理简析

评论