大家在参加IC相关工作笔试或者面试的时候,经常会碰到类似的题目:

怎样用D触发器、与或非门组成二分频电路?

用D触发器实现3倍分频的Verilog描述?

任意切换1-8分频,且无论奇分频还是偶分频,占空比均为50%,写出verilog代码;

时钟分频电路(分频器)在IC设计中经常会用到,其目的是产生不同频率的时钟,满足系统的需要。 比如一个系统,常规操作都是在1GHz时钟下完成,突然要执行一个操作涉及到模拟电路,所需时间是us量级的,显然用1GHz(周期是1ns)的时钟进行操作是不合适的。

时钟分频器电路可以分为数字分频器、模拟分频器和射频分频器等。 数字分频器通过一个计数器来进行分频,权值为分频系数。 模拟分频器就是一个频率分配器,用带阻带通实现。 射频分频器也是滤波器原理,用带内外衰减,阻抗匹配实现。

这篇文章IC君就跟大家聊一聊数字分频器。 对于精度不高的场合,数字分频器分出的时钟就可以满足要求。 常用到数字分频器有2,4,6,8,…… 偶数分频,也会有3,5,7,9…… 奇数分频,甚至还会有8.7,11.2,6.432,…… 分数分频。

偶数分频是最容易掌握的,奇数分频就有些技巧,如果你不知道奇数分频技巧,就可能会被一些公司的面试或者考试题目给难住,错失一些机会。 而像8.7,11.2,6.432,…… 这种分数分频器就更需要技巧。 掌握这些通用的技巧就能很快的实现各种分频器,满足系统的需求。 下面IC君就跟大家分别聊一下偶数分频、奇数分频、分数(小数)分频器。

1偶数分频

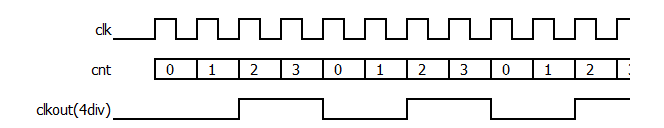

偶数分频器的实现简单,用计数器在上升沿或者下降沿计数,当计数器的值等于分频系数的一半或等于分频系数时,信号翻转。 偶数分频器分频原理如下图所示:

上图的的分频系数是4,就是4分频。 电路原理是用一个上升沿计数的计数器,每次计数到2时输出信号clkout翻转一次,每次计数到4时clkout再翻转一次,一直周期重复下去。 其他的偶数分频器原理也是一样。 从波形中可以看出cnt

从00->01->10->11->00......一直循环记数,如果你够仔细,就可以看出cnt的最高位其实也是一个4分频的时钟。

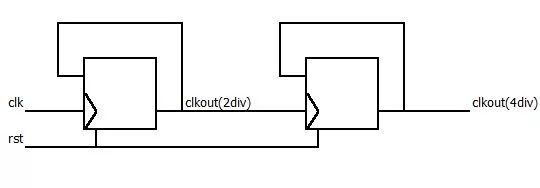

如果偶数分频系数是2的幂,就可以用2分频器级联得到; 例如4分频就是两个2分频级联,下图就是用两个2分频器级联得到4分频器。

2奇数分频

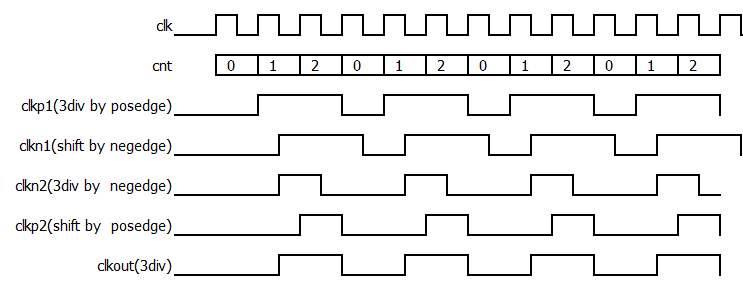

奇数分频器跟偶数分频器一样,当计数器的值等于分频系数(加1或者减1)的一半或等于分频系数时,时钟信号翻转。 奇数分频器分频原理如下图:

上图的分频系数是3,用一个计数器在上升沿计数,每次计数到1翻转一次,每次计数到3再翻转一次,然后周期重复得到信号clkp1,它的周期就是clk的3倍,但是它的占空比不是50%(占空比就是clk为高的时间占整个时钟周期的百分比)。 奇数分频想通过计数器直接分频出占空比是50%的时钟是不可能的,必须要通过中间的临时波形,做一些逻辑“与”“或”的动作才能得到占空比50%的分频时钟。

用一个下降沿的D触发器锁存clkp1得到信号clkn1,把信号clkp1和信号clkn1做逻辑“与”就得到了占空比50%的3分频时钟信号clkout。

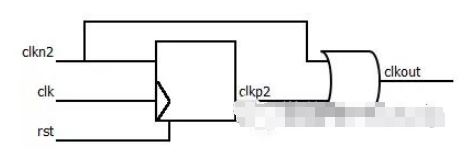

另外一种产生3分频时钟的方法:假设计数器在计数到1的下降沿分频后的时钟信号clkn2翻转一次,计数到2的下降沿clkn2再翻转一次,

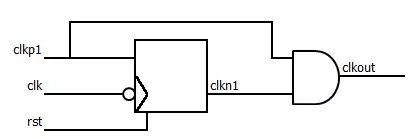

再利用下图电路调整占空比到50%:

用一个正常的D触发器锁存clkn2得到信号clkp2, clkn2“或”上clkp2就可以得到占空比50%的3分频时钟信号clkout。

其他的奇数分频器调整占空比的原理也是相同的。

3分数分频

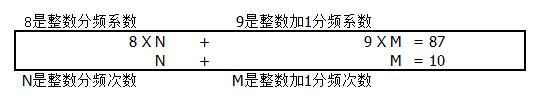

分数分频也叫小数分频器,比如8.7分频。 因为没办法用计数器表示0.7这种数字,所以就用一个等效的概念来进行8.7分频,原时钟87个周期的总时间等于分频后的时钟10个周期的总时间;

先做3次8分频得到时钟周期数是24,再做7次9(8加1)分频得到时钟周期数63,总共就87个时钟周期; 在这87个时钟周期里面分频时钟跳变20次总共10个周期。 分数分频器的原理可以用下图来概括。

用整数部分zn(=8)作为一个分频系数,zn加1(=9)作为另外一个分频系数组成一个小数分频器。

根据上面的原理可以列出下面的二元一次方程组

zn*N+(zn+1)*M=87 ......(1)

N+M=10 ...(2)

可以解出N和M的值分别是3和7。

如果分频系数6.432,那么有下面的二元一次方程组,zn是6

zn*N+(zn+1)*M=6432 ......(1)

N+M=1000 ......(2)

解出N和M的值分别是568和432,这个值就很大了,计数器的位宽也变大了,也就是说小数部分位数越多,需要的计数器的位宽越大,消耗的硬件资源越多。 不过568,432,1000这几个数有公约数,可以除以最大公约数,把计数数值减小。

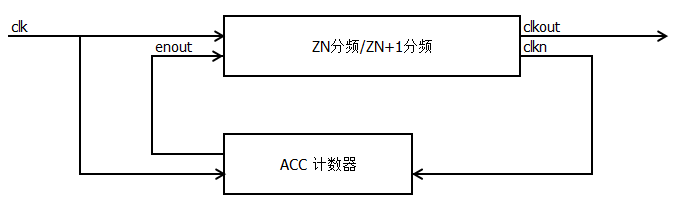

如下图所示:一个小数分频器就有两部分组成:ZN和ZN+1为分频系数的多路分频器,还有一个ACC计数器。

分频器在输入信号enout=0的时候是ZN分频;

分频器在输入信号enout=1的时候是ZN+1分频;

ACC计数器的作用对ZN分频和ZN+1分频的次数计数,对于一位小数计数总次数为10(两位小数为100...),输出信号enout决定下次是ZN分频还是ZN+1分频。

由于篇幅关系,小数分频器的具体电路设计就留到下一篇文章讲。

-

分频器

+关注

关注

43文章

448浏览量

50218 -

Verilog

+关注

关注

28文章

1355浏览量

110766 -

时钟

+关注

关注

11文章

1756浏览量

132137 -

触发器

+关注

关注

14文章

2024浏览量

61469 -

分频电路

+关注

关注

7文章

45浏览量

36064

发布评论请先 登录

相关推荐

奇数分频如何得到呢? 解读奇数分频和逻辑分析仪(ILA)的使用

请问AD9518 VCO偶数分频失锁是什么原因

基于Verilog的FPGA分频设计

分频器的作用是什么 半整数分频器原理图分析

基于复杂可编程逻辑器件和VHDL语言实现半整数分频器的设计

偶数分频、奇数分频、半整数分频和小数分频详解

偶数分频/奇数分频/分数分频详解

偶数分频/奇数分频/分数分频详解

评论