FPGA之三八译码器

一听到三八译码器这个东西可能会感觉有点熟悉,其实在STC89C51系列单片机中,里面就有一个三八译码器,就是一开始的流水灯程序,LED0-7这八个LED!但是怎么在FPGA中实现三八译码器呢?其实很简单。

1、创建好工程,像上一篇文章那样,我就不多说了,忘记的同学可以到下面这个网址查看,

https://blog.csdn.net/Jiang_YW/article/details/89220995

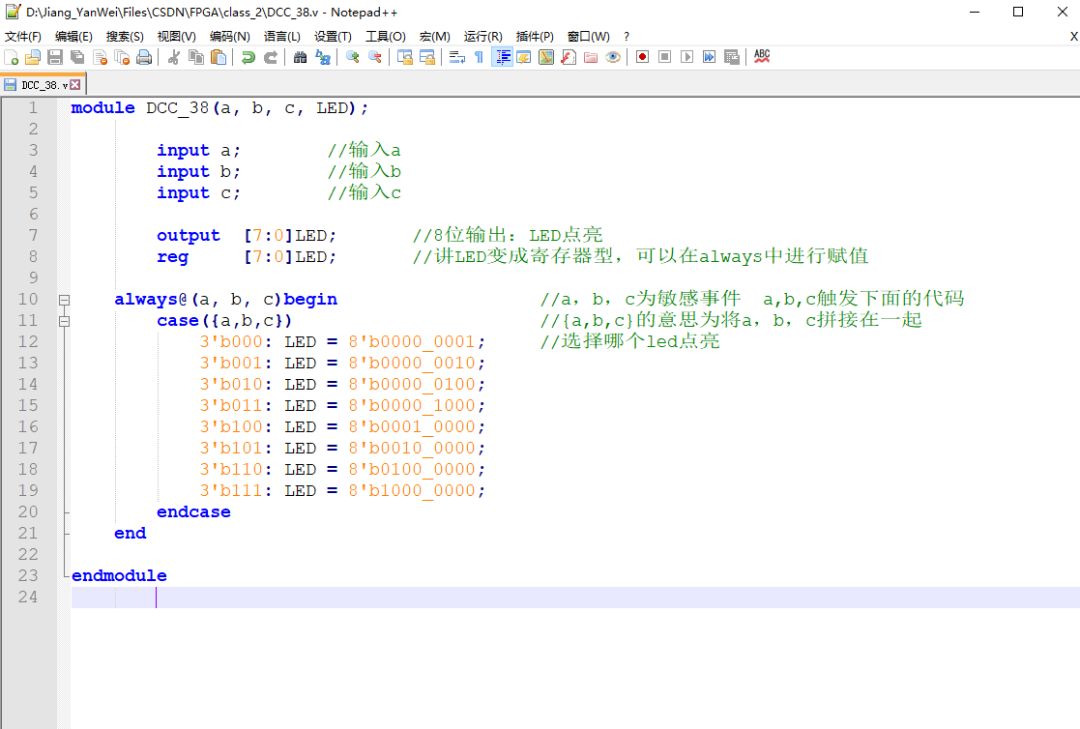

2、创建好工程以后,再新建一个Verilog HDL文件,我命名为DCC_38.v,然后把文件添加到工程里面。

建议新手先学一下Verilog HDL语法,不然对这些内容会看不懂,Verilog相对于VHDL要简单,而且看起来要更相似与C语言,学过C的话,再学Verilog会简单一点点。

推荐网址:https://www.cnblogs.com/SYoong/p/5849168.html

有好几个章节,有兴趣的的同学可以学学。

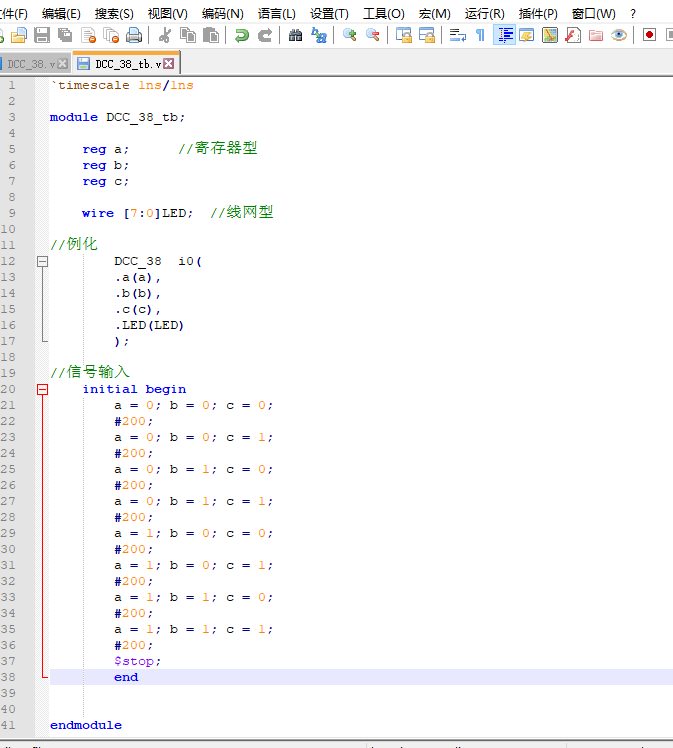

3、把上面工程编译一遍没错之后,就可以开始写tb(testbench)文件了,再新建一个DCC_38_tb.v文件,编写激励程序。

写完之后也添加到尽快工程里面进行编译。

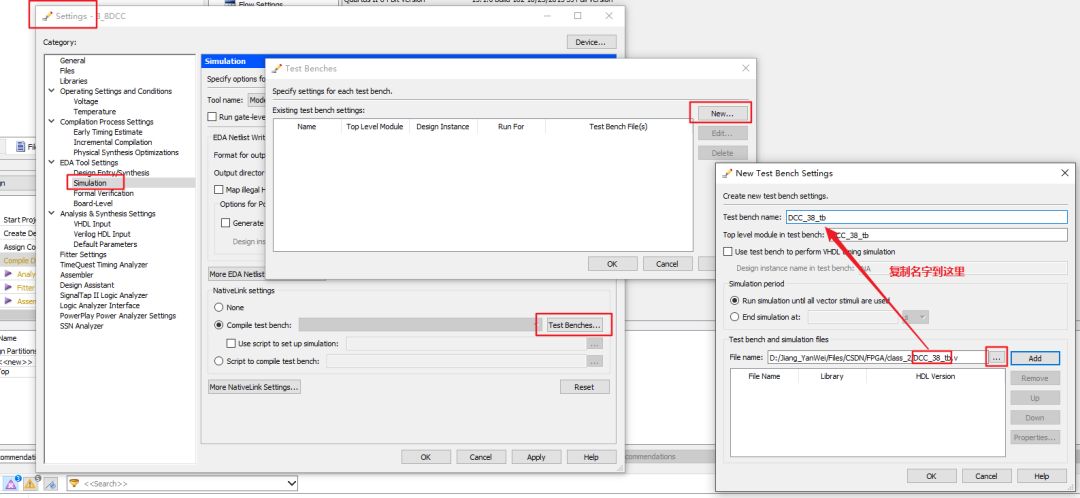

4、点击Assignment → Setting

按上图操作完成之后,点击add跟OK,保存好即可。

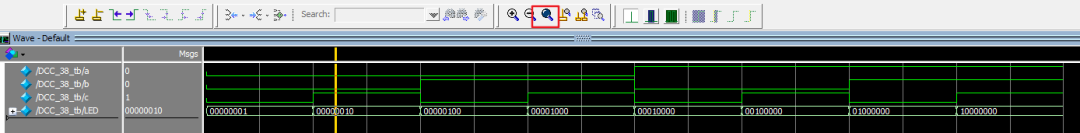

一开始没仿真图出来,点击上面红色框的黑色放大镜即可。

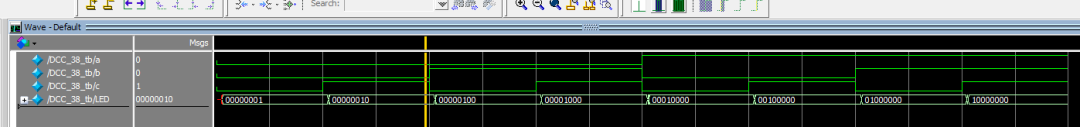

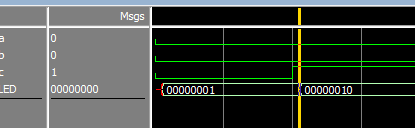

由上图可见仿真没有错误,那么就先关闭ModuleSim。

6、然后点击Gate Level Simulation进行后仿真,点击Run。操作与上图一样

在图里可以看见LED的输出有一点点的延迟,这是正常现象。

为什么这一瞬间LED的值会为零呢?

实际上是芯片0000_0001→0000_0000 → 0000_0010进行了两次的反转,其他的也一样。

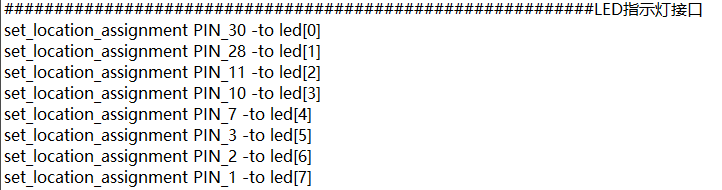

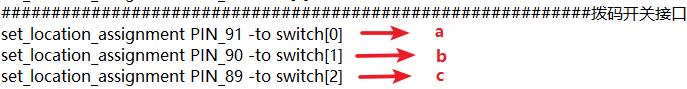

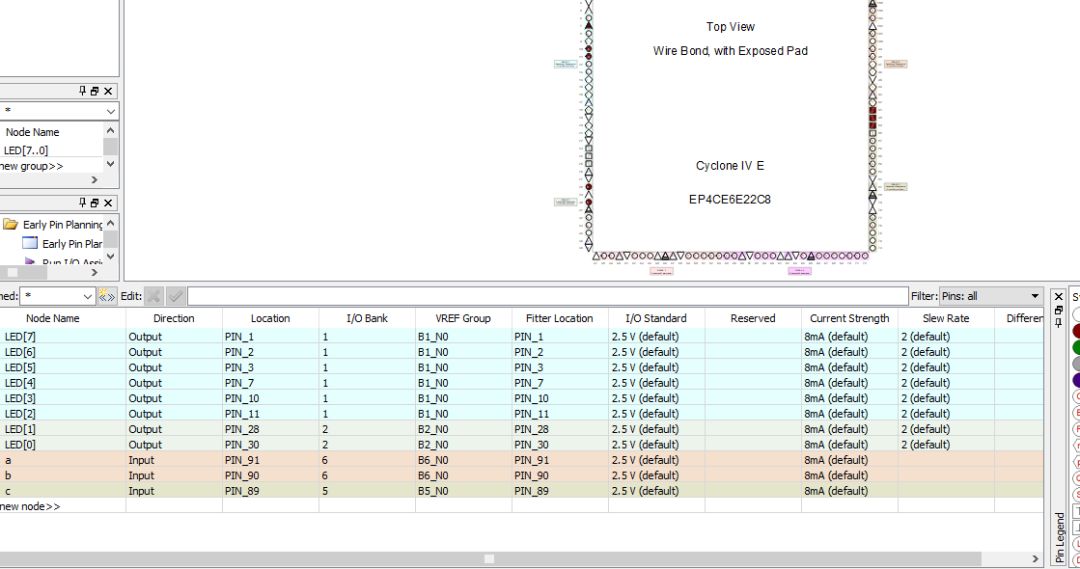

7、点击Pin Planner,参考引脚配置,进行引脚分配

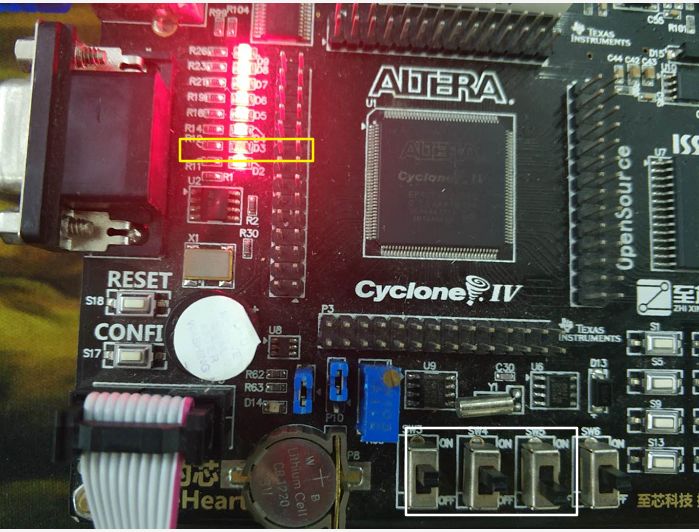

8、再编译一遍程序,就可以烧录到板子里面。

上图只看左边三个开关,第四个忽略

程序ok。

-

FPGA

+关注

关注

1663文章

22492浏览量

638937 -

单片机

+关注

关注

6078文章

45568浏览量

673296 -

译码器

+关注

关注

4文章

313浏览量

52420 -

STC

+关注

关注

14文章

299浏览量

70300

发布评论请先 登录

三八译码器的应用

三八译码器的相关资料推荐

基于FPGA的高速RS编译码器实现

基于FPGA的RS码译码器的设计

基于FPGA 的LDPC 码编译码器联合设计

译码器的逻辑功能_译码器的作用及工作原理

通过采用FPGA器件设计一个Viterbi译码器

关于Actel 的FPGA的译码器的VHDL源代码

FPGA之三八译码器

FPGA之三八译码器

评论