不久前,英飞凌科技股份公司宣布其适用于高压MOSFET的QDPAK和DDPAK顶部散热(TSC)封装技术正式注册为JEDEC标准。按照JEDEC的规定,一家厂商的技术注册和认证成为JEDEC标准之后,其他厂商便可以免费从JEDEC标准组织下载并使用这些标准,只要遵守标准所定义的尺寸和公差,就能够在行业里声称是跟JEDEC标准兼容,并且不设置专利门槛。厂家只需要制造符合此业界通行标准的产品即可。

也就是说,QDPAK和DDPAK表面贴装(SMD)TSC封装设计将会与TO247和TO220一样,可供业界免费使用,并成为行业标准。

不久前,英飞凌科技电源与传感系统事业部大中华区应用市场总监程文涛还与业内媒体一道交流了QDPAK和DDPAK SMD TSC封装设计的研发背景、技术优势,和在推广该封装技术过程中面临的挑战以及英飞凌如何解决这些挑战等话题。

图:英飞凌科技电源与传感系统事业部大中华区应用市场总监程文涛

为何要推出TSC封装设计?

在半导体行业发展的相当一段时间里,不论是功率半导体、模拟半导体,还是数字半导体,芯片的尺寸都在不断地缩小,工艺在不断地微缩。具体到功率半导体方面,过去十多年的芯片演进主要在晶圆部分,比如使用更小的芯片尺寸,实现更低的导通阻抗等等,“随着时间的推移,英飞凌逐渐发现封装技术成为了突破瓶颈的关键方式,”程文涛在与媒体交流时表示。

高压超结硅功率器件的FOM值基本已经达到了物理极限,在此情况下要想继续降低导通阻抗或者是实现更高的能效,封装技术是继续把硅的功率发挥到极致的必经之路。不仅是硅基半导体,现在大热的宽禁带半导体SiC/GaN也需要仰仗新的封装技术。

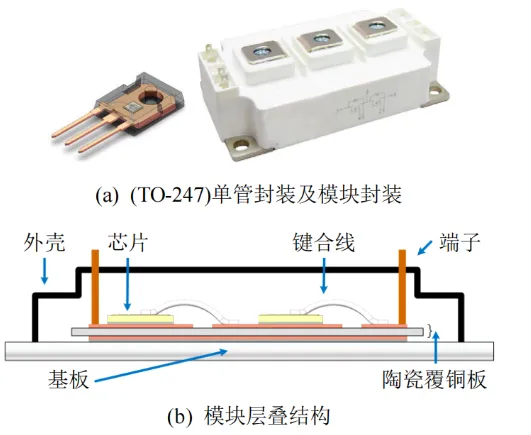

据程文涛介绍,英飞凌的TSC封装技术名称叫QDPAK与DDPAK,“其前身就是我们所熟知的DPAK,即TO252封装。其中QDPAK相当于4个DPAK并排;DDPAK则是两个DPAK并排在一起。”他解释道。

QDPAK封装的主要优势有四个:

满足更大功率需求:优化利用电路板空间,采用开尔文源极连接,减少源极寄生电感;

提高功率密度:顶部散热可实现最高电路板利用率;

提高效率: 经优化的结构具有低电阻和超低寄生电感,可实现更高效率;

减轻重量:综合优化散热和发热,有助于打造更小巧的外壳,从而减少用料,减轻重量

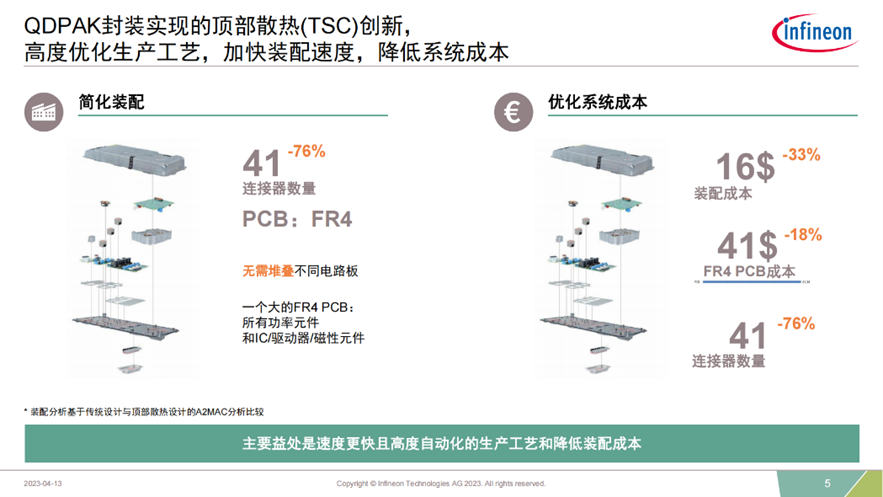

TSC封装为客户带来的裨益

其实QDPAK和DDPAK这两大顶部散热封装技术能够带来最大的益处在于:高度优化了生产工艺,让整个装配过程步骤变少,自动化制造流程更简洁,最终在下游厂商端实现包括PCB数量、层级和板间连接器用量减少,带来装配及整体系统成本大幅降低。

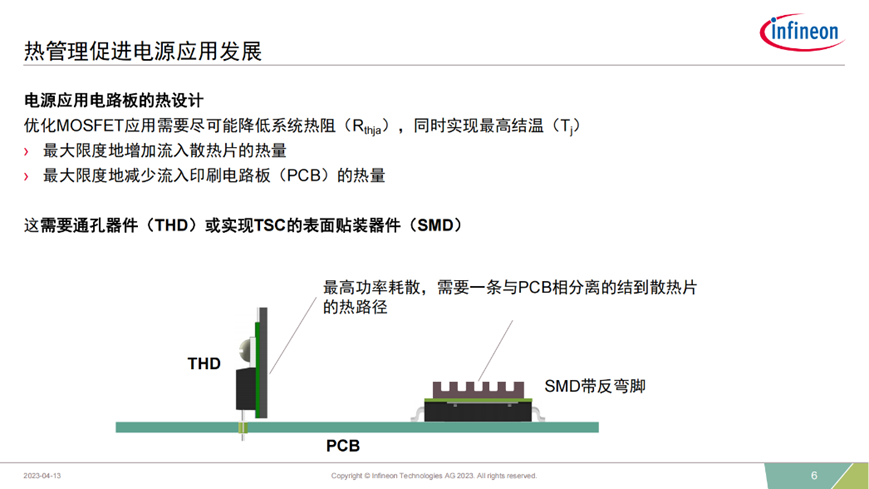

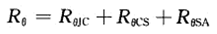

优化MOSFET应用需要尽可能降低系统热阻(Rthja),同时实现最高结温(Tj)。如此一来能够最大限度地增加流入散热片的热量,并最大限度地减少流入PCB的热量。

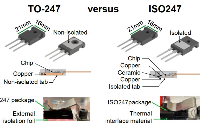

熟悉功率半导体行业的读者应该还有印象,10年前千瓦及以上的大功率应用基本以插件封装(THD)技术为主,例如大家熟知的TO247、TO220封装。这类插件封装技术的优势在于,在当时的装配和封装工艺下能使工程师最大限度地利用外加的散热片,非常高效地将芯片内部产生的热量散发出芯片之外,让芯片能够工作在一个大功率的应用场景中。

但随着数据中心、4G及5G无线通信宏基站等设备对于功率密度的要求越来越高,设备尺寸越做越小。开始要求电源应用的电路板设计中采用更少,或不用独立散热片,同时把更多的热量均匀地散发到整个设备之外。英飞凌经过长时间与产业链下游的行业头部客户以及工程师讨论,最终在业界达成共识,那就是顶部散热才是解决这一矛盾的根本途径。

贴片化是从带独立散热片的插件封装走向更高功率散热的第一步。一般贴片封装的散热主要是靠芯片底部跟PCB(印刷电路板)之间的接触,利用PCB铜箔把芯片产生的热量散发出去。但是这样做的一个明显弊端在于,它需要耗费比较大的PCB铜箔面积,才能有效地把热量散发出去。如果在此期间不能够用面积足够大的PCB铜箔,那么在芯片底部就会形成一个热点,而这个热点会给PCB带来很大的压力。目前业界常用的PCB是FR4材质,该材质的最高温度上限为110℃左右。在更高的功率设计中,底部散热封装无法通过贴片和PCB之间结合均匀地把更多热量散出去,导致这种散热方式走到了瓶颈。

而顶部散热只需要在顶部使用一个薄薄的散热片,而不靠底部的散热片去散热,它可以在同样的PCB材质下,更有效、更均匀地把热量散发出去。同时,它给用户带来的好处便是在同样的散热面积下,可提升整个设备对外输出的功率。。

由于贴片顶部散热封装技术需要所有的器件都贴在同样一个平面的PCB板上。如果对成本进行权衡,客户希望用相同厚度的散热片即可把设备中的热量均匀地散发出去。由此看出,同等的器件高度就成为关键因素所在。因此,英飞凌在其顶部散热封装技术设计内定义的封装厚度为2.3毫米,英飞凌希望通过这次跟JEDEC标准组织的互动,能够使2.3毫米的厚度成为一个业界通行的做法。

至于为何会选择2.3毫米,程文涛解释说,首先要考虑到顶部散热的做法不能成为其它非顶部散热芯片的应用障碍,如果其它非顶部散热的封装厚度比较厚,那么顶部散热的封装就不能比它薄,否则会产生热量散不掉的问题,或是需要加很厚的散热垫。

二是,英飞凌研究了行业中很多的贴片封装尺寸,在大部分的非顶部散热以及顶部散热封装共存的情况下,选择了2.3毫米。这样的厚度能够让足够多的器件并存在同一块PCB板上。

TSC封装的普及面临哪些挑战?

其实英飞凌推广TSC封装技术已有3年之久,程文涛回忆英飞凌在推广TSC封装技术遇到的挑战时表示,在行业内做一个创新的推广,阻力是来自方方面面的,包括生产线方面、安规方面的要求以及散热材料配合等阻力。要想完成TSC封装技术的推广,则需要整个产业链相互配合才能让一个创新最终落地。

首先面临的是接受度的问题,最开始会受到电源领域工程师的质疑,他们之前最为信赖的有效散热封装技术是TO247和TO220,他们会首先质疑新的封装形式在散热能力上是否比原有的散热方式更好;

二是之前生产线上的加工工艺不能满足顶部散热的安装需求。在此需要解决的问题是,在同样一个PCB板上焊接多个顶部散热的芯片,怎样才能保证这些顶部散热的芯片的高度是一致的,利用同样一个模具所加工出来的平面散热片,怎样才能均匀地贴在这些使用顶部散热的芯片上,并且能够保证它们之间的热阻基本一致等等。

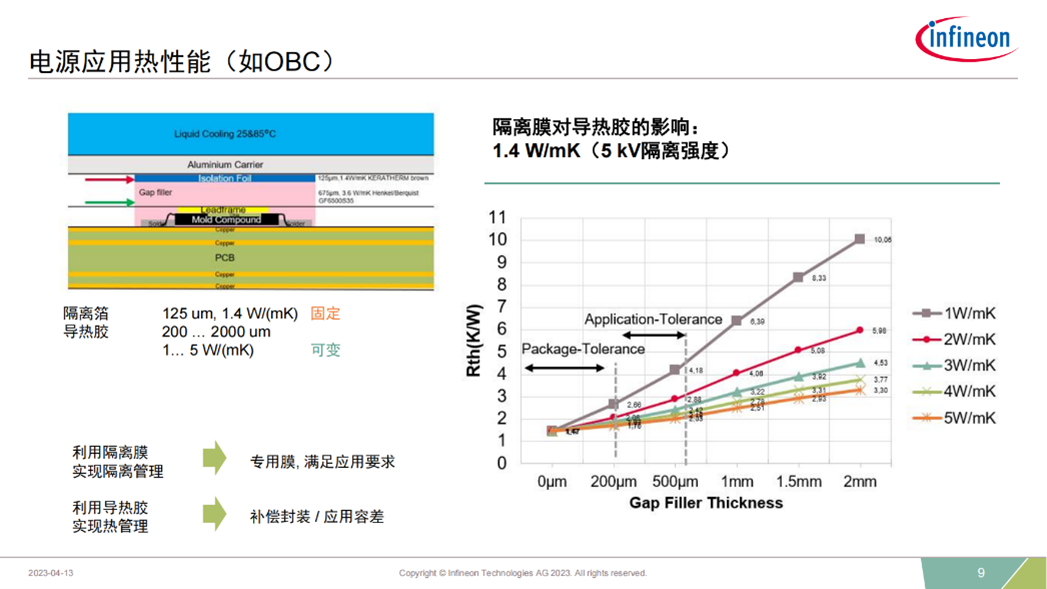

英飞凌与大客户一起共同摸索,经过近两年的时间找到了一些行之有效的应对办法。一般顶部散热接触的电平是处理高压的MOS管漏极,需要经过安全可靠的隔离才能接触外部设备,这一点与插件式封装非常类似。

但如何将多个并联,或者并排摆放的顶部散热芯片里面的热量均匀地散发出去呢?“目前最有效的方式就是用Gap Filler导热胶均匀地把热量传导到顶部的散热片里面去。在这里列出了不同导热能力的导热胶所产生的效果。在目前很多的应用里面,要实现这种采用一个顶部平面的均匀散热,最有效的方式就是用一层能够适应公差的导热胶+隔离片,让所有并排摆放的顶部散热芯片的热量能够均匀地传导到一个平面的散热片上,这是目前业界共同接受的方法。而如果只需要对单独一个顶部散热芯片进行散热,则可以采用锁螺丝、铜夹子甚至焊接等多种选择。但是从加工的速度、制造的成本上来看,这种方法是最行之有效的。”程文涛解释说。

三是需要做更多的验证。因为顶部散热芯片,一般是不会用螺丝进行固定的,而是使用一块很大面积的平板散热片与底层大面积的PCB板中间搭载多颗芯片。那么,这种情形下,它的抗震等级可不可靠,EMI问题严不严重等很多方面的相关问题,在推行之初,需要厂商做很多的实验去验证目前采用的方案是否可行。

当然,虽然问题很多,但程文涛感到欣慰的是,现在越来越多的厂商看到了TSC封装的优势,大家都进行了良性的互动,“尽管挑战是多方面的,但随着产业链上下游共同分工配合,困难就会快速高效的被解决。”

结语

TSC封装最为适合数据中心、通信基站、电动汽车等需要产品具有体积小、重量轻、功率密度高、效率高等特性的应用场景中。其实,在JEDEC标准里面,英飞凌不是唯一一家做顶部散热封装技术的公司,不同的企业提出的顶部散热封装技术设计方案都有他们自己的设计和考虑,最终哪一个封装会成为业界公认的标准,还需要看厂商对终端应用的理解,以及终端客户的接受程度。

-

英飞凌

+关注

关注

66文章

2175浏览量

138621 -

功率器件

+关注

关注

41文章

1758浏览量

90405

发布评论请先 登录

相关推荐

华润微持续发力MOSFET先进封装,三款顶部散热封装产品实现量产

TAS5630B器件顶部散热焊盘和散热器之间加导热绝缘垫,散热器需要接地吗?

SiC与GaN 功率器件中的离子注入技术挑战

碳化硅(SiC)功率器件核心优势及技术挑战

功率器件顶部散热封装技术的优势及普及挑战

功率器件顶部散热封装技术的优势及普及挑战

评论