使用 NoC 可以大大简化 SoC的开发,但这在很大程度上取决于谁在开发NoC。

作者:Michael Frank and Frank Schirrmeister

除了简易的产品以外,几乎所有的现代系统级芯片 (SoC) 设备都将利用片上网络(NoC) 来实现其片上通信。有些人质疑是否有必要使用 NoC,或者采用更基本的方法是否能足够满足需要。

Part.1

SoC中有什么?

SoC 是一种集成电路(IC),它集成了计算机或其他电子系统的大部分或全部组件。SoC 由称为知识产权(IP) 模块的多个功能单元组成。其中有许多模块将来自第三方供应商;剩下的部分- 那些提供“秘密武器”,将此SoC与竞争产品区分开来 - 将由自己内部开发创建。

这些 IP 模块可以包括处理器内核,如微处理器单元(MPU)、图形处理单元(GPU) 和神经处理单元(NPU)。除了各种类型的存储器 IP 外,其他 IP 模块还可以执行通信、实用程序、外设和加速功能。

Part.2

总线、Crossbar Switch和NoC

每个 IP 块都表示在系统内存空间中的某个位置。术语“事务”(transaction) 是指从系统内存空间的地址中写入或读取数据字节的操作。为了使SoC发挥其魔力,IP块需使用事务通过某种形式的互连来相互“交谈”。术语“启动器”(initiator) 和“目标”(target) 是指生成或响应事务的 IP 块。

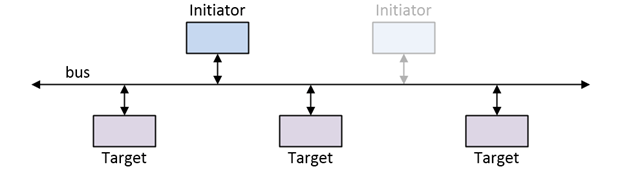

1990年代SoC上使用的主要互连机制是总线(bus)。高度简化的表示如图 1 所示。请注意,标记为“总线”的线路将包括多条实现数据总线、地址总线和相关控制信号的线路。

图 1:简化的总线互连结构

在许多早期的SoC设计中,只有一个中央处理器(CPU) 形式的启动器IP块。当启动器在地址总线上放置一个地址时,所有的目标 IP 块都会看到它,其中一个会对自己说:“这是我”。当启动器随后发出读取命令时,或者当它将数据放在数据总线上并发出写命令时,相应的目标将做出响应。

有一些早期的 SoC 可能会使用多个启动器。例如,CPU 可能附带直接内存访问 (DMA)功能,该功能可用于在不同内存区域和外围设备之间快速传输大型数据块。随着设计中启动器数量的增加,有必要实施某种形式的仲裁方案,允许它们协商总线的控制。

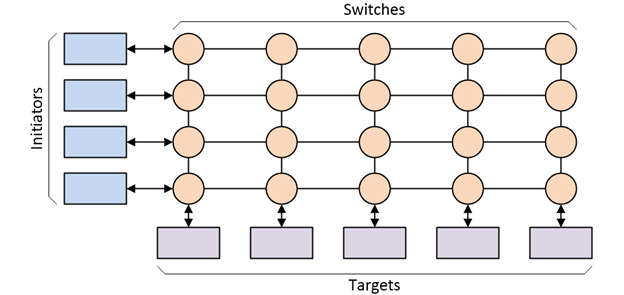

在 2000 年代初期,随着 SoC 设计变得越来越复杂(包含越来越多的 IP 模块并采用多个启动器),使用基于 crossbar switch交叉开关的互连架构变得很普遍(图2)。同样,此图中的每一条线代表一条包含数据、地址和控制信号的多线总线。

在 2000 年代初期,随着 SoC 设计变得越来越复杂(包含越来越多的 IP 模块并采用多个启动器),使用基于 crossbar switch交叉开关的互连架构变得很普遍(图2)。同样,此图中的每一条线代表一条包含数据、地址和控制信号的多线总线。

图2: 简化的crossbar switch互连架构

在这种情况下,任何启动器都可以与任何目标通信。当事务从启动器传递到目标并再次返回时,switch交叉开关对事务进行路由,并且多个事务可以随时在“进行中”。每个switch都具有缓冲事务的能力,因此如果许多事务同时到达,它可以决定哪个事务具有更高的优先级。

SoC 设计的规模和复杂性持续增长。大约在 1990 年代初期,SoC 可能只包含几十个 IP 模块,整个设备可能只包含 20,000 到 50,000 个逻辑门和寄存器。相比之下,如今,SoC 可以包含数百个 IP 模块,每个模块包含数十万甚至数百万个逻辑门和寄存器。

在同一时期,数据总线的宽度从8位增加到16位,32位,64位,甚至更高。事实上,目前数据传输的典型大小是 64 字节(512 位) 缓存行,这很快就会导致路由拥塞问题。尽管硅芯片工艺的发展已经使晶体管缩小了几个数量级,但由于芯片上导线的宽度没有以同样的速度减小,这些问题变得更加严重。

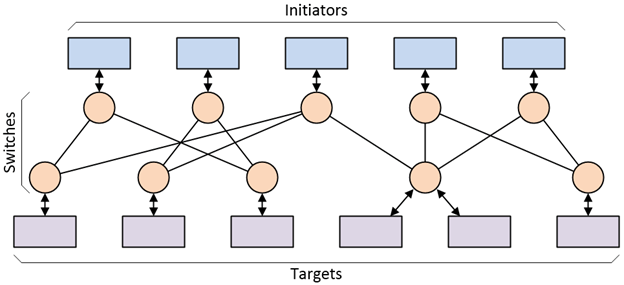

为了解决这些问题,今天的设计人员采用了片上网络(NoC) 的概念。图 3 是一个简单的 NoC 示例。在这种情况下,事务就由传递的信息包承担。每个数据包包含一个反映目标地址的标头和一个包含数据、指令、请求类型等的正文。

图3: 简化的片上网络(NoC)互连架构

多个信息包可以在任何特定时间“传输”,并且switch再次具有缓冲事务并确定事务优先级的能力。由于每个启动器不需要能够与每个目标通信,这可以反映在架构中,从而进一步降低了互连要求。

Part.3

使用成品还是“自己动手”?

从一个角度来看,使用 NoC很大程度上简化了 SoC 的设计,但这在很大程度上取决于谁在开发 NoC。术语“套接字”(socket) 是指IP块与NoC之间的物理接口(例如,数据宽度) 和通信协议。SoC行业已经定义并采用了几种socket协议(OCP,APB,AHB,AXI,STBus,DTL等)。

除了不同的数据宽度外,同一设计中的IP模块可能以不同的频率计时。由于 SoC 设计可能涉及数百个 IP 块,其中许多来自其他第三方供应商,因此 IP 可能使用不同的socket协议。为了适应这种多样性,可能需要在启动器和目标socket之间转换事务。

支持多个 SoC 项目的内部 NoC 需要多个维度的可配置性和灵活性。因此,从头开始开发 NoC 可能与设计 SoC 的其余部分一样复杂和耗时。此外,开发人员现在有两件事需要验证和调试 - NoC和设计的其余部分。

解决措施是使用现成的NoC解决方案,例如 Arteris的FlexNoC。在这种情况下,FlexNoC直观的界面使设计人员能够识别构成架构的IP模块以及每个模块的socket特性(宽度、协议、频率等)。开发人员还可以指定哪些启动器需要与哪些目标通信。此时,生成NoC实际上是一个“按钮”操作。

Part.4

SoC 到底有多复杂?

回到SoC设计何时需要片上网络的问题。直觉的答案可能是较小的设计可能被豁免。但是,在最近与Semico Research的Rich Wawrzyniak的讨论中,他证实我们已经在客户那里看到的情况是:即使在工业和物联网领域的较小设计中,用户也经常面临数十到数百个不得不组装和协调的IP块。

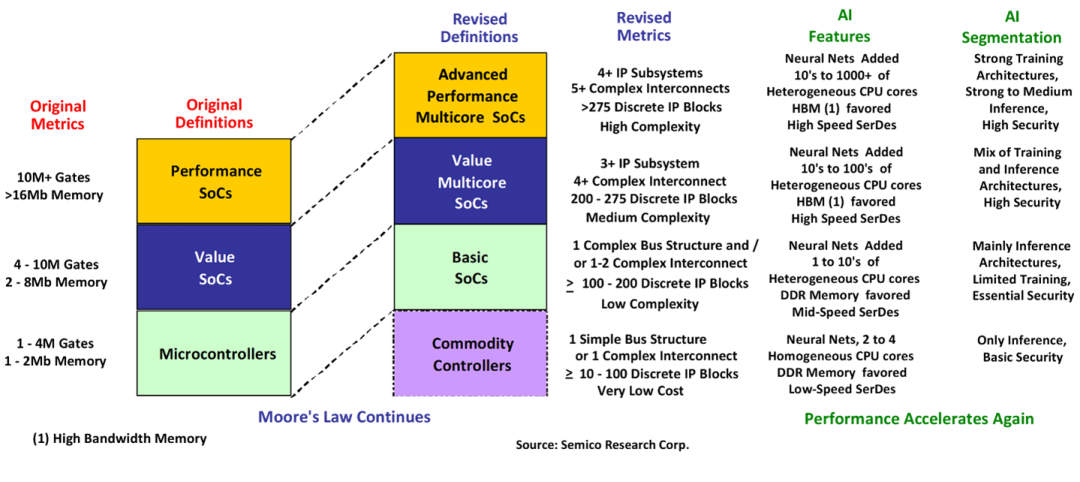

如图 4 所示,Semico 定义了四类 SoC。其中三种- 具有100-200个离散模块和1+互连的基本SoC,具有200-275个模块和4+复杂互连的特定价值多核SoC,以及具有>275模块和5+复杂互连的高性能SoC - 是NoC自动化的明确靶心目标。但是除此之外,即使是较简单的商用控制器,设计人员也要面临着10到100个需要交互的离散模块。

对于较小的设计,工程师倾向于“自己做NoC”。但通常情况下,他们很快就会意识到:他们应该打电话给Arteris来利用NoC自动化。

图4: Semico根据复杂性将SoC分为四类

+

结论

在本专栏的开头,提出了“我的SoC设计何时需要NoC?”的问题。简单的答案是,当今日益复杂的SoC设计始终需要一个NoC来优化实现出色路由和性能目标。实施前卫的NoC的简单方法是使用Arteris的FlexNoC 。

关于 Arteris

Arteris是系统IP的先进提供商,包括 片上网络(NoC) 互连 IP 和 IP 部署技术两部分,可加速各种电子产品的系统级芯片(SoC)半导体开发和集成。垂直应用包括汽车、移动、消费电子、企业数据中心、5G 通信、工业和物联网,利用 AI/ML 等技术和功能安全为宝马、博世、百度、 Mobileye、三星、东芝和恩智浦等客户提供服务。Arteris IP产品包括FlexNoC互连IP,Ncore缓存一致性IP,CodaCache独立末级缓存,ISO 26262 安全,人工智能,自动时序收敛和Magillem SoC 组装自动化。Arteris IP 产品可以帮助客户提升性能、降低功耗和面积、提高设计复用效率、加快 SoC 开发速度,从而降低开发和生产成本。

审核编辑 :李倩

-

模块

+关注

关注

7文章

2715浏览量

47521 -

soc

+关注

关注

38文章

4173浏览量

218381 -

启动器

+关注

关注

0文章

60浏览量

13173

原文标题:我的SoC设计何时需要NoC?

文章出处:【微信号:ArterisIP,微信公众号:ArterisIP】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

技术文章:如何利用NoC来进行FPGA内部逻辑的互连

利用NoC资源解决FPGA内部数据交换的瓶颈

如何利用NoC资源去支撑FPGA中的创新设计

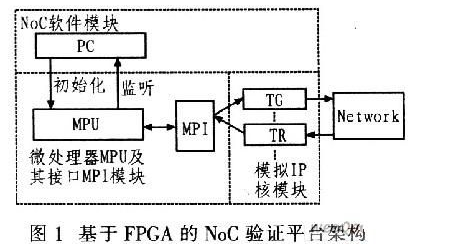

怎么构建一种基于FPGA的NoC验证平台?

采用FPGA的NoC验证平台实现方案

SoC中有什么?SoC到底有多复杂?

从SoC到NoC:芯片架构的演进与变革

AMD Versal系列FPGA NoC介绍及实战

传智驿芯联手Arteris,利用创新NoC技术驾驭复杂SoC设计

我的SoC设计何时需要NoC?

我的SoC设计何时需要NoC?

评论