我们在进行硬件设计时,时常会遭遇一些尴尬的事情,反复确认了电路图的设计完全正确,但是做出来的板子却无法正常工作。找来找去查不出问题,最终,我们会怀疑Layout设计是否出了问题,其中在Layout中最容易出现却很难确诊的问题是“ 地弹 ”的问题。

✦ 何为“地弹”?

举个例子:两个人相约下午两点在某地见面,两人都准时抵达了目的地但是没有成功接头。为什么?因为两个人所参考的时钟不一致,一个人参考的是北京时间,而另一个人参考的却是纽约时间。

此类问题在电路设计中就是“地弹”,“地弹”是指两个地平面(系统的参考平面)之间有电压差,当这个电压差足够大的时候,会导致系统的逻辑混乱。

**✦ **两步避免在BUCK电路中出现“地弹”

1) B****UCK电路的典型Layout设计建议

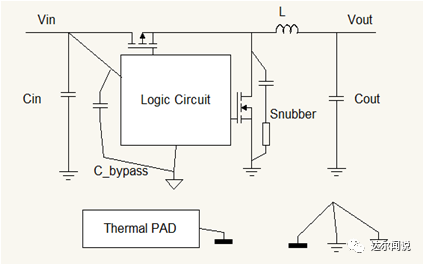

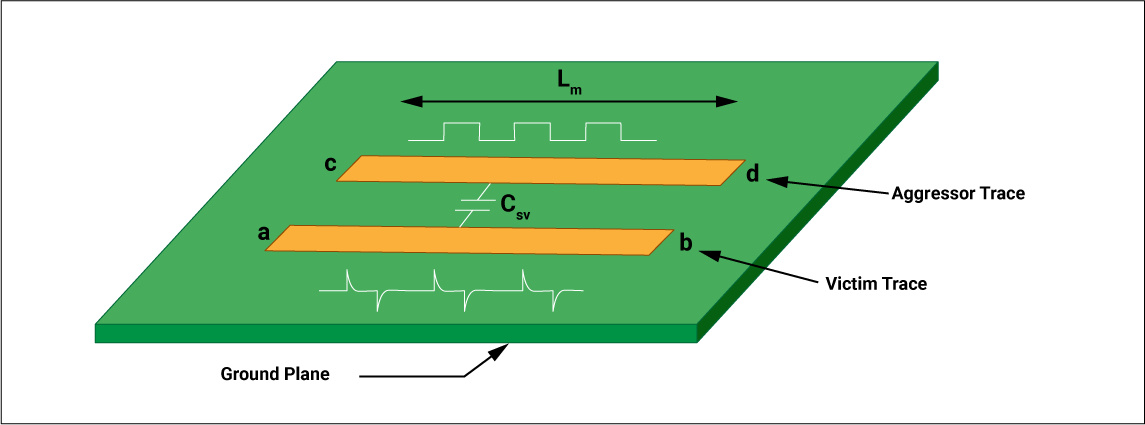

*图1 BUCK电路模型示意图

如图1所示,一个BUCK电路的最低配置是一套上下管(下管也可以是肖特基二极管),输出电感与电容,还有输入电容。

为了避免“地弹”,需要重视安装芯片的旁路电容并正确的Layout。旁路电路的作用是保障DC/DC控制器内部的逻辑电路正常工作。

注意:在某些场合,电路如果非常精简没有旁路电容,在Layout设计就需要将输入电容考虑进来,让其兼任旁路电容。

2)出现“地弹”的原因

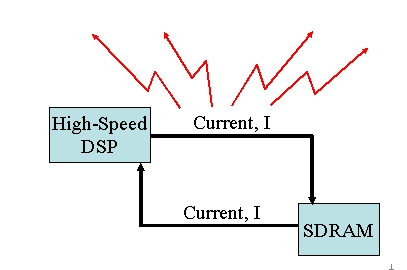

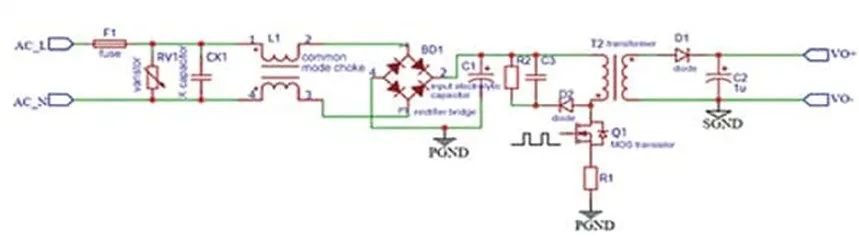

图2 关于地弹的一个实际案例

图2是一个实际的关于地弹的案例,在检查Layout设计时,不妨按照图中的思路手绘一个走线的示意图,然后再与图1的标准模型比对,很多问题可以在设计时被避免。

这个设计的主要问题是:

1)没有安装旁路电容;

2)在没有旁路电容的情况下,没有将输入电容Cin兼任旁路电容;

3)Snubber安装位置不正确,没有起到滤除噪音的作用;

4)输入电容的地平面与芯片的地平面之间路径不顺畅,两个地平面之间的阻抗经实测约0.2毫欧。

虽然看起来两个地平面之间的阻抗很小,但是经实测只要负载电流大于500mA,芯片立刻进入保护模式而关断。也就是说,虽然只有0.1毫伏(0.2mOhm*0.5A=0.1mV)的地弹也足以引起芯片内部逻辑错误。

当然,对地弹的忍受程度因芯片设计而异,但是尽量减小地弹是对Layout设计的基本要求。

-

电路设计

+关注

关注

6676文章

2453浏览量

204444 -

电压

+关注

关注

45文章

5607浏览量

115821 -

Layout

+关注

关注

14文章

405浏览量

61796

发布评论请先 登录

相关推荐

基于keras利用cv2自带两步检测法进行实时脸部表情检测

用labview调用teststand做并行测试,如何避免出现UUT information弹框?

用labview调用teststand做批量测试,如何避免出现UUT information弹框?并行测试可以解决

如何避免在PCB设计中出现电磁问题

自感电路中出现的过电压现象与电感电路教学

如何避免在DSP系统中出现噪声和EMI问题

如何避免在DSP系统中出现噪声和EMI问题

LTC1705:两步电压转换减小了笔记本电脑电源的尺寸和热量

两步避免在BUCK电路中出现“地弹”

两步避免在BUCK电路中出现“地弹”

评论