**1. Buck Layout注意事项

**

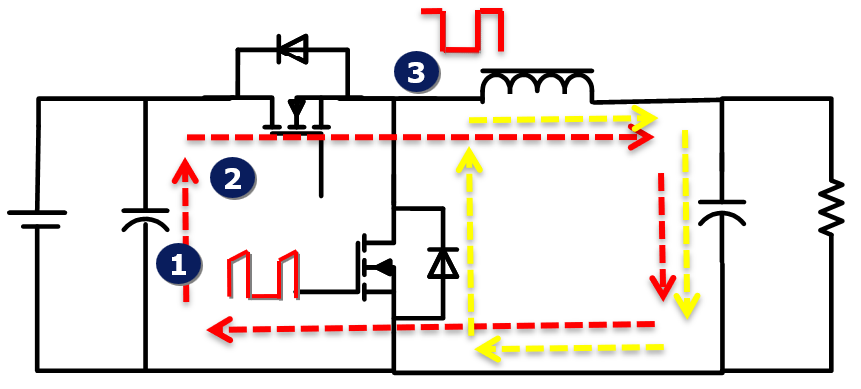

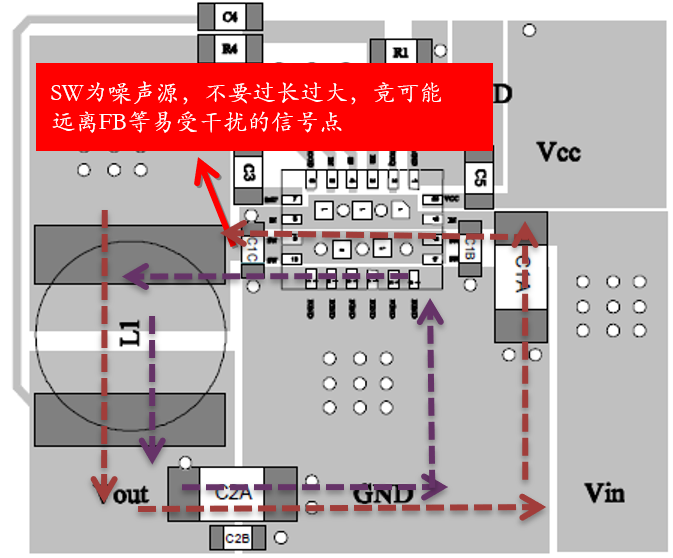

① 输入电容就近放在芯片的输入Vin和功率地PGND,减少寄生电感的存在,因为输入电流不连续,寄生电感引起的噪声对芯片的耐压以及逻辑单元造成不良影响;

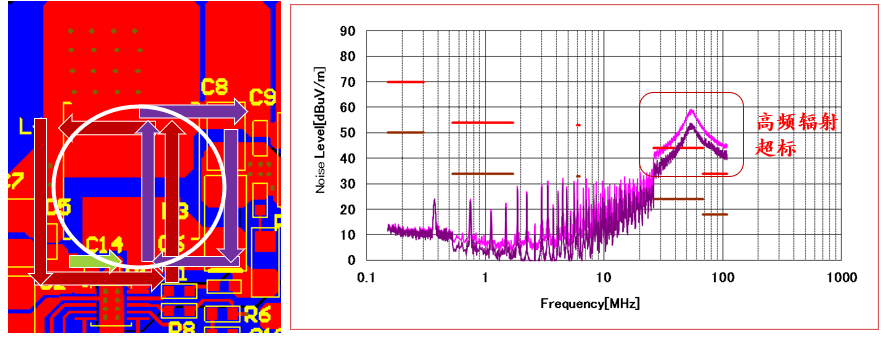

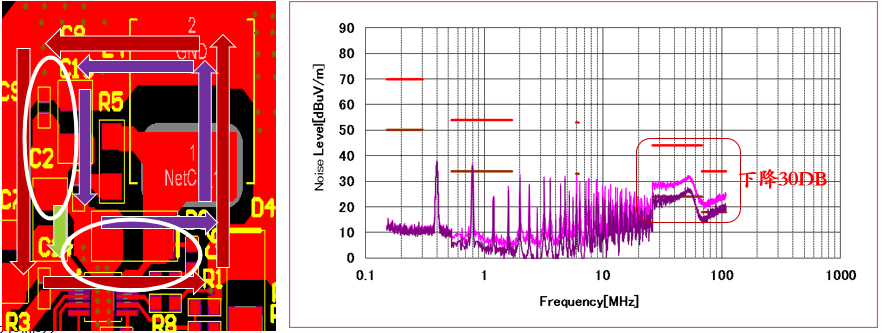

**② 功率回路尽可能的短粗,保持较小的环路面积,较少噪声的发射;

**

③ SW点是噪声源,保证电流的同时保持尽量小的面积,远离敏感的易受干扰的位置;

④ VCC电容应就近放置在芯片的VCC管脚和芯片的信号地之间,尽量在一层,没有过孔对于信号地(AGND)和功率地PGND在一个管脚的芯片,同样就近和该管脚连接;

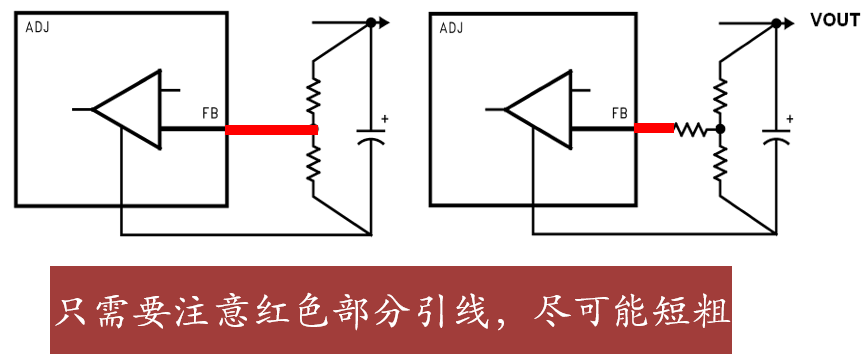

⑤ FB是芯片最敏感,最容易受干扰的部分,是引起系统不稳定的最常见原因。

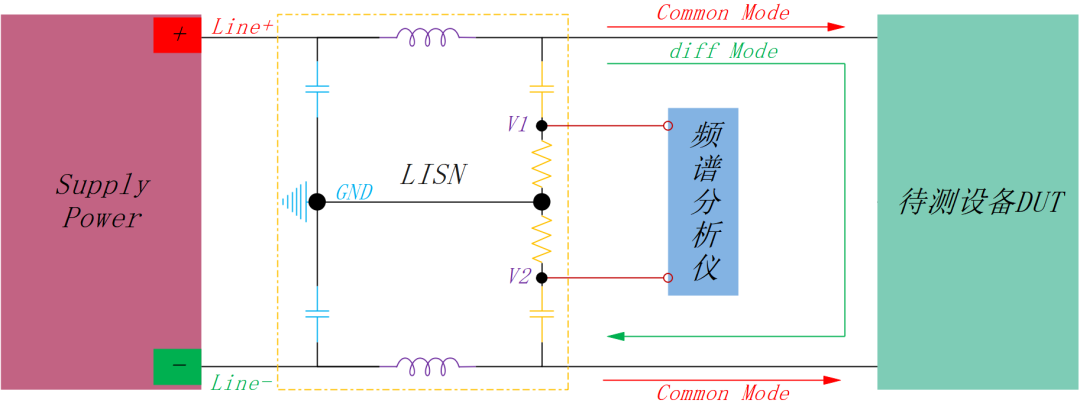

2. DCDC的噪声来源

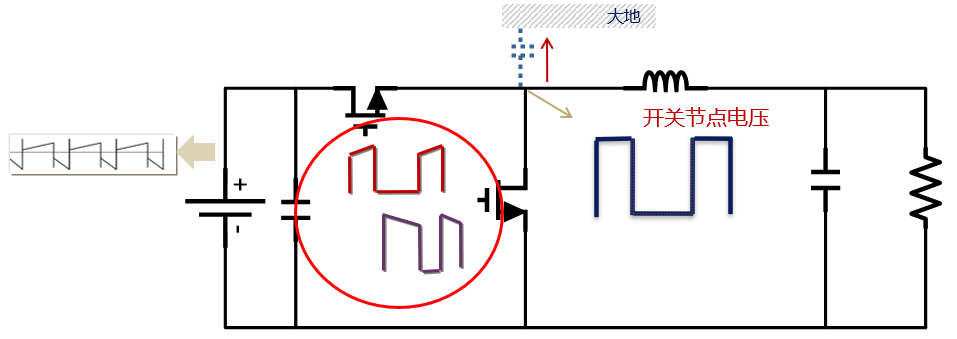

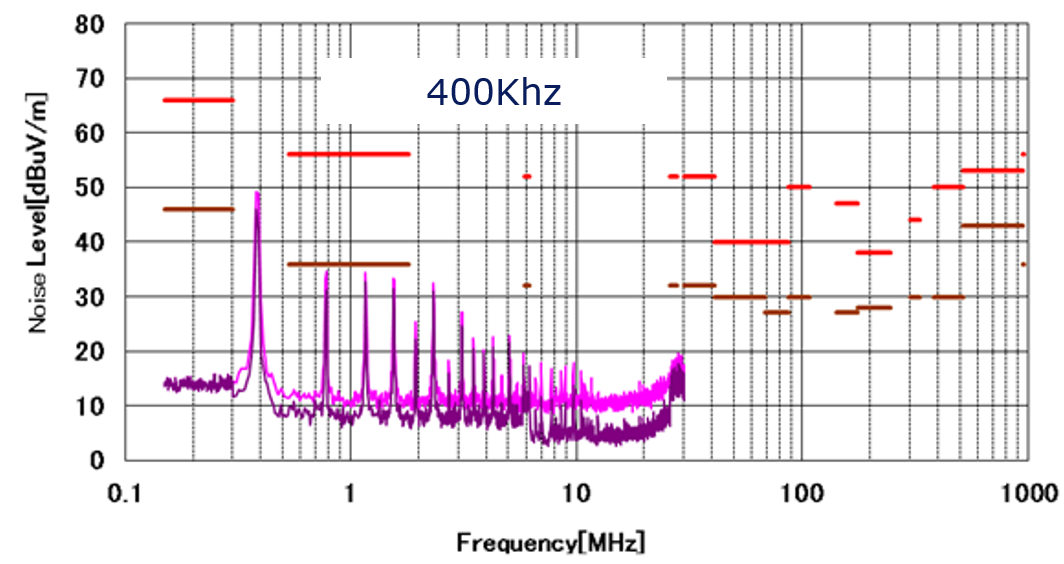

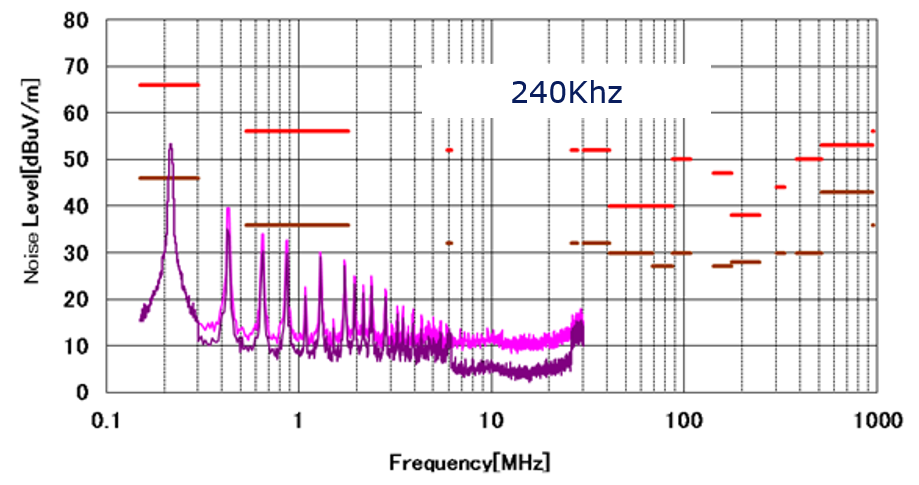

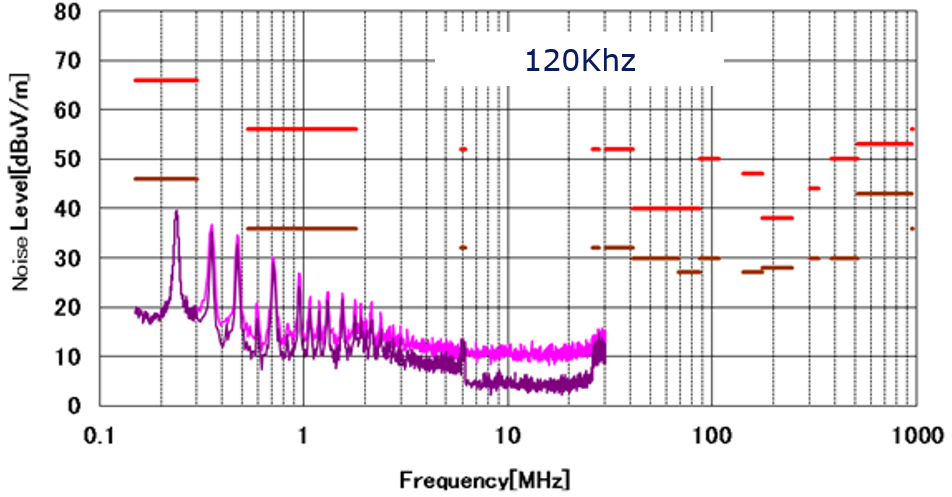

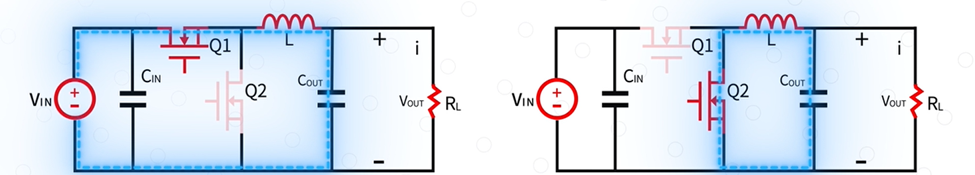

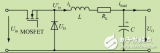

a. BUCK电路EMI的主要来源:高频电流环路和电压跳变

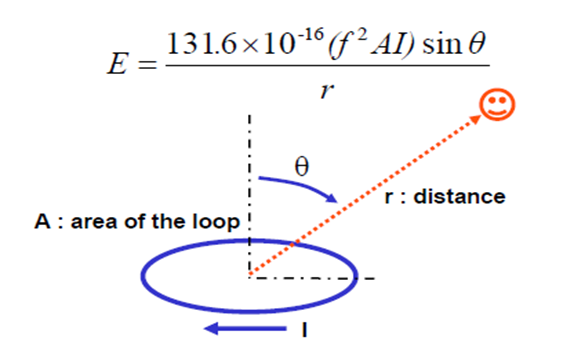

b. 环路天线原理:噪声分量和电流大小,环路面积和频率成正比,和距离成反比

3. DCDC的噪声抑制办法

a. 减慢开关速度,主要和上升时间Tr有关;

b. 减小高频环路面积,增加Vin和GND电容可以减少高频环路的电流;

c. 减小开关节点面积,降低容性耦合。

-

芯片

+关注

关注

455文章

50738浏览量

423297 -

信号

+关注

关注

11文章

2790浏览量

76736 -

管脚

+关注

关注

1文章

227浏览量

32026 -

Vcc

+关注

关注

2文章

305浏览量

35971

发布评论请先 登录

相关推荐

BUCK面临的挑战:EMI问题及对应的优化方案

pcb layout必须要了解EMI的三要素

Buck电路中PCB layout布局设计和注意事项

如何从EMI角度看PCB layout 法规

【技术探讨】BUCK电路设计技术要点

buck电路电感值如何选取

开源硬件-PMP11052.1-面向 Fly-buck 的 EMI 优化布局设计 PCB layout 设计

SPS Layout学习笔记

buck电路是什么意思_buck电路简介

如何在PCB的Layout阶段,充分应用改善技巧抑制EMI噪讯的强度

PCB印刷电路板的EMI噪讯设计

BUCK电路的EMI抑制方案

PMP30930.1-EMI 优化型降压 PCB layout 设计

Buck电路的Layout设计与EMI

Buck电路的Layout设计与EMI

评论