USB转串口:

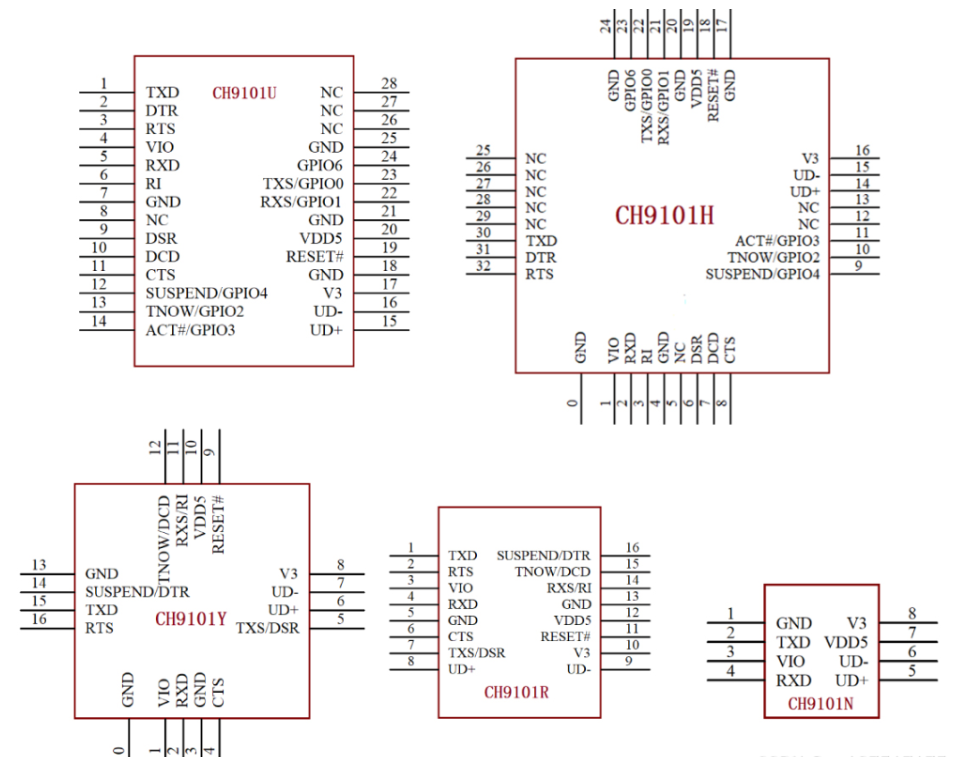

CH340C/N/K/E/B/G/T

CH341F/B/C/T/A

USB转打印口:

CH340H/S

CH341F/B/A

USB转I2C:CH341F/B/C/T/A

USB转SPI:CH341F/B/A/H

USB转并口/GPIO:CH341F/B/A

芯片供电注意事项

CH340/CH341等 USB 芯片都支持 5V 和 3.3V 电源电压,5V 供电时芯片 V3 引脚需要接一个 104 电容到地,3.3V 供电时需要注意以下几点:

★ 与 USB 芯片相连接的所有电路的电源电压都必须不高于 3.3V。

★ USB 芯片的 VCC 引脚与 V3 引脚必须短接,必须同时输入 3.3V 电源电压。

★ 如果使用 ESD 保护器件/瞬变电压抑制器件,那么其正电压应该是 3.3V。

芯片电平匹配问题

CH340/CH341 芯片支持 5V与 3.3V 供电,转换的接口为 TTL 电平,输出高电平与供电电压保持一致。因此在实际使用的时候,和相连的对端设备间要注意电压匹配的问题。

★ 与芯片相连的 IO 引脚电压不得超过芯片供电电压,否则可能会损坏芯片;

★ 在 5V 供电模式下,兼容 3.3V 系统,可以直接与 5V 或 3.3V 系统连接,与 1.8V 系统连接时需要外加电平转换电路;

★ 在 3.3V 供电模式下,可以与 3.3V 系统连接,与 1.8V 系统连接时需要外加电平转换电路;

★ 降压电路可以使用简单的电阻分压法,如串联1.6K与3.3K电阻可以得到接近3.3V电压;升压电路可以参考 boost 升压电路原理进行搭建;当然除了上面的方法,也可以直接采用升降压芯片;

防止电流倒灌问题

在串口应用中,当 CH340/CH341 与其他 IC 譬如 MCU 等芯片相互连接时,若有一方不需要供电工作时,要注意电流倒灌导致未供电的芯片开始工作或工作异常的情况,或者是通过串口下载程序时,MCU 需要复位以实现下载时,发现复位不成功,原因可能相同。解决办法:可在 CH340/CH341芯片的 发送引脚 TXD 上接一个反向二极管,然后再连接到对端 IC。在接收引脚上加一个限流电阻来防止对端 IC 对CH340/CH341倒灌电。

晶体以及电容的选用

对于 CH340/CH341系列需要外接晶振的芯片,在选用晶振时如果选择 12MHz 的石英晶体,那么旁路电容一般选择 33pF 的独石或高频瓷片电容。如果选用的低成本陶瓷晶体,那么旁路电路的容量必须用该晶体厂家的推荐值,一般情况下是 47pF。对起振困难或者起振不稳定的晶体可以适当调整旁路电容值进行测试。

芯片CH340的V3引脚作用

V3 的引脚除了在不同电压供电模式下接法不同,对于电容数值选用也是需要注意的。V3 引脚的电容用于内部电源节点退耦,来改善 USB 传输过程中的 EMI,通常容量在 4700pF 到 0.1uF 范围,建议容量为 0.1uF,即 104 电容。

如何提高工作稳定性和抗干扰能力

USB 信号属于模拟信号,所以在 CH340/CH341 等 USB 芯片内部包含数字电路和一些模拟电路,另外,USB 芯片中还包含时钟震荡及 PLL 倍频电路,电路的公共地端在芯片内部已经连接在一起并连接到芯片的 GND 引脚。

如果 USB 芯片有时工作不正常、或者 USB 数据传输随机性失败、或者抗干扰能力差,那么就应该考虑 USB 芯片是否稳定工作。影响 USB 芯片工作稳定性的几大因素及解决办法如下:

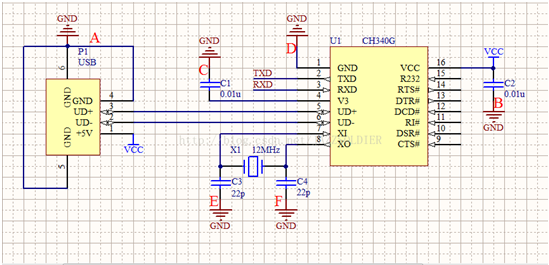

1. 时钟信号不稳定

时钟信号不稳定通常是 PCB 布线中 GND 走线不佳。参考下图,该图适用于 USB 类芯片,图中有 6个接地点,分别是 A、B、C、D、E、F,设计电路及 PCB 时应该尽量避免这 6 个 GND 点之间存在电压差(主要是指数字电路中的高频毛刺电压,也就是数字噪声)。

★ 尽量缩短这 6 个点之间的距离;

★ 类似模拟电路设计中的单点接地;

★ 大面积 GND 铺铜及 GND 多点过孔 VIA 降低高频信号阻抗。图中最关键的是 E 点、F 点与 D 点之间不能存在高频毛刺电压差,可以用示波器探头接 D 点测量时钟输入端 XI 引脚的 12MHz 时钟波形是否有抖动。

2. 时钟信号受干扰

★ PCB 设计时尽量不在晶体及震荡电容附近走线,尤其是不要走继电器、电动机等带有瞬时冲击电流的电源线和强信号线、时钟信号线、频率较高的开关信号线等;

★ 使晶振、外部电容与IC之间的信号线尽可能保持最短;

★ 在晶体及震荡电容周边布置 GND 铺铜屏蔽干扰;

★ 将晶体外壳接地(任何需要晶体工作的电路都可以这样设计);

★ 使用有源晶振等。

3. USB信号受干扰

★ USB 信号线 D+ 与 D- 尽量对称平行布线,保证两根差分线紧耦合,避免 90度走线,弧形或45度走线均可;

★ 在元件布局时,尽量使差分线路最短,布线优先绘制差分线,一对差分线上尽量不要超过两对过孔,且过孔需对称放置;

★ 最好在两侧布置 GND 铺铜,减少干扰,在空间允许情况下,其他信号网络及地离差分线的间距至少 20mil,距离过近会对差分线阻抗产生影响;

★ 可以在 USB 信号线 D+ 和 D- 上串接共模电感以抑制EMI;

★ USB 外壳地串接一个 100K 到 1M 级的电阻到地,同时电阻上并联一个0.01uF电容;

★ 使用符合 USB 规范的带屏蔽层的传输线,不能使用普通排线或者非 USB 线缆。

除以上几种原因与解决方法外,还可以通过使用屏蔽罩在复杂应用环境中减小EMI干扰。

接入主机无反应或者出现无法识别的USB设备

★ 首先需要检查芯片供电是否正常,3.3V和5V供电注意事项参考上面说明;

★ 查看芯片是否为内置晶振版本,若为外置晶振版本,用示波器测量晶振是否起振,晶振与旁路电容参数是否匹配;

★ 检查电路原理图设计是否正确无误且满足规范;

★ 检查使用的线缆是否符合 USB 规范,线缆是否过长以及有无屏蔽层;

★ 检查电路板是否存在焊接问题,导致局部电路短路;

★ 控制芯片焊接最高温度与持续时间,务必控制低于 300 摄氏度且高温持续时间低于 2 分钟;

Windows 设备管理器出现感叹号设备

设备管理器出现感叹号设备说明硬件已经被系统枚举到了,但是驱动未安装或者驱动不匹配,此时需要做以下操作:

★ 从官网上下载最新的芯片驱动,链接地址为:http://www.wch.cn/download/CH341SER_EXE.html,安装时先点击卸载将可能存在的老版本驱动卸载删除,之后再点击安装新驱动;

★ 如果使用新驱动后问题仍然无法解决,那么查看系统驱动安装日志查看具体报错原因。日志系统路径为:C:Windowsinfsetupapi.dev.log。打开日志,查找CH341 字样可以看到失败原因,之后再进行对应问题的解决;

不同系统下面如何使用和判断设备是否正常工作

在不同的系统环境下要分别使用相应的芯片驱动,所有驱动可以从官网搜索下载到

★ Linux 系统下面使用首先需要确保系统中没有老驱动存在,系统的默认驱动目录为:/lib/modules/$(uname -r)/kernel/drivers,老驱动完整路径为 /lib/modules/$(uname -r)/kernel/drivers/usb/serial/ch341.ko。如果存在该文件,那么需要手动删除。之后编译下载的 Linux 驱动源码,将生成的新驱动文件 ch34x.ko 拷贝到原驱动路径下,然后执行 depmod 重启即可。插入设备后,可以通过 dmesg 查看设备是否枚举成功,以及驱动加载是否正常,成功会在 /dev 路径下产生 ttyUSB 开头的设备文件。

★ Android 系统下直接使用免驱APP就可以了,官网提供了芯片操作库以及 demo 工程源码方便二次开发,设备连接 Android 设备时,要使用 OTG 线并确保 Android 系统的 host 权限已经打开;

★ MacOS 下使用时首先要从官网下载最新芯片驱动,在系统上双击安装。当设备插入后,如果在系统 /dev 路径下产生 /dev/tty.wchusbserial 关键字说明设备正常工作;

Windows 系统下如何确定 COM 口为 CH340/CH341 设备

★ 使用软件查询法,依次打开系统的 COM 口,并以 300bps 向 COM 口发送特殊字符串 "$CH341Ser?",如果回复字符 'W'那么表明为 CH340/CH341 设备;

★ 使用CH341PT.DLL动态库,应用程序可以直接调用DLL中相应的API识别 CH340/CH341 串口,识别速度快,效率高。注意,CH341PT.DLL在INF中定义为可选安装,默认是安装的;

串口通讯乱码

如果 CH340/CH341 在与其他器件进行串口通讯时出现乱码,首先需要确保双方串口设置完全相同,包括波特率、数据位、停止位、校验位等。其次需要明确双方收发误差率允许范围以及实际通讯时波特率误差。CH340/CH341 串口接收信号的允许波特率误差不小于 2%,CH340G/CH340T/CH340R 串口发送信号的波特率误差小于 0.3%,CH340C/CH340E/CH340B 小于 1%,明确范围后测量实际通讯波特率误差是否满足此条件。另外需要注意,如果实际通讯模型是 TTL 转 RS232 通讯,那么需要测量最终通讯接口误差,因为信号经过电平转换芯片后误差会放大。

审核编辑黄宇

-

芯片

+关注

关注

459文章

51659浏览量

430423 -

usb

+关注

关注

60文章

8044浏览量

267847 -

串口

+关注

关注

14文章

1574浏览量

77833

发布评论请先 登录

相关推荐

国产芯片解析:无线充电管理芯片CH246跟CH247对比详细

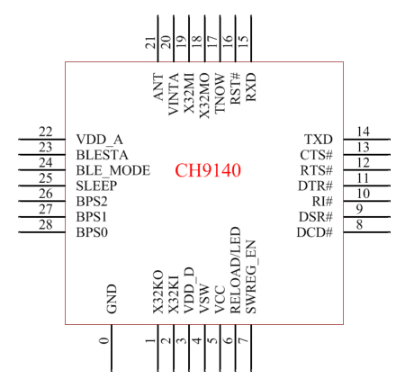

沁恒微蓝牙转接芯片系列解析:CH9140/CH9141/CH9142/CH9143

USB转串口芯片CH340与CH341使用问题汇总

USB转串口芯片CH340与CH341使用问题汇总

评论