大多数关于高级光刻的讨论都集中在三个要素上——曝光系统、光掩模和光刻胶——但这只是挑战的一部分。

将图案从光掩模成功转移到晶圆上的物理结构还取决于多种薄膜的协同工作,包括底层、显影剂和各种表面处理。事实上,该工艺的大部分灵活性和适应性都来自于这些辅助材料,三星电子首席工程师 Hyungju Ryu 在最近的 SPIE 高级光刻和图形会议上的演讲中说。

光刻是最复杂的开发过程,曝光系统的开发和采购需要数年时间。因此,一旦设计在工厂内投入生产,对光掩模的更改是不受欢迎的。因此,针对实际条件优化图案转移通常落在光刻胶和蚀刻工艺上。

底层使晶圆表面正常化

在第一层之后的任何层中,器件晶圆都呈现出不均匀的表面。与硅和金属交织的氧化物图案会导致表面能和润湿性发生变化,并且先前的表面处理会导致粗糙度。

底层涂层有助于平滑这种特征粗糙度并改善曝光结果。他们通过使表面能正常化、促进光刻胶粘附并降低图案坍塌的风险来做到这一点。

当需要薄光刻胶时,例如在高数值孔径 EUV 中,光刻胶层本身可能无法捕获足够的曝光剂量。致密的底层可以帮助抵抗光致产酸剂 (PAG) 扩散,确保光致产酸剂分子保持在光刻胶保护基团附近。不幸的是,EUV 光子具有如此高的能量,以至于它们与薄光刻胶的反应可以从底层以及光刻胶本身激发二次电子。在金属氧化物光刻胶中,应用材料公司的研究人员表明,这些二次电子可以改善交联,确保整个光刻胶层不溶于显影剂。

imec 研究员 Mihir Gupta 指出,底层设计涉及在蚀刻选择性和抗腐蚀之间取得平衡。蚀刻选择性是两种材料之间蚀刻速率的差异。它部分取决于材料和蚀刻等离子体之间的相互作用。这些材料的差异越大,就越容易确定将蚀刻其中一种而不蚀刻另一种的工艺条件。

致密的底层可以通过提供与光刻胶的强烈对比来提高选择性。同时,总蚀刻时间也是影响光刻胶侵蚀的一个重要因素。致密的底层蚀刻更慢,增加了光刻胶对蚀刻化学物质的暴露。随着光刻胶厚度的下降,平衡这两个因素变得更具挑战性。

晶圆厂通常使用光刻胶来图案化抗蚀刻硬掩模,然后依靠硬掩模来保护晶圆。但是,如果光刻胶太薄,它可能会在第一个转移步骤完成之前被侵蚀掉。随着光刻胶厚度的减小,底层厚度也应该减小。

不幸的是,正如 Brewer Science 高级研究员 Si Li 及其同事所表明的那样,随着厚度的下降,传统的旋涂层可能无法形成均匀的涂层。相反,Brewer Science 工程师展示了一种小分子“旋涂底漆”材料,能够获得比传统聚合物更薄的层。

Nissan Chemical 的研究员 Wataru Shibayama 及其同事通过首先旋涂底漆层,然后用溶剂冲洗,获得了类似的结果。该团队随后将结果与原子层沉积中的吹扫循环进行了比较。溶剂冲洗去除未反应的底漆,留下均匀的薄层 (10Å)。

并非所有缺陷都打印出来:面漆和显影剂如前所述,光刻胶捕获的图像包含一定程度的随机缺陷。这是由光子和化学散粒噪声引起的,但这并不是故事的结局,因为并非光刻胶捕获的所有缺陷都会打印在晶圆上。即使在曝光之后,也有很多机会可以改善最终印刷图案。例如,杜邦电子技术经理侯希森及其同事指出,ArF 和 KrF 光刻工艺经常在曝光后和曝光后烘烤前使用面漆,通过使缺陷和侧壁更易溶于显影剂来化学“修剪”光刻胶图案.

修剪效果的强度是可调的。它可以简单地降低桥接缺陷的可能性,或者可以调整整体临界尺寸 (CD)。在 EUV 曝光测试中,杜邦团队能够将所需剂量减少 24%,但仍能达到相同的分辨率。

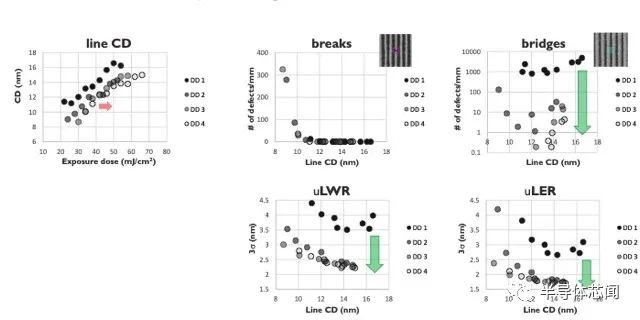

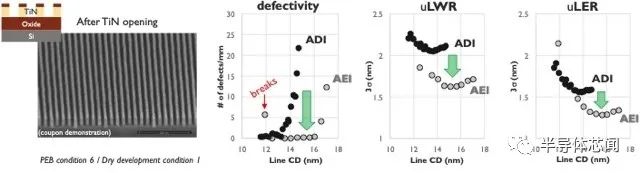

干法光刻胶和干法显影工艺允许调整光刻胶和显影参数作为工艺配方的一部分。imec 研发团队负责人 Hyo Seon Suh 解释说,更积极的开发过程可以平滑线边缘并消除一些桥接缺陷。同时,更激进的过程可能使换行更有可能发生。通常,蚀刻后无故障窗口以比光刻后窗口更大的 CD 为中心。

图 1:(显影)优化干式显影参数可改善粗糙度和桥接缺陷,同时适度增加剂量与尺寸比。

图 2:(蚀刻)相对于开发后检查 (ADI),蚀刻后检查 (AEI) 随着整体 CD 的增加发现更少的缺陷和更小的粗糙度

相比之下,Inpria 的金属氧化物抗蚀剂依赖于基于湿轨的开发过程。在他们的抗蚀剂中,保护性配体围绕着金属氧化物核心。通过共同优化抗蚀剂和显影化学物质,晶圆厂可以根据自己的要求调整分辨率/线宽/剂量权衡。

根据 TEL 研究员 Cong Que Dinh 的说法,要考虑的关键参数是 m,即抗蚀剂中溶解抑制剂的浓度。m随深度 ( dm/dx )的变化是完全或不完全曝光的量度。标准偏差σ m是抗蚀剂偏析和化学散粒噪声的其他影响因素的量度。

一般来说,减少曝光剂量会增加 dm/dx。抗蚀剂的表面可能是完全可溶的,但不完全的显影会导致通孔底部出现浮渣,抗蚀剂特征底部出现浮渣。减小σ m有助于提高对比度和锐化特征边缘。在 TEL 的 ESPERT 工艺中,显影剂化学物质通过改变曝光的抗蚀剂表面的极性以促进溶解来降低σ m 。TEL 小组能够解决通过干涉光刻印刷的 8 纳米半间距特征。在 10nm 半间距处,通过优化显影化学,灵敏度提高了 30%,线宽粗糙度降低了 21%。

随着工艺的发展,imec 的 Hyo Seon Suh 表示,曝光工具可实现的绝对分辨率是第一步,其次是能够在晶圆上实现该分辨率的蚀刻系统。但要在生产设计中真正实现这些功能,底层、开发人员和流程中其他鲜为人知的元素发挥着关键作用。

审核编辑 :李倩

-

晶圆厂

+关注

关注

7文章

633浏览量

38057 -

光刻

+关注

关注

8文章

330浏览量

30321 -

EUV

+关注

关注

8文章

609浏览量

86332

原文标题:EUV光刻的无名英雄

文章出处:【微信号:光刻人的世界,微信公众号:光刻人的世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

纳米压印光刻技术旨在与极紫外光刻(EUV)竞争

日本首台EUV光刻机就位

Prolith和HyperLith主要用于mask-in-stepper lithography仿真、光刻设计

结构化布线在AI数据中心的关键作用

美投资8.25亿美元建设NSTC关键设施,重点发展EUV光刻技术

日本与英特尔合建半导体研发中心,将配备EUV光刻机

日本大学研发出新极紫外(EUV)光刻技术

日企大力投资光刻胶等关键EUV材料

Rapidus对首代工艺中0.33NA EUV解决方案表示满意,未采用高NA EUV光刻机

ASML考虑推出通用EUV光刻平台

台积电A16制程采用EUV光刻机,2026年下半年量产

英特尔率先推出业界高数值孔径 EUV 光刻系统

英特尔突破技术壁垒:首台商用High NA EUV光刻机成功组装

ASML 首台新款 EUV 光刻机 Twinscan NXE:3800E 完成安装

EUV光刻的无名英雄

EUV光刻的无名英雄

评论