一、MOSFET功耗

Buck电路的损耗,主要发生在功率路径上,也就是较大电流通过的器件上:MOSFET、电感、二极管(非同步控制器)。

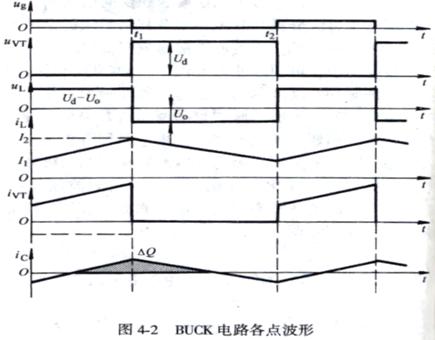

根据Buck电路的几个工作阶段,我们分别讨论MOSFET的损耗

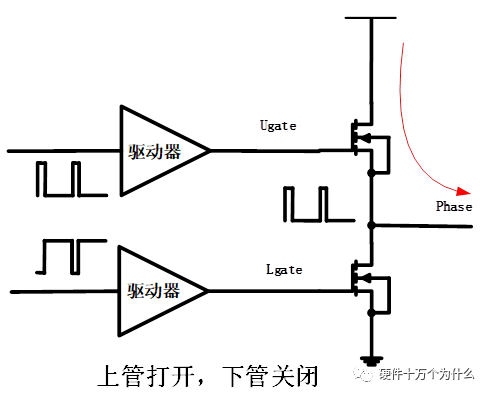

第一个阶段:上管打开的过程:

在开关过程中产生的损耗,MOSFET处于放大区,下管关闭几乎没有电流。

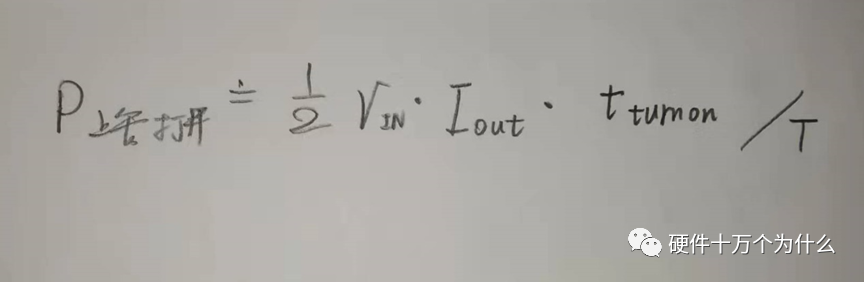

在上管打开过程中,上管的电压Vds不断减小,电流Ids不断增加。我们简单地可以认为是线性增减。此时输出电流处于谷底,最小值。如果近似的看成是电流平均值即输出电流值,则可以简单计算如下:

如果需要考虑电流纹波,则计算公式如下:

第二个阶段:上管完全导通、下管关闭。

上管MOSFET处于打开状态,上MOSFET等效于一个电阻即为MOSFET的导通阻抗Rds(on),Rds(on)上面流经电流的损耗。此时,下管没有电流,功耗全部集中在上管上。

打开的时间是由占空比决定的:上管打开的时间约等于T*D。

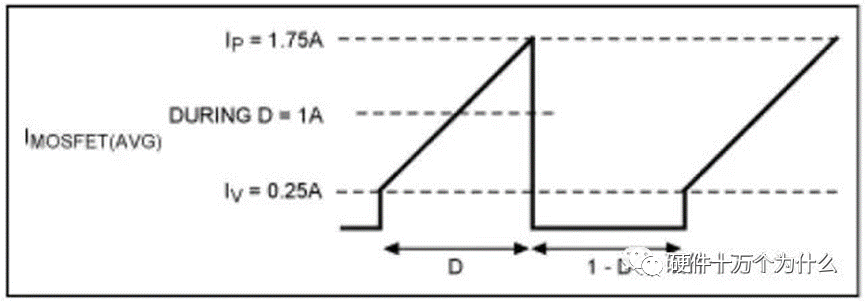

电流近似计算时,可以看作就是Buck电源的输出电流。如果细算起来,就需要考虑在上管打开过程中,电流是逐步变大的,我们需要对这个电流增大的过程进行积分计算,考虑到电流逐步变大的过程。

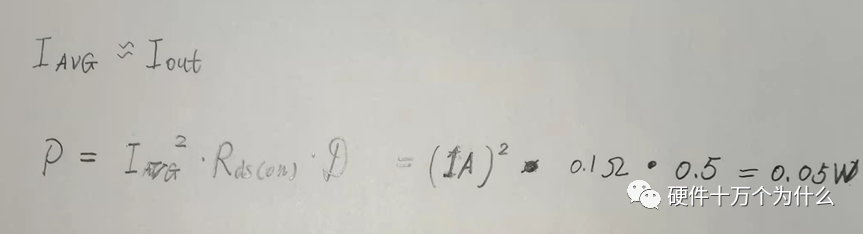

如果电流纹波足够小,我们可以近似认为上管打开过程电流没变化。则这个计算非常容易,就是直接计算,就可以:

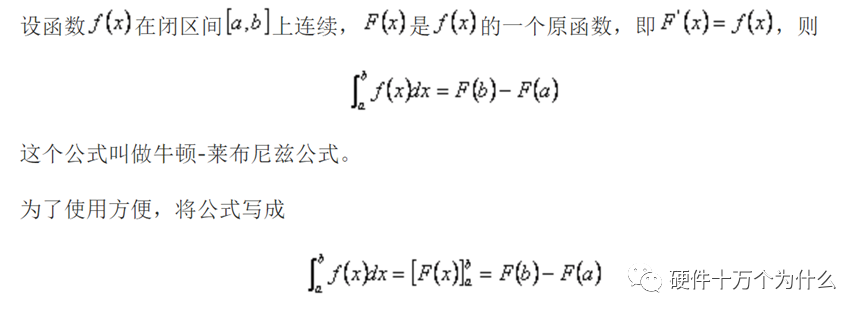

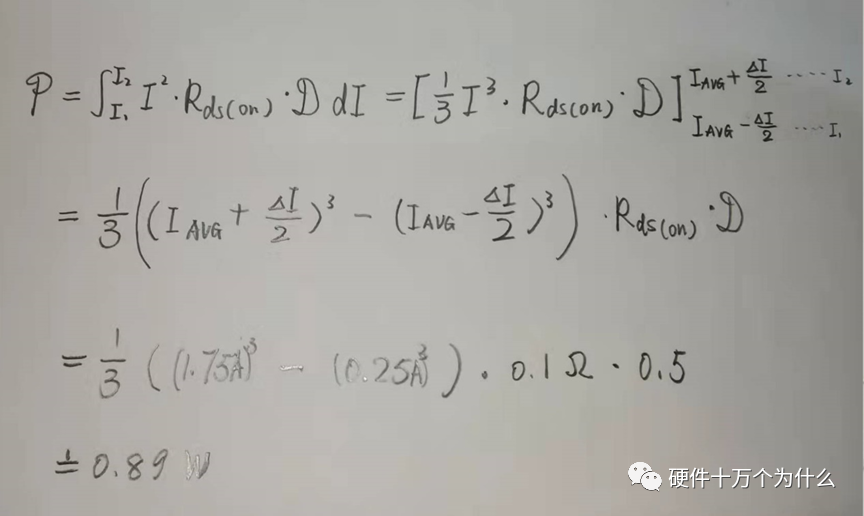

如果纹波带来的影响不可忽略,则我们需要进行积分运算。我们从开始开启的电流进行积分,即最小电流处,积分到最大电流处。此处运用牛顿-莱布尼兹公式,计算定积分。

第三个阶段,上管关闭的过程

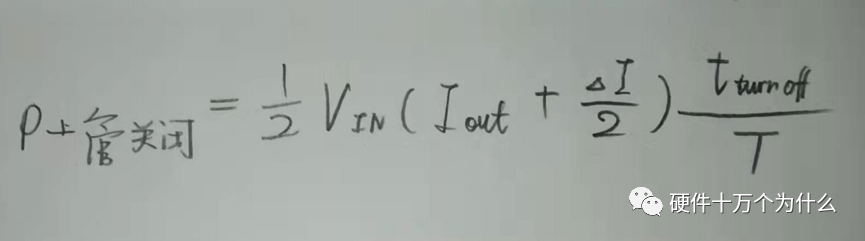

上管打开的过程和关闭的过程是类似的计算方法,此处只是电流为整个周期的最大值,因为经历了一个充电的过程,电流此时处于峰值。另外就是上管关闭的时间,会与上管打开的时间不一样。我们计算公式如下:

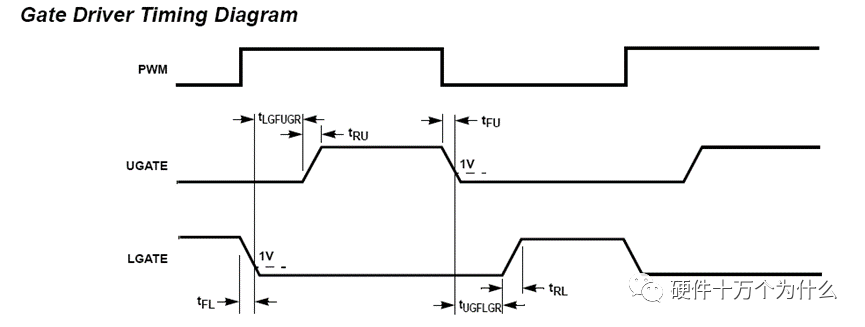

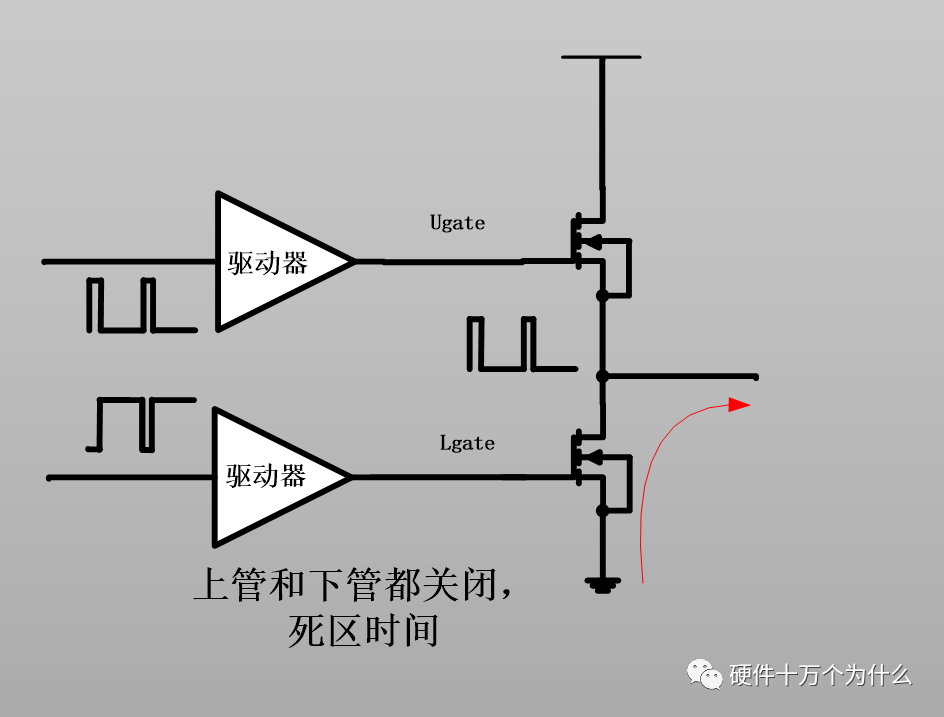

第四个阶段,此时上管已经完全关闭,下管暂时还没有打开,称为死区时间

我们需要理解,任何控制器都需要控制避免上下管同时打开,如果出现这个状态,则非常可能烧管,因为相当于通过上下管把输入电源和GND进行了短路。

为了避免这种状态,只好在上管关闭之后,等待一个时间段,再对下管进行打开的操作。而在两个MOSFET都关闭的状态,我们就称为死区时间。这个时间,主要依赖下管的寄生二极管进行续流,实现输出电流的一个回路。

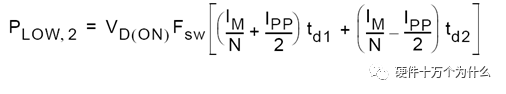

此时的功耗,就是下管的寄生二极管的功耗,也就是二极管的正向导通压降乘以此时的电流。在开关开关的过程中,会有两个阶段经历死区时间,所以下管的死区时间功耗计算公式如下:

第五阶段,下管导通

导通功耗,因为很显然下管的功耗是在电流通过MOS的DS沟道之间的电阻(rDS(ON))产生的。下面公式可估算下MOS管的导通功耗。

下管的导通损耗,近似的可以看作是:

如果考虑纹波,可以用以下公式进行计算:

1) 占空比 (高侧FET,上管) = Vout/(Vin*效率)

2) 占空比 (低侧FET,下管) = 1 – DC (高侧FET)

FET 可能会集成到与控制器一样的同一块芯片中,从而实现一种最为简单的解决方案。但是,为了提供高电流能力及(或)达到更高效率,FET 需要始终为控制器的外部元件。这样便可以实现最大散热能力,因为它让FET物理隔离于控制器,并且拥有最大的 FET 选择灵活性。它的缺点是 FET 选择过程更加复杂,原因是要考虑的因素有很多。

一个常见问题是“为什么不让这种 10A FET 也用于我的 10A 设计呢?”答案是这种 10A 额定电流并非适用于所有设计。

选择 FET 时需要考虑的因素包括额定电压、环境温度、开关频率、控制器驱动能力和散热组件面积 。关键问题是,如果功耗过高且散热不足,则 FET 可能会过热起火。我们可以利用封装/散热组件 ThetaJA 或者热敏电阻、FET 功耗和环境温度估算某个 FET 的结温,具体方法如下:

3) Tj = ThetaJA * FET 功耗(PdissFET) + 环境温度(Tambient)

它要求计算 FET 的功耗。这种功耗可以分成两个主要部分:AC 和 DC 损耗。这些损耗可以通过下列方程式计算得到:

4) AC损耗: AC 功耗(PswAC) = ½ * Vds * Ids * (trise + tfall)/Tsw

其中,Vds 为高侧 FET 的输入电压,Ids 为负载电流,trise 和 tfall 为 FET 的升时间和降时间,而Tsw 为控制器的开关时间(1/开关频率)。

5) DC 损耗: PswDC = RdsOn * Iout * Iout * 占空比

其中,RdsOn 为 FET 的导通电阻,而 Iout 为降压拓扑的负载电流。

其他损耗形成的原因还包括输出寄生电容、门损耗,以及低侧 FET 空载时间期间导电带来的体二极管损耗,但在本文中我们将主要讨论 AC 和 DC 损耗。

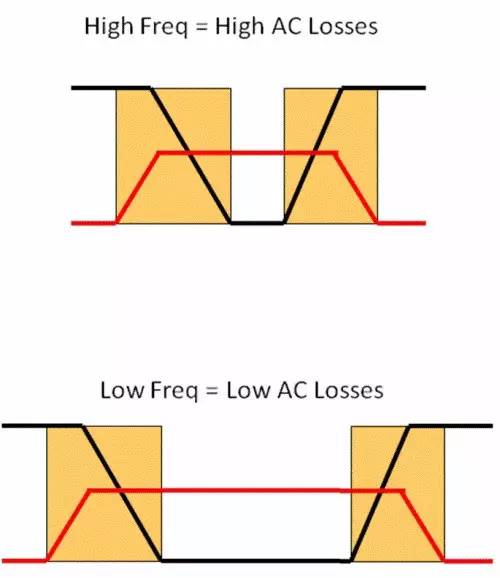

开关电压和电流均为非零时,AC 开关损耗出现在开关导通和关断之间的过渡期间。图 2 中高亮部分显示了这种情况。根据方程式 4),降低这种损耗的一种方法是缩短开关的升时间和降时间。通过选择一个更低栅极电荷的 FET,可以达到这个目标。另一个因素是开关频率。开关频率越高,升降过渡区域所花费的开关时间百分比就越大。因此,更高频率就意味着更大的AC开关损耗。所以,降低 AC 损耗的另一种方法便是降低开关频率,但这要求更大且通常也更昂贵的电感来确保峰值开关电流不超出规范。

AC 损耗图

开关频率对 AC 损耗的影响

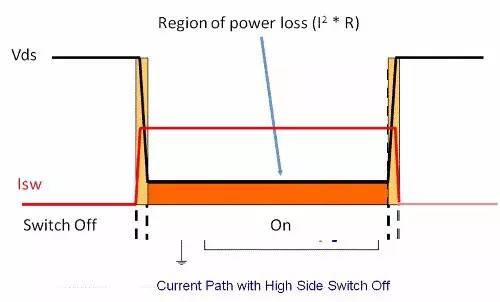

开关处在导通状态下出现 DC 损耗,其原因是 FET 的导通电阻。这是一种十分简单的 I2R 损耗形成机制。但是,导通电阻会随 FET 结温而变化,这便使得这种情况更加复杂。所以,使用方程式 3)、4)和 5)准确计算导通电阻时,就必须使用迭代方法,并要考虑到 FET 的温升。降低 DC 损耗最简单的一种方法是选择一个低导通电阻的 FET。另外,DC 损耗大小同FET 的百分比导通时间成正比例关系,其为高侧 FET控制器占空比加上 1 减去低侧 FET 占空比,如前所述。 我们可以知道,更长的导通时间就意味着更大的DC 开关损耗,因此,可以通过减小导通时间/FET 占空比来降低 DC 损耗。例如,如果使用了一个中间 DC 电压轨,并且可以修改输入电压的情况下,设计人员或许就可以修改占空比。

DC 损耗图

占空比对 DC 损耗的影响

尽管选择一个低栅极电荷和低导通电阻的 FET 是一种简单的解决方案,但是需要在这两种参数之间做一些折中和平衡。低栅极电荷通常意味着更小的栅极面积/更少的并联晶体管,以及由此带来的高导通电阻。另一方面,使用更大/更多并联晶体管一般会导致低导通电阻,从而产生更多的栅极电荷。这意味着,FET 选择必须平衡这两种相互冲突的规范。另外,还必须考虑成本因素。

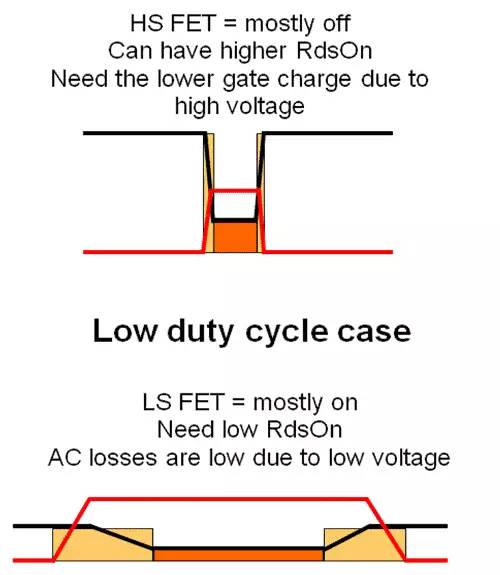

低占空比设计意味着高输入电压,对这些设计而言,高侧 FET 大多时候均为关断,因此 DC 损耗较低。但是,高 FET 电压带来高 AC 损耗,所以可以选择低栅极电荷的 FET,即使导通电阻较高。低侧 FET 大多数时候均为导通状态,但是 AC 损耗却最小。这是因为,导通/关断期间低侧 FET 的电压因 FET 体二极管而非常的低。因此,需要选择一个低导通电阻的 FET,并且栅极电荷可以很高。

低占空比设计的高侧和低侧 FET 功耗

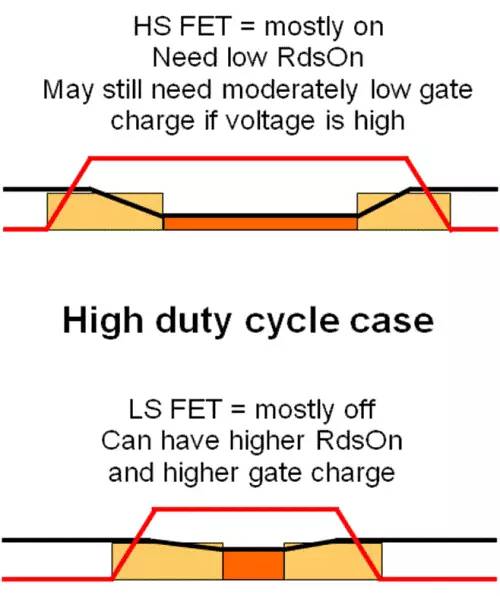

如果我们降低输入电压,则我们可以得到一个高占空比设计,其高侧 FET 大多数时候均为导通状态 ,如图 8 所示。这种情况下,DC 损耗较高,要求低导通电阻。根据不同的输入电压,AC 损耗可能并不像低侧 FET 时那样重要,但还是没有低侧 FET 那样低。因此,仍然要求适当的低栅极电荷。这要求在低导通电阻和低栅极电荷之间做出妥协。就低侧 FET 而言,导通时间最短,且 AC 损耗较低,因此我们可以按照价格或者体积而非导通电阻和栅极电荷原则,选择正确的 FET。

高占空比设计的高侧和低侧 FET 功耗

假设一个负载点 (POL) 稳压器时我们可以规定某个中间电压轨的额定输入电压,那么最佳解决方案是什么呢,是高输入电压/低占空比,还是低输入电压/高占空比呢?使用不同输入电压对占空比进行调制,同时查看 FET功耗情况。

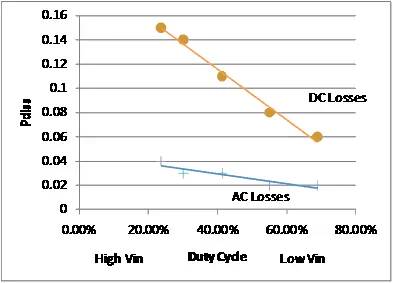

高侧 FET 反应曲线图表明,占空比从 25% 增至 40% 时 AC 损耗明显降低,而DC 损耗却线性增加。因此,35% 左右的占空比,应为选择电容和导通电阻平衡FET的理想值。不断降低输入电压并提高占空比,可以得到最低的AC 损耗和最高的 DC 损耗,就此而言,我们可以使用一个低导通电阻的 FET,并折中选择高栅极电荷。如低侧 FET ,控制器占空比由低升高时 DC 损耗线性降低(低侧 FET 导通时间更短),高控制器占空比时损耗最小。整个电路板的AC 损耗都很低,因此任何情况下都应选择使用低导通电阻的 FET。

高侧FET 损耗与占空比的关系

低侧 FET 损耗与控制器占空比的关系。

请注意:低侧 FET 占空比为 1-控制器占空比,因此低侧 FET 导通时间随控制器占空比增加而缩短

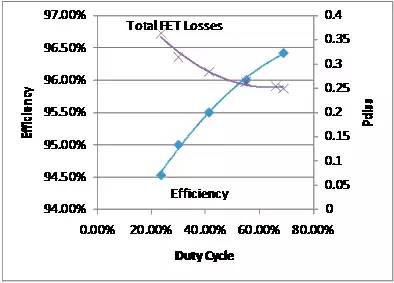

我们将高侧和低侧损耗组合到一起时总效率的变化情况。我们可以看到,这种情况下,高占空比时组合 FET 损耗最低,并且效率最高。效率从 94.5% 升高至 96.5%。不幸的是,为了获得低输入电压,我们必须降低中间电压轨电源的电压,使其占空比增加,原因是它通过一个固定输入电源供电。因此,这样可能会抵消在 POL 获得的部分或者全部增益。另一种方法是不使用中间轨,而是直接从输入电源到 POL 稳压器,目的是降低稳压器数。这时,占空比较低,我们必须小心地选择 FET。

总损耗与效率和占空比的关系

二、电感的损耗

电感功耗阻性损耗

电感功耗包括线圈损耗和磁芯损耗两个基本因素,线圈损耗归结于线圈的直流电阻(DCR),磁芯损耗归结于电感的磁特性。

DCR 定义为以下电阻公式:

式中,ρ 为线圈材料的电阻系数,l 为线圈长度,A 为线圈横截面积。

DCR 将随着线圈长度的增大而增大,随着线圈横截面积的增大而减小。可以利用该原则判断标准电感,确定所要求的不同电感值和尺寸。对一个固定的电感值,电感尺寸较小时,为了保持相同匝数必须减小线圈的横截面积,因此导致DCR 增大;对于给定的电感尺寸,小电感值通常对应于小的DCR,因为较少的线圈数减少了线圈长度,可以使用线径较粗的导线。

已知DCR 和平均电感电流(具体取决于SMPS 拓扑),电感的电阻损耗(PL(DCR))可以用下式估算:

PL(DCR) = IL(AVG)^2× DCR

这里,IL(AVG)是流过电感的平均直流电流。对于降压转换器,平均电感电流是直流输出电流。尽管DCR的大小直接影响电感电阻的功耗,该功耗与电感电流的平方成正比,因此,减小DCR 是必要的。

另外,还需要注意的是:利用电感的平均电流计算PL(DCR) (如上述公式)时,得到的结果略低于实际损耗,因为实际电感电流为三角波。本文前面介绍的MOSFET 传导损耗计算中,利用对电感电流的波形进行积分可以获得更准确的结果。更准确。当然也更复杂的计算公式如下:

PL(DCR) = (IP^3 - IV^3)/3 × DCR

式中IP 和IV 为电感电流波形的峰值和谷值。

磁芯损耗

磁芯损耗并不像传导损耗那样容易估算,很难估测。它由磁滞、涡流损耗组成,直接影响铁芯的交变磁通。SMPS 中,尽管平均直流电流流过电感,由于通过电感的开关电压的变化产生的纹波电流导致磁芯周期性的磁通变化。

磁芯材料对磁芯损耗的影响很大。SMPS 电源中普遍使用的电感是铁粉磁芯,铁镍钼磁粉芯(MPP)的损耗最低,铁粉芯成本最低,但磁芯损耗较大。

磁芯损耗可以通过计算磁芯磁通密度(B)的最大变化量估算,然后查看电感或铁芯制造商提供的磁通密度和磁芯损耗(和频率)图表。峰值磁通密度可以通过几种方式计算,公式可以在电感数据资料中的磁芯损耗曲线中找到。

相应地,如果磁芯面积和线圈数已知,可利用下式估计峰值磁通:

这里,B 是峰值磁通密度(高斯),L 是线圈电感(亨),ΔI 是电感纹波电流峰峰值(安培),A 是磁芯横截面积(cm2),N 是线圈匝数。

磁芯损耗主要由三种构成,磁滞损耗、涡流损耗和剩余损耗。

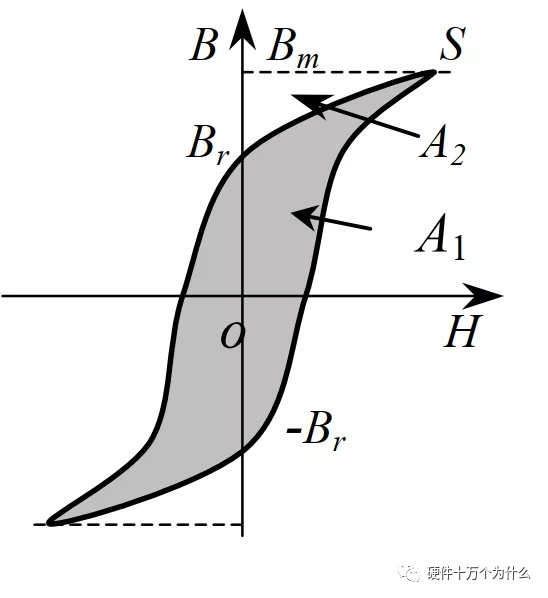

磁滞损耗如何理解呢?

磁滞损耗源于每个交流周期中磁芯偶极子的重新排列所消耗的功率,可以将其看作磁场极性变化时偶极子相互摩擦产生的“摩擦”损耗,正比于频率和磁通密度。

磁芯在外磁场的作用下,材料中的一部分与外磁场方向相差不大的磁畴发生了‘弹性’转动,这就是说当外磁场去掉时,磁畴仍能恢复原来的方向;而另一部分磁畴要克服磁畴壁的摩擦发生刚性转动,即当外磁场去除时,磁畴仍保持磁化方向。因此磁化时,送到磁场的能量包含两部分:前者转为势能,即去掉外磁化电流时,磁场能量可以返回电路;而后者变为克服摩擦使磁芯发热消耗掉,这就是磁滞损耗。

上图为典型的磁滞曲线,从前面磁滞损耗的理解来看。剩磁Br越小,那么磁畴的刚性转动越少,损耗就越小。或者说磁滞损耗正比于磁滞回线包围的面积。

涡流损耗则是磁芯中的时变磁通量引入的。由法拉第定律可知:交变磁通产生交变电压。因此,这个交变电压会产生局部电流,在磁芯电阻上产生I2R 损耗。

如下图,根据电磁感应定律,通电线圈产生磁场B,如果电流是交变的,那么产生的磁场B也是变化的。变化的磁场在磁芯上面产生电场e,并且这个电场是环形电场。因为磁芯材料的电阻率一般不是无限大的,会有一定的电阻值,那么感生出的环形电场会使磁芯中形成环形电流。电流流过电阻,就会发热,产生损耗,这就是涡流损耗。

剩余损耗

剩余损耗的来源,是因为磁芯在磁化过程中,磁化状态并不是随磁化强度的变化立即变化到它的最终状态,而是需要一个过程,需要一定的时间,这便是引起剩余损耗的原因。

剩余损耗是由于磁化弛豫效应或磁性滞后效应引起的损耗。所谓弛豫是指在磁化或反磁化的过程中,磁化状态并不是随磁化强度的变化而立即变化到它的最终状态,而是需要一个过程,这个‘时间效应’便是引起剩余损耗的原因。它主要是在高频1MHz以上一些驰豫损耗和旋磁共振等,在开关电源几百KHz的电力电子场合剩余损耗比例非常低,可以近似忽略。

选择合适的磁芯,要考虑不同的B-H曲线和频率特性,因为B-H曲线决定了电感的高频损耗,饱和曲线及电感量。因为涡流一方面引起电阻损耗,导致磁材料发热,并引起激磁电流加大,另一方面减少磁芯有效导磁面积。所以尽量选择电阻率高的磁性材料或采用碾轧成带料的形式以减少涡流损耗。因此,铂科新材料NPH-L适用于更高频率、高功率器件的低损耗金属粉芯。如图所示:

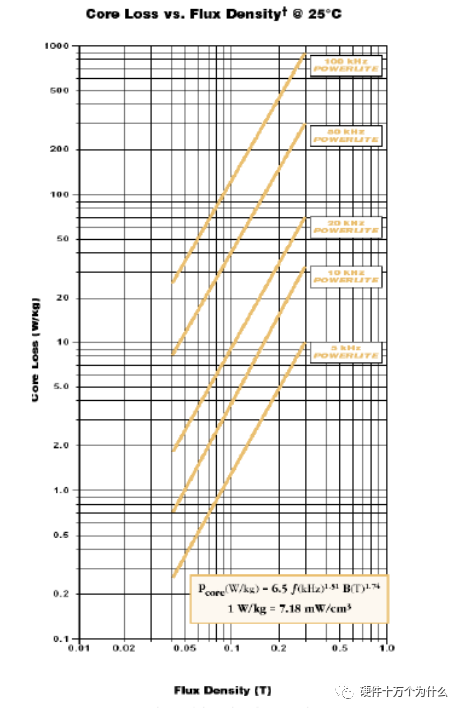

磁芯损耗是磁芯材料内交替磁场引致的结果。某一种材料所产生的损耗,是操作频率与总磁通摆幅(ΔB)的函数,从而降低了有效传导损耗。磁芯损耗是由磁芯材料的磁滞、涡流和剩余损耗引起的。所以,磁芯损耗是磁滞损耗、涡流损耗和剩磁损耗的总和。公式如下:

在一个世纪以前Steinmetz 总结出一个实用于工程计算磁芯损耗的经验公式:

这个公式表明单位体积的损耗Pv 是重复磁化频率和磁通密度的指数函数。Cm ,α 和β 是经验参数,两个指数都可以不为整数,一般的1<α<3 和 2<β<3。对于不同的材质,生产厂家一般会给出其相应的一套参数,但公式和参数仅仅适用于正弦的磁化情况,这是该经验公式应用于开关电源领域的一个主要缺陷。

有些厂家给出的计算公式,主要计算磁滞损耗,剩余损耗和涡流损耗都忽略了。如上图所示:

根据磁芯厂家提供的计算公式计算磁损。

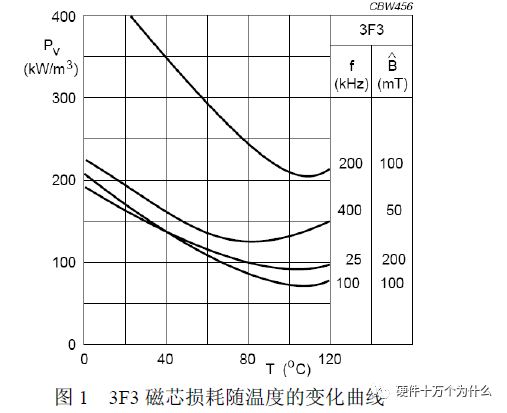

借助 Steinmetz 模型计算磁损在工程上的应用十分广泛,然而该模型的参数随频率变化,也就是说用来反映频率和最大磁感应强度与磁损关系的幂指数α 和β 的拟合值在不同频率时是不同的,同时温度对磁芯损耗的影响也很大。

飞利浦公司的3F3 材料单位体积损耗和温度的关系。既然磁芯损耗随温度的变化而变化,那么计算公式就应该考虑温度的影响。但式(2)中没有明显体现温度影响的参数。为此,一些产商在Steinmetz 经验公式的基础上进行改进,把温度和频率的影响包括在一个更加通用的公式中,比如下式就是飞利浦公司提出的计算正弦波下的单位体积的磁芯损耗公式(W/m3)。

其中:

式(3)中参数Cm、α、β 反映了频率对磁芯损耗的影响。而参数ct0、ct1、ct2,和T 体现了温度的影响,温度的总体影响用参数CT 来表示。表1 为飞利浦公司提供的材料的相应参数。应用式(3)和(4) ,Steinmetz 经验公式(2)可以用来计算正弦波励磁时,不同频率和温度下磁芯材料的单位体积损耗。

表1 飞利浦公司常用磁材料的单位体积损耗(W/m^3)的参数列表

电感磁芯产生损耗的原因: 贴片电感磁芯的损耗主要来源于磁芯损耗和线圈损耗两个方面,而且这两个方面的损耗量的大小又需要根据其不同电路模式来进行判断。其中,磁芯损耗主要是因为磁芯材料内交替磁场而产生的,它所产生的损耗是操作频率与总磁通摆幅(ΔB)的函数,会大大降低了有效传导损耗。线圈损耗则是因为磁性能量变化所造成的能源耗损,它会在当功率电感电流下降时,降低磁场的强度。

电感磁芯降低损耗的方法:

1、电感磁芯中产生的磁芯损耗会随电感磁芯损耗上升而下降的容许铜线损耗,而且还会带来相同的电感磁芯材料通量激增。因此当开关频率上升至 500 kHz 以上,电感磁芯损耗和绕组交流损耗就可以极大地减少电感中的容许直流电流。

2、电感磁芯在线圈中的损耗主要表现在铜线损耗上,因此想要降低铜线损耗,必须要在电感磁芯损耗上升时降低,一直持续到各损耗均相等。最好的情况就是在高频率下损耗稳定保持相等,并允许从磁结构获得最大输出电流。

-

二极管

+关注

关注

147文章

9568浏览量

165803 -

MOSFET

+关注

关注

144文章

7080浏览量

212664 -

buck电路

+关注

关注

27文章

470浏览量

46389

发布评论请先 登录

相关推荐

Buck电路:DCDC电路中的损耗是如何产生的

阐述BUCK电路损耗产生及其估算算法

【原创】同步buck电路讲解

分享一下Buck电路的电感要求

buck电路是什么意思_buck电路简介

开关电源损耗分析 以Buck为例

BUCK型开关电源中的损耗与效率的计算

Buck电路的损耗

Buck电路的损耗

评论