"英诺达EnFortius凝锋低功耗系列EDA软件又新增一款门级功耗分析工具GPA,该工具可以快速精确地计算门级功耗,帮助IC设计师对芯片功耗进行优化。"

(2023年4月25日,四川成都)英诺达(成都)电子科技有限公司发布了自主研发的门级功耗分析工具EnFortius凝锋Gate-level Power Analyzer(GPA),该软件是英诺达继发布低功耗静态验证工具LPC之后的第二款低功耗系列EDA工具,可以快速精确地完成门级功耗分析,帮助工程师更好的完成低功耗设计。

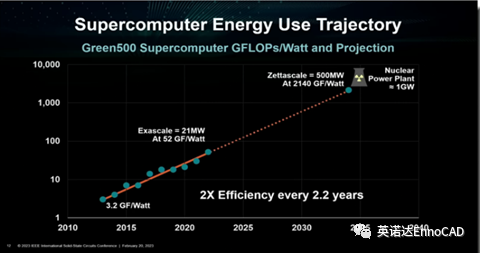

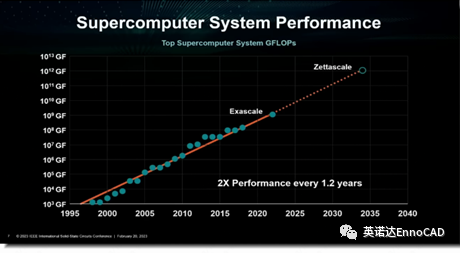

除了性能和面积之外,低功耗长期以来一直是芯片的关键设计要求,而功耗面临的挑战更是与日俱增,甚至成为制约大算力芯片发展的主要瓶颈。AMD的CEO苏姿丰日前在ICCSS 2023上表示“现在要让半导体的算力增加的最大瓶颈,其实不是算力本身而是能耗效率。超级电脑的算力可以每1.2年就翻倍,但是能耗效率的进展却是每2.2年才能够翻倍”。

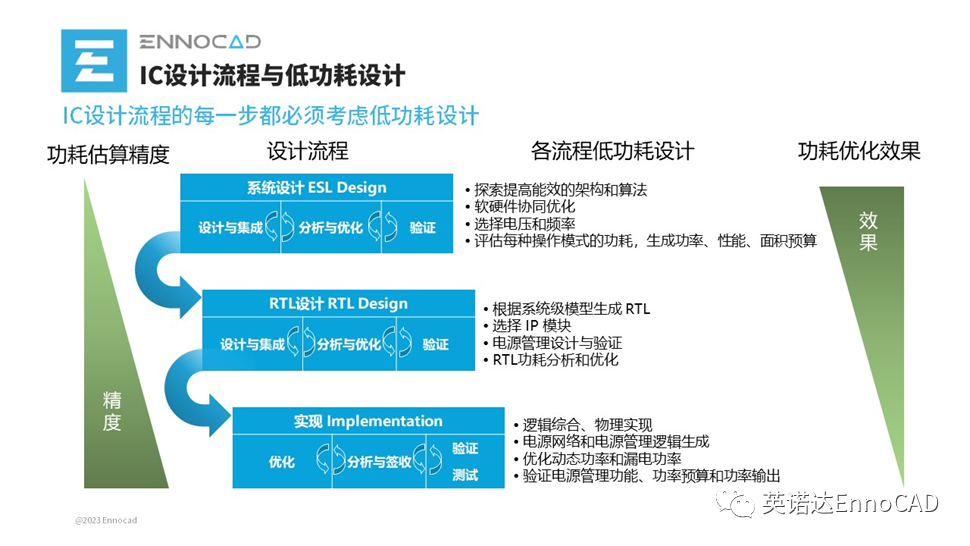

超级计算机性能与能耗效率曲线(Source: ISSCC 2023) 不仅是大算力芯片,低功耗在其他领域也成为重要的指标。清华大学魏少军教授在ICCAD 2022会议上提到,中国的IC设计已经到了不能仅靠采取更新的工艺来提升产品竞争力的阶段,更多的是需要创新的架构、方法学并配合先进的设计工具来满足产品竞争力的需求,而低功耗设计就是其中的一条有效途径。 在芯片设计流程中,各个阶段都必须考虑低功耗设计,而且每个阶段所采取的低功耗策略和使用的工具都略有不同,从整个流程看,越早考虑功耗收益越大,但是估算精度往往不够精确。到了设计流程后期,特别是物理实现之后,功耗的估算会更精确,但此时可采用的功耗优化方法与优化的程度都比较有限。

IC设计流程与低功耗设计

英诺达此次推出的EDA工具GPA是针对门级的功耗分析工具,工具支持工艺库Liberty标准中的各类功耗模型以及信号活动文件标准SAIF中的各类信号活动信息,比如更精确描述有源器件的SDPD(state-dependent-path-dependent)信号活动信息,同时工具内建算法可以完成信号活动率、信号转换时间、时钟信号及特殊常量信号在电路中的传导计算,准确快速地完成网表级的功耗分析。配合工具提供的各类报告、电路搜索及查询功能,可以帮助工程师快速有效地定位电路中可能的功耗热点及分析原因,为后续的功耗优化提供数据及解决办法。

江苏华创微系统有限公司的芯片项目负责人符青表示:“最近,我们率先使用了英诺达的门级功耗分析工具GPA,这款软件可以输入业界标准的设计、网表、SAIF等文件,准确地计算了门级网表的消耗功率,达到了与业内同类产品相当的水平。同时,GPA的运行速度也更快,可以让工程师们及时进行优化调整。作为低功耗设计的一款关键工具,这款软件为团队提供了重要的参考指标,也让我们对英诺达的后续EDA产品报以期待。”

英诺达创始人、CEO王琦博士表示:“功耗是IC设计流程中非常重要的一个考虑指标,针对逻辑综合及物理实现后的网表,英诺达的GPA功耗分析软件可以快速完成电路的静态功耗分析,并针对电路中已有的功耗优化方案做评估,为工程师做进一步功耗优化提供基础。英诺达未来将在该领域持续发力,立足客户需求,提供更多更卓越的低功耗设计相关的EDA工具和解决方案。”

审核编辑 :李倩

-

eda

+关注

关注

71文章

2759浏览量

173308 -

算力芯片

+关注

关注

0文章

47浏览量

4529 -

英诺达

+关注

关注

1文章

31浏览量

1962

原文标题:英诺达再发低功耗EDA工具,将持续在该领域发力

文章出处:【微信号:gh_387c27f737c1,微信公众号:英诺达EnnoCAD】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英诺达发布全新静态验证产品,提升芯片设计效率

英诺达携两款静态验证EDA工具亮相ICCAD-Expo 2024

艾伟达发布数字芯片EDA工具adsDesigner

英诺达受邀参加IIC Shenzhen 2024

英诺达与清华大学携手,共促国产EDA进步

引领智能未来:英锐恩科技的国产低功耗单片机ENMCU

国产网表级功耗分析EDA大幅提升精度与性能

英诺达低功耗设计研讨会圆满结束

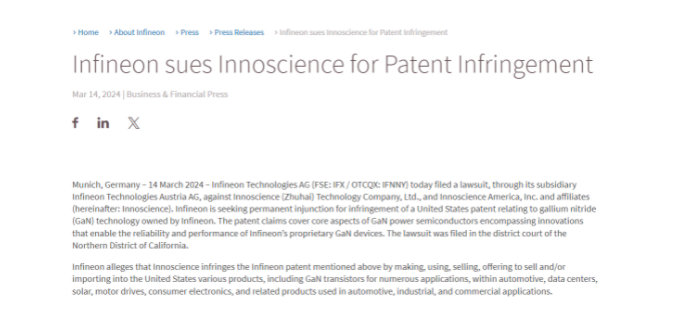

英诺赛科营业收入实现跨越式增长,持续推动技术创新

论述RISC-C在IOT领域的发展机会

英飞凌起诉英诺赛科专利侵权

英诺达再发低功耗EDA工具,将持续在该领域发力

英诺达再发低功耗EDA工具,将持续在该领域发力

评论