eSPU

4月25日-26日,2023移动云大会在苏州金鸡湖国际会议中心隆重举行。中国移动董事长杨杰发表了“云擎未来铸重器 算启新程绘宏图”的主题演讲,“算力网络”成为核心关键词。杨杰董事长提到:“中国移动正在打造以算为中心、网为根基,网云数智安边端链(ABCDNETS)等深度融合、提供一体化服务的算力网络。”并强调将通过汇聚产业合力,共建一流的算网产业生态。

会上,中国移动发布了COCA软硬一体片上计算架构。其中,针对AI大模型时代下高性能计算、存储系统面临的挑战和机遇,计划以COCA为核心打造基于自研可编程DPU SoC、多元异构智能算力、高性能RDMA网络、Diskless存储架构引擎等技术的大模型算力基础设施。

苏州库瀚信息科技有限公司作为移动云云定义存储联合实验室合作伙伴受邀参加本届移动云大会,与移动及众多产业伙伴探讨如何以高能效RISC-V存力+运力方案助力算力网络、大模型算力基础设施落地。

数据中心存力与运力是大算力数字经济的基石,也是低碳经济的重要领域。随着海量实时数据场景的增多,如何降本增效,提高数据中心存储与网络的性能、效率、可靠性和安全性,同时降低其能耗和成本,成为了算力网络落地的核心挑战。

库瀚科技与移动云能力中心在2021年在移动云存储软硬件融合设计领域签署联合研发协议,双方就移动云ESSD高性能存储网络关键组件、云定制硬盘及RISCV高性能低碳存储服务器解决方案等相关领域进行技术开发合作。

在存力方面,库瀚于本次移动云大会首次公开实测了基于全球首款RISC-V架构PCIe 5.0 SSD主控芯片的高性能企业级SSD方案,现场实测硬件性能可达 PCIe 5.0 模式下性能达到顺序读14GB/s,顺序写>10GB/s,PCIe 4.0模式下性能为顺序读7500MB/s、顺序写6900MB/s,随机读1750K IOPS、稳态随机写600K IOPS。两种模式下均突破库瀚Aurora SSD主控芯片发布时的水平,实现业内顶尖的性能水准。

同时,库瀚亦在本次移动云展会中现场展示了基于QLC NAND 和 XL-Flash Gen2两种新型介质的SSD方案,其中XL-Flash Gen2 SSD的延迟现场实测仅为35us。

下一步,库瀚将针对移动云ESSD存储系统的需求,将开展更深度的软硬件融合设计及测试调优,以满足PCIe 5 时代对低延时、高带宽、低功耗的存力需求。

大会现场展示的基于库瀚Aurora的PCIe 5.0/4.0 SSD及相关存储解决方案

在运力方面,自2021年11月起,库瀚科技已助力移动云开展存储网络关键技术模组联合技术攻关,目前相关云盘系统产品已进行商业化部署,形成移动云算力网络存储新能力。

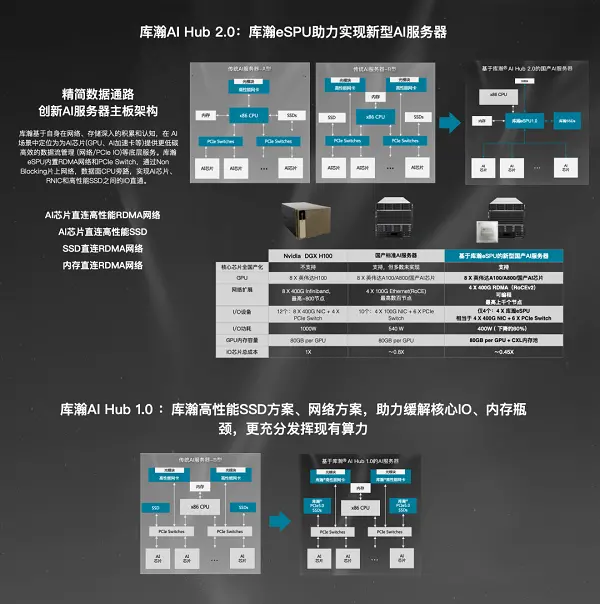

针对AI大模型需求,库瀚科技在本次移动云大会中,亦首次发布了大存力+大运力的系统级底座方案AI Hub™,为云计算、人工智能、媒体渲染、自动驾驶、元宇宙、BTIT等高算力、低时延的IO密集型场景提供底座式服务。

AI Hub™是库瀚科技针对AI场景算力成本与效率痛点的底座式解决方案,基于库瀚eSPU1.0及eSPU0.5芯片为AI算力提供更低碳高效的数据IO优化,以高能效大存力+大运力支撑国产AI芯片更高效产出算力,助力大算力可持续发展。库瀚eSPU1.0将服务器中的智能网卡、PCIe Switch芯片、CPU的数据读写I/O相关功能进行融合,精简数据搬运路径,实现以下优势:

1.优化系统运行效率:通过eSPU芯片实现数据流的智能调度和加速,减少数据在网络和PCIe总线上的拥塞和延迟;

2.降低功耗:通过eSPU芯片实现数据流的硬件卸载和压缩,减少数据在网络和PCIe总线上的传输量,降低系统的能耗和散热需求;

3.降低采购成本和使用成本:通过eSPU芯片实现智能网卡和PCIe Switch芯片的功能集成,减少系统的硬件组件和接口数量,降低系统的复杂度和故障率,节省系统的空间和成本;

库瀚科技与移动云基于双方对数据中心领域的共同愿景和战略目标,旨在利用双方在存力及运力领域的技术优势和场景需求,共同打造基于RISC-V开源架构的高性能低碳存储、网络解决方案,为算力网络等新型场景的落地提供更高效、更可靠、更灵活、更安全的基础设施服务。同时,双方将继续深化合作,共同推动RISC-V架构在智算中心、算力网络等新场景的广泛应用和生态建设,已满足低碳数字经济国家战略技术需求。

审核编辑黄宇

-

SSD

+关注

关注

21文章

2900浏览量

118067 -

数据中心

+关注

关注

16文章

4906浏览量

72502 -

ESPU

+关注

关注

0文章

5浏览量

7113 -

RISC-V

+关注

关注

46文章

2344浏览量

46801 -

库瀚科技

+关注

关注

0文章

6浏览量

89

发布评论请先 登录

相关推荐

直播预约 |开源芯片系列讲座第25期:RISC-V架构在高性能领域的进展与挑战

基于risc-v架构的芯片与linux系统兼容性讨论

《RISC-V能否复制Linux 的成功?》

RISC-V,即将进入应用的爆发期

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

思尔芯亮相RISC-V中国峰会,展示架构建模与混合仿真验证方法

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

北京大学谢涛:基于RISC-V构建AI算力的优势和两种模式

IaaS+on+DPU(IoD)+下一代高性能算力底座技术白皮书

从多核到众核, 赛昉科技RISC-V+NoC IP子系统为算力芯片赋能

risc-v多核芯片在AI方面的应用

DPU技术赋能下一代AI算力基础设施

解锁RISC-V技术力量丨曹英杰:RISC-V与大模型探索

库瀚科技以 RISC-V 架构eSPU助力移动云构建算力网络基础设施“芯”动能

库瀚科技以 RISC-V 架构eSPU助力移动云构建算力网络基础设施“芯”动能

评论