在SpinalHDL中使用之前已有的Verilog等代码的时候需要将这些代码包在一个BlackBox里面,但是如果这些代码里面有时钟和复位,我们需要怎么将时钟和复位端口和SpinalHDL中已有的时钟域连接起来呢?

当BlackBox中只有一个时钟的时候可以直接使用mapClockDomain完成时钟信号和复位信号的赋值。在mapClockDomain中如果没有指定时钟域的话就采用的是默认时钟域。

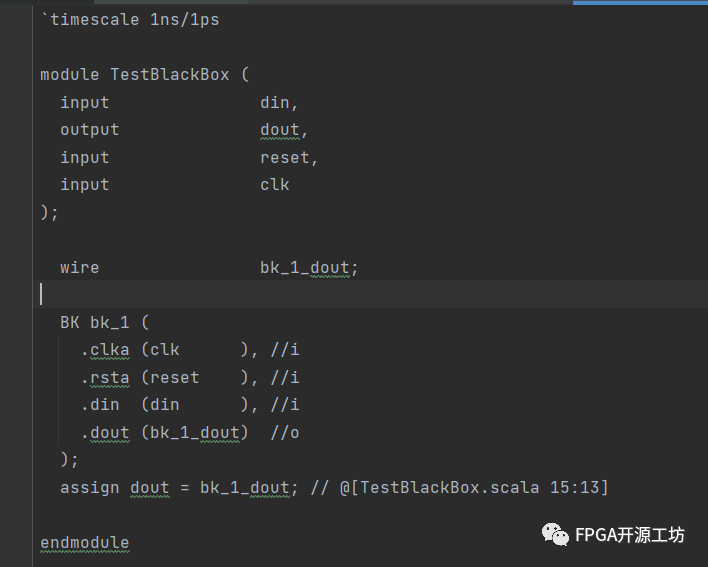

import spinal.core._ import spinal.lib._ class BK extends BlackBox{ val clka = in Bool() val rsta = in Bool() val din = in Bool() val dout = out Bool() mapClockDomain(clock = clka, reset = rsta) } class TestBlackBox extends Component { val din = in Bool() val dout = out Bool() val bk = new BK bk.din <> din bk.dout <> dout } object TestBlackBox extends App{ SpinalVerilog(new TestBlackBox) }

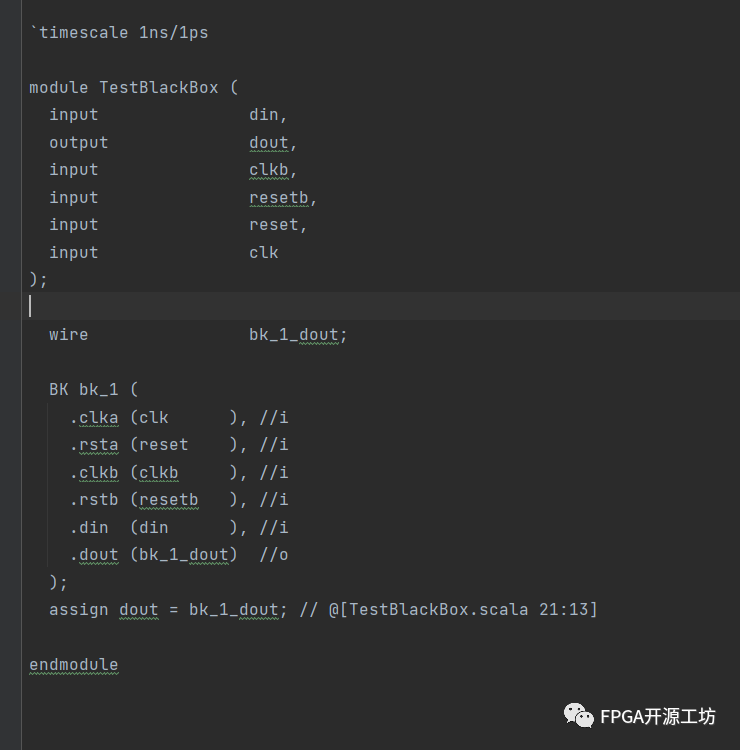

当有两个时钟域的时候,就需要把时钟域给指定一下了,在下面代码中将时钟域通过参数的方式传了进来。

import spinal.core._

import spinal.lib._

class BK(clockDomaina: ClockDomain, clockDomainb: ClockDomain) extends BlackBox{

val clka = in Bool()

val rsta = in Bool()

val clkb = in Bool()

val rstb = in Bool()

val din = in Bool()

val dout = out Bool()

mapClockDomain(clockDomaina,clock = clka, reset = rsta)

mapClockDomain(clockDomainb,clock = clkb, reset = rstb)

}

class TestBlackBox extends Component {

val din = in Bool()

val dout = out Bool()

val clkb = in Bool()

val resetb = in Bool()

val clockDomainb = ClockDomain(clock = clkb,reset = resetb)

val bk = new BK(this.clockDomain,clockDomainb)//默认时钟域和新建的时钟域b

bk.din <> din

bk.dout <> dout

}

object TestBlackBox extends App{

SpinalVerilog(new TestBlackBox)

}

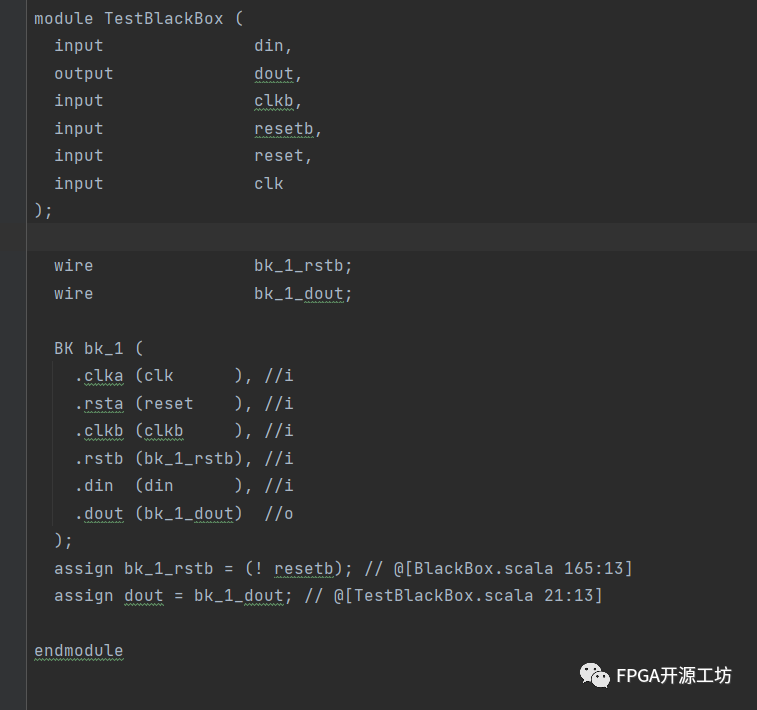

因为在SpinalHDL中默认时钟域是高复位的,但是我们已有的IP可能是低复位的,这个时候就需要在mapClockDomain中指定一下复位信号是HIGH还是LOW。在下面代码中就将时钟域b下面的复位指定为低复位。

import spinal.core._

import spinal.lib._

class BK(clockDomaina: ClockDomain, clockDomainb: ClockDomain) extends BlackBox{

val clka = in Bool()

val rsta = in Bool()

val clkb = in Bool()

val rstb = in Bool()

val din = in Bool()

val dout = out Bool()

mapClockDomain(clockDomaina,clock = clka, reset = rsta)

mapClockDomain(clockDomainb,clock = clkb, reset = rstb, resetActiveLevel = LOW)

}

class TestBlackBox extends Component {

val din = in Bool()

val dout = out Bool()

val clkb = in Bool()

val resetb = in Bool()

val clockDomainb = ClockDomain(clock = clkb,reset = resetb)

val bk = new BK(this.clockDomain,clockDomainb)

bk.din <> din

bk.dout <> dout

}

object TestBlackBox extends App{

SpinalVerilog(new TestBlackBox)

}

以上三种情况应该足够应对一般情况下BlackBox的时钟域的赋值了。

审核编辑:汤梓红

-

Verilog

+关注

关注

28文章

1351浏览量

110091 -

时钟

+关注

关注

10文章

1733浏览量

131473 -

HDL

+关注

关注

8文章

327浏览量

47382 -

复位

+关注

关注

0文章

172浏览量

24215 -

时钟信号

+关注

关注

4文章

448浏览量

28565

原文标题:SpinalHDL BlackBox时钟与复位

文章出处:【微信号:FPGA开源工坊,微信公众号:FPGA开源工坊】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

在SpinalHDL里实现优雅的添加待跟踪波形信号

在SpinalHDL的设计中集成现有RTL设计(IP)的渠道——BlackBox

关于SpinalHDL仿真中信号驱动那点事儿

聊一聊SpinalHDL 1.6.1引入的blackbox inline功能

谈谈SpinalHDL中StreamCCByToggle组件设计不足的地方

如何在SpinalHDL里启动一个仿真

记录一个在使用BlackBox中parameter踩到的坑

SpinalHDL设计错误总结相关资料分享

SpinalHDL里时钟域中的定制与命名

STM32电源管理、复位、时钟

SpinalHDL里用于跨时钟域处理的一些手段方法

原来SpinalHDL中BlackBox封装数组接口如此简单

SpinalHDL BlackBox时钟与复位

SpinalHDL BlackBox时钟与复位

评论