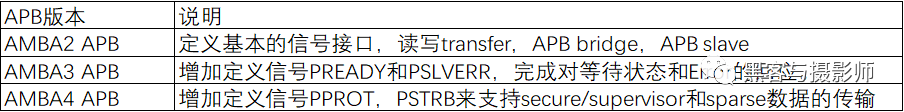

2.5 AXI总线

2.5.1 AXI总线简介

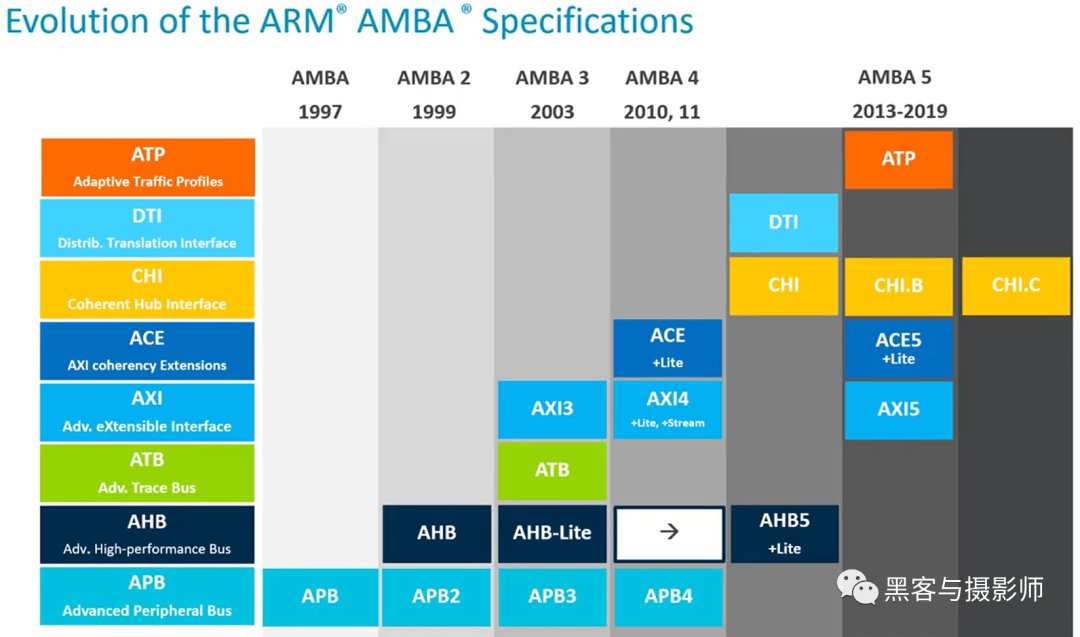

AXI作为AMBA总线协议的一部分,第一次出现在AMBA 3.0中。后面AMBA 4.0发布,AXI4出现了。AXI4总线和别的总线一样,都用来传输bits信息(包含了数据或者地址)。AXI是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易进行时序收敛。

AXI特点是单向通道体系结构,信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

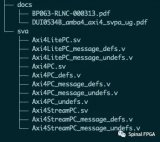

AXI4总线有三种类型,分别是AXI4、AXI4-Lite、AXI4-Stream。AXI4是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解,AXI4-Lite是AXI4的轻量版。这里保留了memory-mapped的写法,主要是为了与AXI4-Stream区分开。

可以这样去理解memory-mapped,假设有master A, 和 slave B,A与B通过AXI4或者AXI4-Lite连接通讯,A可以把B这个外设看作A上的某个地址。当A向B传输数据时,就等同于A向这个地址传输数据。AXI4-Stream与AXI4、AXI4-Lite不同, 它不需要地址通道。

2.5.2 AXI总线读写框架

1)AXI读写传输

AXI4 和 AXI4-Lite接口包含5个不同的通道:两个读通道和三个写通道。每一个AXI传输通道都是单方向的。每一个传输都有地址和控制信息在地址通道(address channel)中,用来描述被传输数据的性质。

- 两个读通道:读地址通道(read address channel)、读数据通道(read data channel)。

- 三个写通道:写地址通道(write address channel)、写数据通道(write data channel)、写响应通道(write response channel)。

对于读操作,主模块通过地址通道发送读传输地址,从模块通过读数据通道返回给主模块所需要的数据。

对于写操作,主模块通过写地址通道发送写传输地址,并通过写数据通道把数据发送给从模块。而从模块接受到数据后,需要通过写响应通道返回一个响应给主模块。

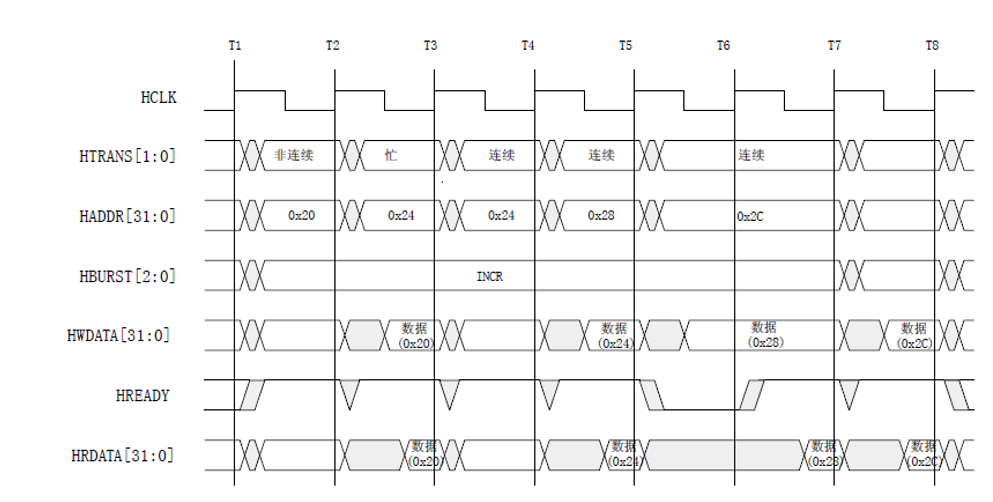

读通道和写通道是分开的,因此可以完成数据的双向传输。此外AXI4能够实现burst传输,换句说就是,可以在一个地址后传输多个数据,最多可以达256 字节。AXI4-Lite不支持burst传输。AXI4-Stream 只有一个通道,不需要地址,可以burst 传输无限的数据。

这5条独立的通道都包含一个信息信号和一个双路的VALD、READY握手机制。信息源通过VALID信号来指示通道中的数据和控制信息什么时候有效。目地源用READY信号来表示何时能够接收数据。读数据和写数据通道都包括一个LAST信号,用来指明一个事物传输的最后一个数据。

读和写传输都有他们自己的地址通道,这地址通道携带着传输所必须的地址和信息。读数据通道传送着从模块到主模块的读数据和读响应信息。读响应信息指明读事务的完成状态。写数据通路传送着主模块向从模块的写数据。每八个数据都会有一个byte lane ,用来指明数据总线上面的哪些byte有效。写响应通道提供了设备响应写传输的一种方式。这完成信号每一次突发式读写会产生一个。

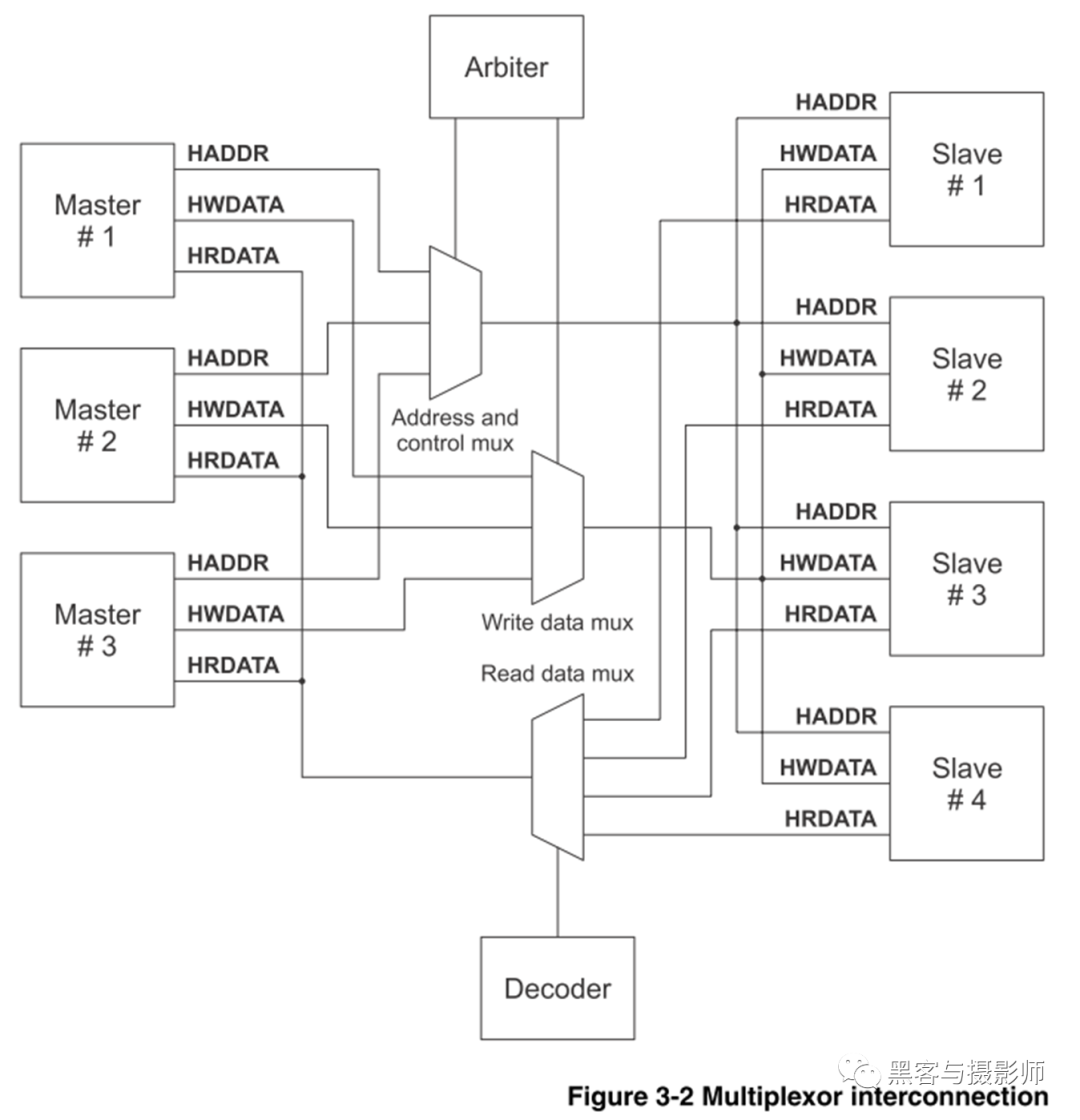

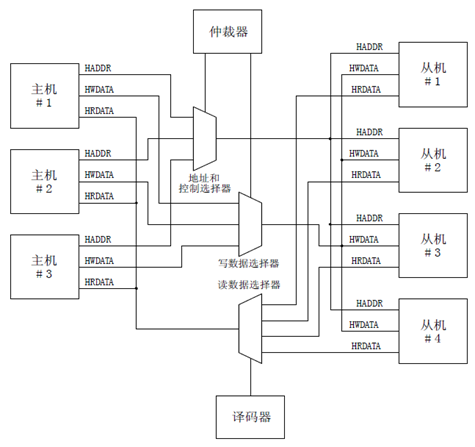

2)AXI典型连接图

上图是一个典型的一系列主设备与一系列从设备的连接系统。这些主设备与从设备通过interconnect连接在一起。

AXI协议提供单一的接口定义,主要包括:

- manager和interconnect之间。

- subordinate和interconnect之间。

- manager和subordinate之间。

AXI协议还提出了一个重要的概念,那就是 Register Slices,因为 上述五个通道之间没有固定的关系,而且通道中传输的信息是单方向的,那么可以可以在任意一个通道中任意节点 插入register slices,通过插入register slice来抵消长路径的延时,从而提高系统的性能。register slice的使用需要平衡 时钟延时和最大工作频率之间的关系。

2.5.2 AXI信号

2.5.3 握手信号

在了解AXI每个通道的定义信号后,下面对读写机制中的握手机制进行说明。

五个独立的通道均使用VALID/READY进行握手,VALID由源端产生,用于指示源端发出的地址、数据、控制信息什么时候生效,READY则由目的端产生,用于指示源端发送信息什么时候被接收,只有当VALID和READY同时为高时,才会表示本次传输完成。

VALID和READY握手可以分为下面三种情况:

- VALID早于READY生效。

- READY早于VALID生效。

- VALID和READY同时生效。

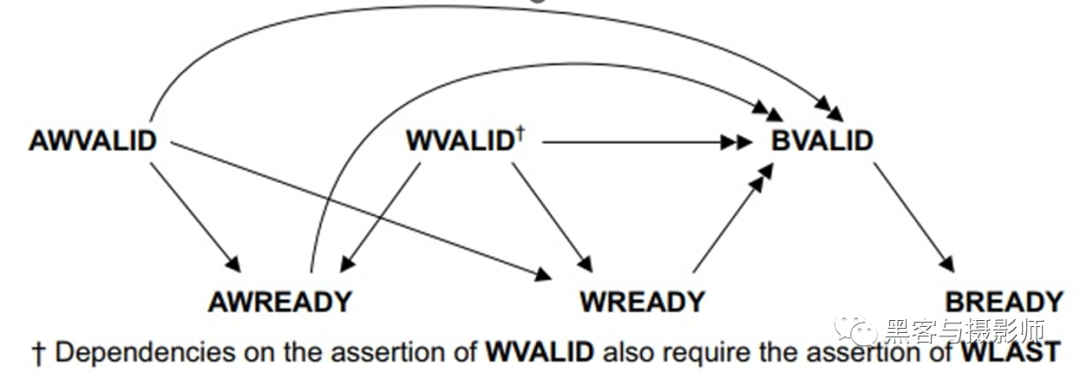

对于五个通道之间的关系,AXI协议仅定义了下面的关系:

- 写响应必须跟随写操作的最后一个传输。

- 读数据必须紧跟读地址数据。

除了上述两点定义,AXI未定义其他任何通道间的关系,那么对于通道间的握手信号先后顺序,必须按照特定的顺序操作,不然很容易引起接口上的dead-lock。

具体的,读操作时,对应的读地址通道和读数据通道间握手信号的解释如下: - ARVALID和ARREADY可以参考握手机制中的时序图所示关系;

- RVALID和RREADY可以参考握手机制中的时序图所示关系;

- RVALID必须在ARVALID和ARREADY同时生效后被使能;

写操作时,对应的写地址通道、写数据通道、写响应通道间的握手信号的解释如下: - AWVALID和AWREADY之间的关系可以参考握手机制中的时序图。

- WVALID和WREADY之间的关系可以参考握手机制中的时序图。

- WVALID和AWREADY之间也可以参考握手机制中的时序图。

- BAVALID和BREADY之间的关系可以参考握手机制中的时序图。

- BVALID必须在WVALID和WREADY同时生效之后再被使能,同时必须是WLAST之后。

上述写操作通道间握手顺序是基于AXI3协议,AXI4/5在AXI3基础上有改进,具体如下:

AXI4/5协议对于BVALID置位条件加强了,同时需要满足WVALID/WREADY和AWVALID/AWREADY生效之后,且是在WLAST之后,才能被使能;

2.5.4 地址结构

AXI协议传输数据时控制信息采用Start_address+Length形式,即Manager发出start_address、length以及burst类型、每次传输的大小等,subordinate需要根据这些信息计算后续的地址,决定返回那些地址对应的数据给manager;那么如何根据manager发送的address、length、burst类型、每个传输的大小这些信息计算出manager需要访问的地址,需要先看一下AXI协议所定义的地址结构;

2.5.5 burst length

AXI协议定义 ARLEN、AWLEN分别表示读操作长度和写操作长度,后面统一使用AxLEN统一表示。

AxLEN的含义:AxLEN+1 个传输(transfer)。

如AxLEN=7,AxSIZE=16byte(后面会讲到),那么本次burst传输的数据量为:8*16=128byte。

AXI3协议定义AxLEN范围:1~16;对应的AxLEN使用4bit表示。

AXI4协议定义AxLEN范围:1~256,对应的AxLEN使用8bit表示。

对于Length还有如下几点限制条件:

- 对于WARP类型的burst,burst length必须为2、4、8或者16。

- burst不能超过4KB地址边界。

- burst不支持提前结束。

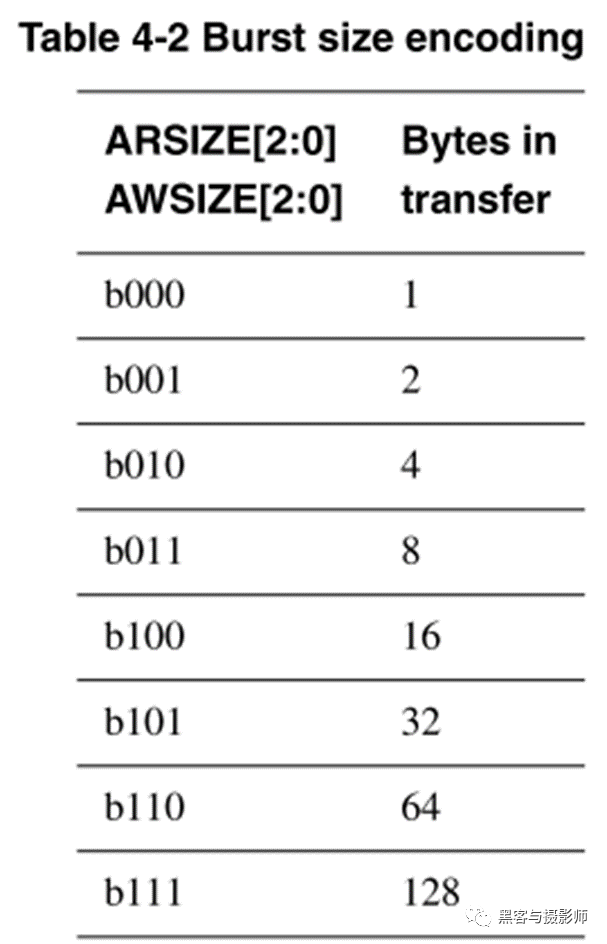

2.5.6 burst size

burst size表示每次传输(transfer)包含多少byte,分别定义了ARSIZE、AWSIZE分别表示读传输、写传输大小。

后面统一使用AxSIZE表示,AxSIZE使用3bit表示,具体的译码方式参见下图:

AxSIZE指定的传输大小不能超过系统工作的数据位宽。

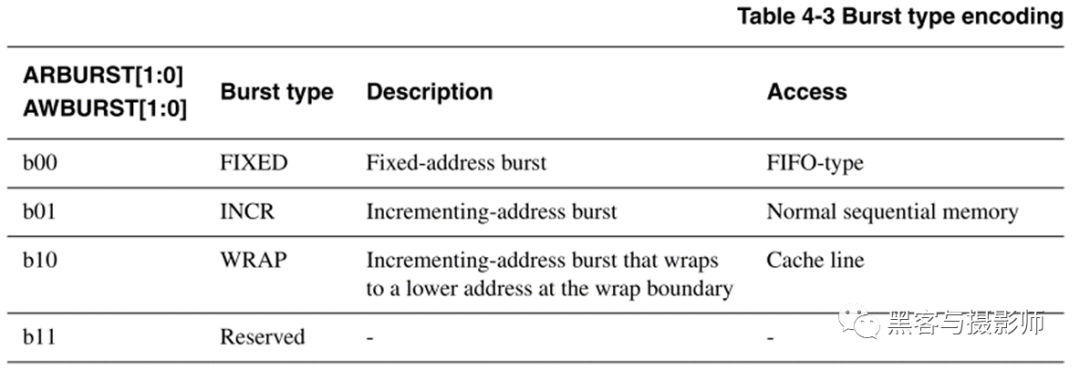

2.5.7 burst type

AXI协议规定下面三种burst类型:

同理,AxBURST为ARBURST和AWBURST的统称,分别表示读操作、写操作burst类型。

- FIXED表示每次传输的地址是相同的地址,常用于对FIFO的访问。

- INCR表示每次地址都是按照递增类型,下次传输的地址=当前传输地址+当前传输的大小。

- WRAP表示每次地址都是按照递增类型,只有在达到地址边界的时候,会卷绕到低位的地址边界开始,这种卷绕方式同AHB协议相同。

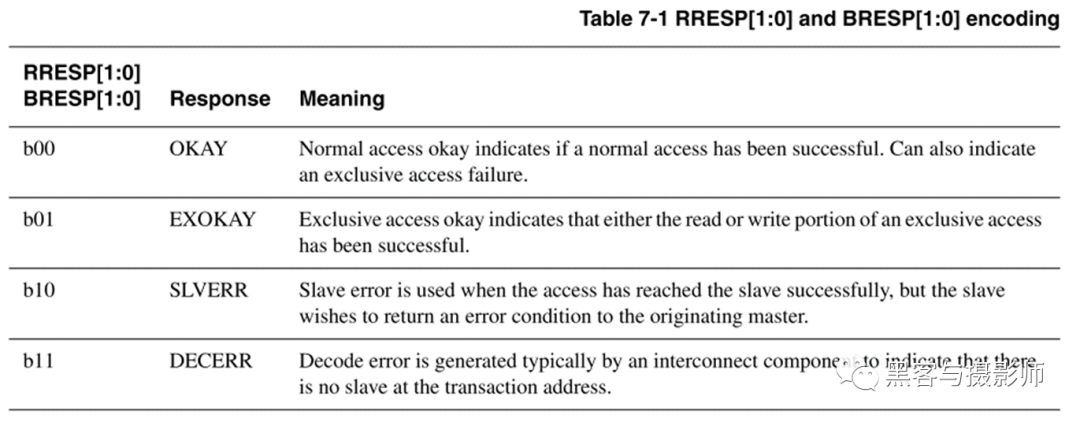

2.5.8 响应类型

上面分析地址结构、数据结构,接下来介绍一下响应类型,BRESP、RRESP分别表示写响应、读响应,后面统一使用xRESP表示,具体的译码规则如下:

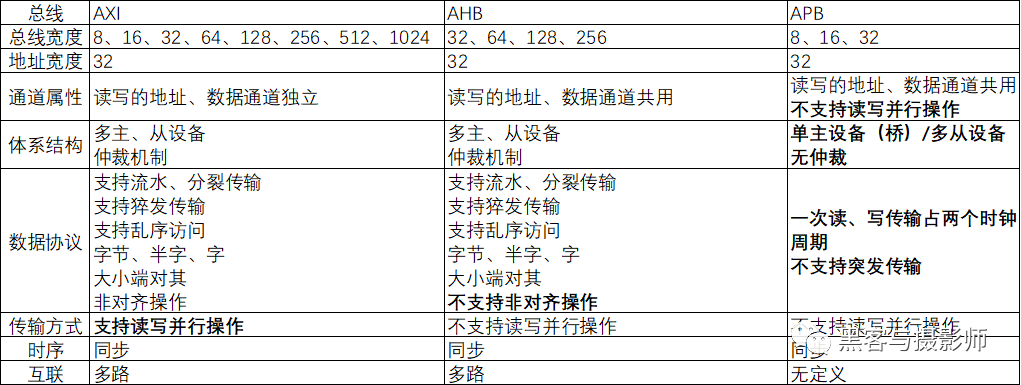

2.6 AXI、AHB、APB总线对比

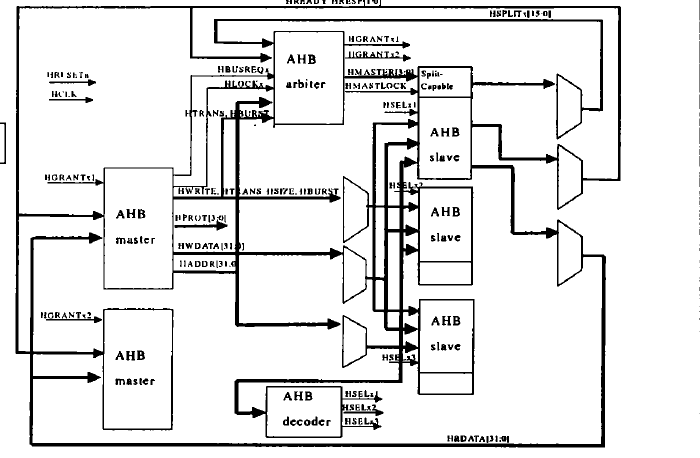

AHB:针对高效率、高频宽及快速系统模块所设计的总线,它可以连接如CPU、芯片上或芯片外的内存模块和DMA等高效率模块。

APB:用在低速且低功耗的外围设备,针对外围设备作功率消耗及复杂接口的优化。APB在AHB和低带宽的外围设备之间提供了通信的桥梁,所以APB是AHB的二级拓展总线。

AXI:高速度、高带宽、管道化互联、单向通道,只需要首地址、读写并行、支持乱序、支持非对齐操作,但连线非常多。

AXI、AHB、APB总线的性能对比分析:

AHB是高级高性能总线,AXI是高级可扩展接口,APB是高级外围总线。AHB和APB都是单通道总线,不支持读写并行。而AXI是多通道总线,总共分为五个通道,能够实现读写并行。AHB和AXI都是多主/从设备,且通过仲裁机制实现总线控制权的分配。而APB是单主设备多从设备,其主设备就是APB桥,不具有仲裁机制。在数据操作方面,AHB和AXI支持突发传输,APB不支持。此外,AXI支持数据的非对齐操作,AHB不支持。

-

ARM

+关注

关注

134文章

9084浏览量

367384 -

总线

+关注

关注

10文章

2878浏览量

88051 -

AMBA

+关注

关注

0文章

68浏览量

14981

发布评论请先 登录

相关推荐

AMBA总线IP核的设计

AMBA总线概述(二)

ARM体系的特点与ARM的技术的简介及AMBA总线的分析

基于AMBA总线介绍

深度解读AMBA、AHB、APB、AXI总线介绍及对比

介绍AMBA2.0总线

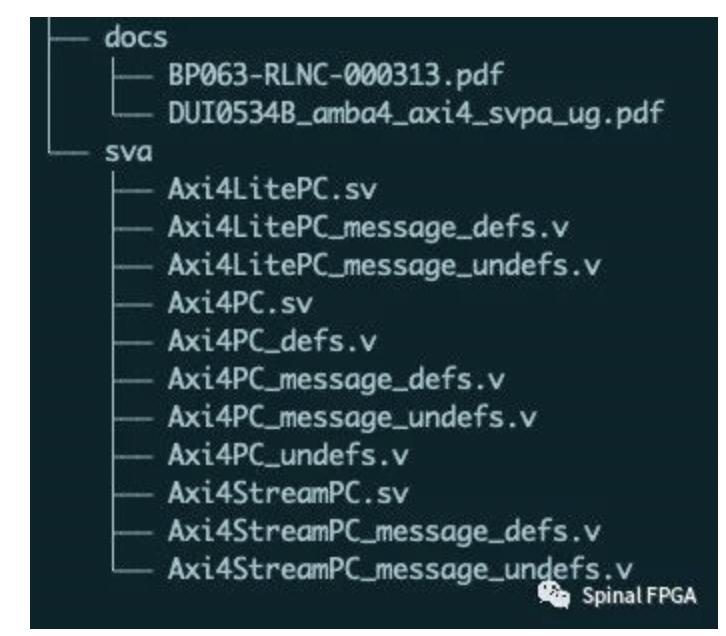

验证必备:AMBA4 SystemVerilog Asseration

深度分析AMBA总线工作原理4

深度分析AMBA总线工作原理4

评论