上小节主要会聚焦在MOS管特性,由MOS管搭建的简单逻辑器件,以及D触发器器件。

本小节将从这些逻辑器件,门电路,触发器开始,搭建一些相对复杂点的功能电路,比如加法器和减法器等。从这个过程中,体会一下如何从基本逻辑门开始,构建功能稍微复杂的电路。

内容概括

加法器的介绍,其内容包括:

二进制加法器

减法器

乘法器

0****1

二进制加法器

01

半加器

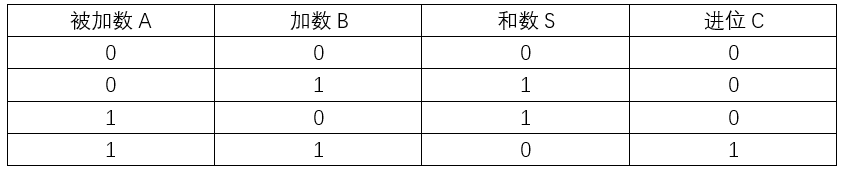

半加器不考虑低位进位来的进位值,只有两个输入,两个输出。由一个与门和异或门构成,

真值表如下:

逻辑表达式 :

02

全加器

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数和,还有一个来自前面低位送来的进位数。这三个数相加,得出本位和数(全加和数)和进位数。这种就是“全加"。

**真值表如下: **

| 被加数A | 加数B | 进位输入Ci | 和数S | 进位输出Co |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

逻辑表达式 :

经过上面的介绍我相信大家对加法器已经有了一定了解,接下来我们为大家介绍如何用与非门等设计一个全加法器。首先我们需要对 公式化简 ,这里就用到了前面介绍的逻辑转换律。

02

减法器

减法器可以由基础的半减器和全减器模块组成,或者基于加法器和控制信号搭建。

定义Nbit被减数x,减数Y,差为D(difference);来自低bit的借位Bi,想高bit借位Bi+1,i为bit序号。

01

半减器

半减器用于计算两bit Xi和Yi的减法,输出结果Di和向高位的借位Bo(Borrow output)。其真值表、逻辑表达式如下:

02

全减法器

全减器不同于半减器在于,全减器输入来自低位的借位Bi(Borrow input),另外两个输入xi、yi,输出为Di和向高位借位Bo。

其真值表、逻辑表达式如下:

接下来我们为大家介绍如何用与非门等设计一个全减法器:

03

乘法器(阵列乘法器)

实现乘法的比较常用的方法是类似与手工计算乘法的方式:

对应的硬件结构就是阵列乘法器(array multiplier)它有三个功能: 产生部分积,累加部分积和最终相加 ,其中HA为半加器,FA为全加器。

-

逻辑器件

+关注

关注

0文章

88浏览量

20098 -

门电路

+关注

关注

7文章

199浏览量

40152 -

触发器

+关注

关注

14文章

2000浏览量

61124

发布评论请先 登录

相关推荐

数字电路基础知识分享4

数字电路基础知识分享4

评论