这一篇来讲一下如何解决上一篇[如何设计一个同步FIFO(二)]最后提出的问题。

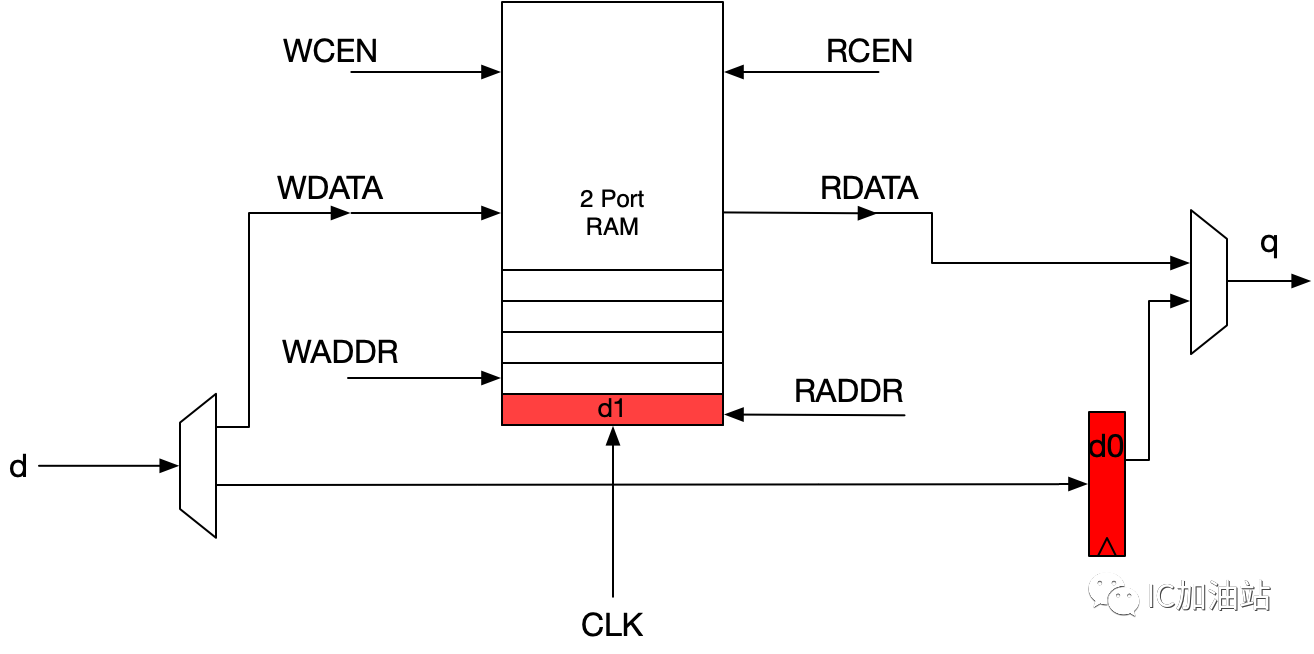

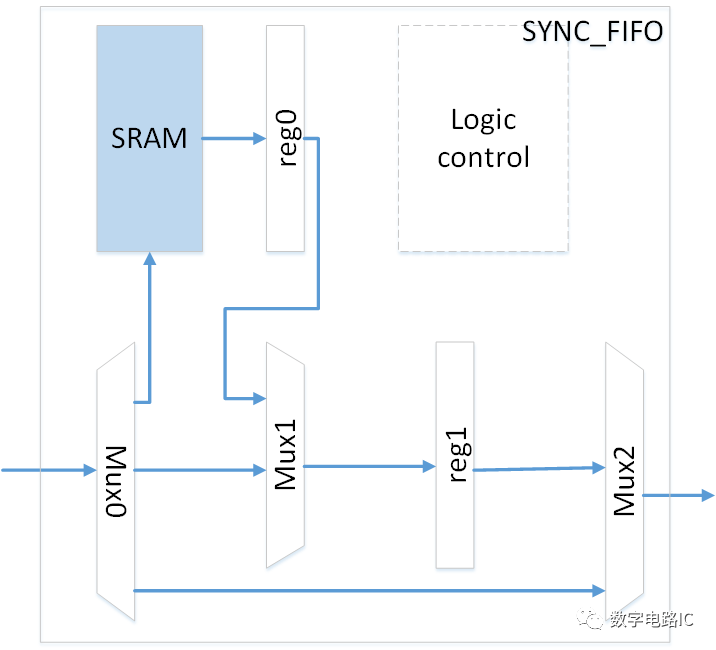

在上一篇中,我们设计的基于双端口SRAM的同步FIFO结构如下,

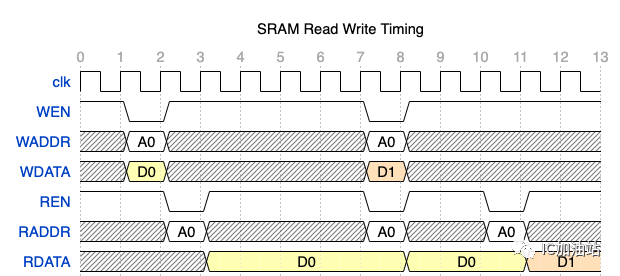

我们说这个结构之所以使得FIFO的输出Q在读完SRAM之后保持稳定,其实需要SRAM本身可以保持RDATA在读操作之后的多个周期保持稳定。即SRAM本身的读时序如下图所示:图中cycle 4,5,6都没有读操作,SRAM的RDATA依然保持D0不变。

但是如果SRAM的读时序不能保证这样,而是只能保证数据RDATA valid一个周期,那么我们就无法使用上面的结构。

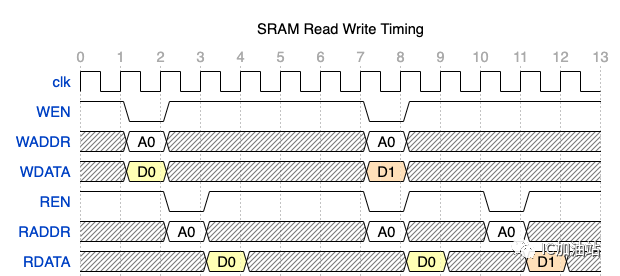

那么要怎么做才能达到我们想要的FIFO时序呢?大家可以很容易想到,如果想保持数据稳定,那还是要借助一级Flop的帮忙,即将SRAM的输出RDATA锁在一个buffer flop里。不过大家也看到,在上一讲里我们下面的结构也还是有问题。

下面老李带领大家整理设计思路。我们看上面的SRAM的时序图,可以发现,我们周期T的时候读一次SRAM,数据在T+1周期到RDATA,我们再把这个数据存到一级flop中,那么要在T+2周期才能在flop的q上看见这个数据。这2个周期是无法避免的。所以说,当我们的FIFO要pop一次,然后下一个周期FIFO的Q数据要切换成最头上的数据(假设这个数据是head),那么我们可以得出结论,我们不能在pop的这一个cycle才去从SRAM中读head,而必须让head在这pop之前已经被读到了flop里,那么当pop来了之后,我们只需要让FIFO的q切换到这个flop输出就可以了。这是设计思路的第一层次。

下面大家再考虑,我们切换到了另一个flop,那么这个时候输出前一个Q的那个flop干什么去呢?当然不能闲着,它的任务是去接受此时存在SRAM里最头上的数据,相当于从SRAM里提前预支了这个数,缓存在这里,这样当下一个pop来的时候,可以在下一个周期再切换到它。

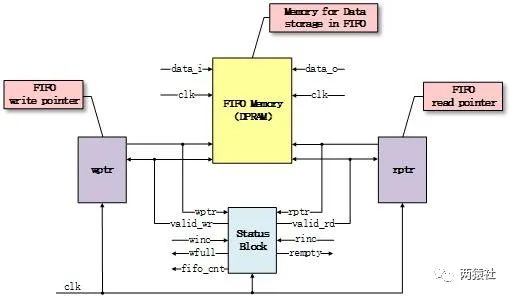

所以大家可以得出一个下面的结构。

要注意的点是我们这里有两级输出buffer flop,在上一讲当中我们说FIFO进来的第一个数不能存到RAM里,而是要直接存到输出级flop去。那么在上面的结构有相应的变化:FIFO进来的前两个数都不能存到RAM里,而是要从第3个数开始才把数据存到RAM里。

时序图建议大家自己画一下。

聪明的同学可能觉得这个思路很眼熟,没错,这里的解决的办法其实是数字电路设计中很常见的一个思路:乒乓Ping-pong buffer。

ping-pong buffer很常用,也是数字电路设计中的一个常考知识点。特别是valid/ready 握手协议中如何插入一级pipestage还能保证传输没有bubble,即每个周期都能够传输数据,老李当年面试被问到不止一次,老李自己做面试官也喜欢问这个问题。其实老李之前是想专门拿出来一篇来讲ping-pong buffer的,不过发现其他很多公众号博主已经写过相应的文章了,老李觉得大家看他们的文章就可以。所以这篇咱们只是简略讲一讲ping-pong buffer在这里的应用。

这里也给另外一个公众号“数字IC自修室”打个广告,上面也有很多很棒的文章,关于ping pong buffer大家可以看这一篇

[芯片设计小经验——乒乓buffer]

-

sram

+关注

关注

6文章

768浏览量

114730 -

fifo

+关注

关注

3文章

389浏览量

43738

发布评论请先 登录

相关推荐

同步FIFO设计详解及代码分享

怎样设计一个同步FIFO?(1)

FIFO设计—同步FIFO

怎样设计一个同步FIFO?(3)

怎样设计一个同步FIFO?(3)

评论