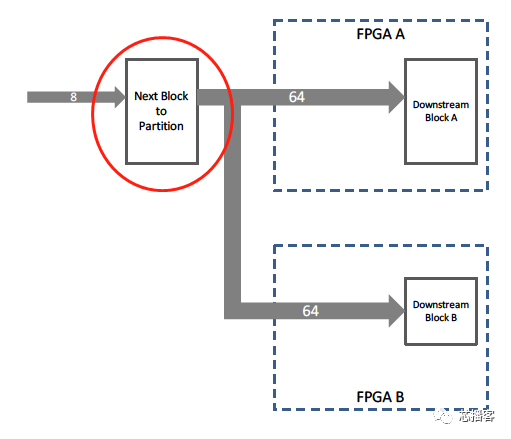

在进行FPGA原型验证的过程中,当要把大型的SoC进行FPGA原型验证时,有时候会遇到一种情况,同样的接口分两组出去到不同的模块,而这两个模块规模较大,又需要分割在两片FPGA中,这时候就会像下图一样:

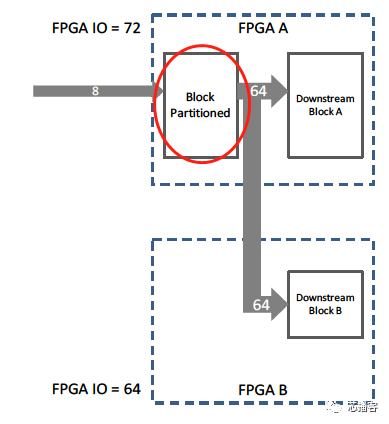

此时,途中画圈的Block到底应该放在FPGA_A中还是FPGA_B中呢?假如放在FPGA_A中,则会增加FPGA_A和FPGA_B的IO资源,如下图所示,FPGA需要64+8=72个IO,而FPGA_B则需要64个IO。这样,对于整个FPGA原型验证系统而言,光这一个功能点,IO资源一共使用了64+72=136个,然而真正的SoC并不仅仅是这一点儿功能,实际上需要更多的IO去连接各个FPGA。

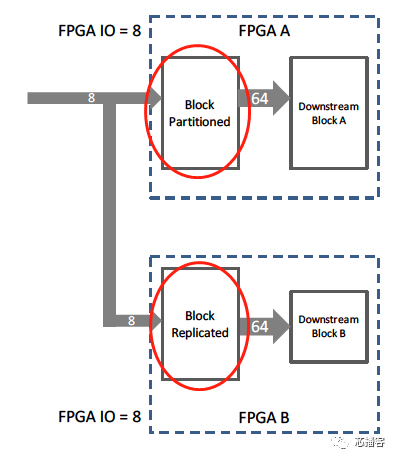

所以,对于原型验证系统,我们推荐采用复制逻辑的办法,以使FPGA原型验证系统在不改变SoC功能的情况下,完成IO的节省,如下图所示,使用的IO数量从64+72下降到8+8、所以FPGA原型验证系统的EDA工具要有分辨那些模块能够在不改变功能的前提下复制到不同的FPGA中,以节省IO。

诚然,节省IO的代价使增加了整个系统的逻辑资源,但这个增加是值得的。复制是一个非常有用的技巧,当我们进行分区时,或者最好是在分区之前,我们应该注意复制机会,以降低IO需求。复制对于在FPGA之间分发芯片支持项目(如时钟和重置)也非常有用。

审核编辑:汤梓红

-

FPGA

+关注

关注

1625文章

21637浏览量

601347 -

芯片

+关注

关注

453文章

50258浏览量

421152 -

接口

+关注

关注

33文章

8462浏览量

150750 -

soc

+关注

关注

38文章

4108浏览量

217802 -

原型验证

+关注

关注

0文章

22浏览量

10721

原文标题:FPGA原型验证系统中复制功能模块的作用

文章出处:【微信号:于博士Jacky,微信公众号:于博士Jacky】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA原型验证系统中复制功能模块的作用

FPGA原型验证系统中复制功能模块的作用

评论